tlm源碼分析——interface class和port_base

uvm官方提供的兩種interface有:uvm_sqr_ifs和uvm_tlm_ifs;

兩種interface都是定義了各個TLM API function的原型;都是單獨的class,並沒有進行extend;

uvm_tlm_if,包含兩個參數化的type定義;

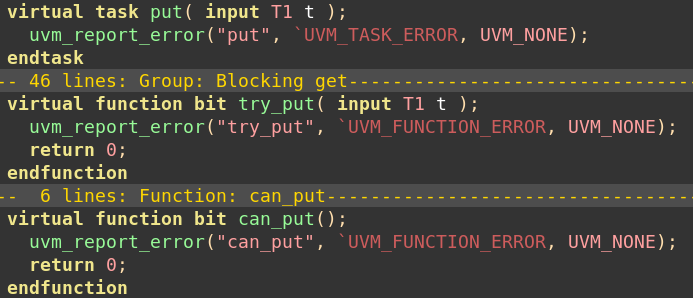

put類函數,一個task,兩個function:

can_put只是返回值,並不會將trans寫出去;

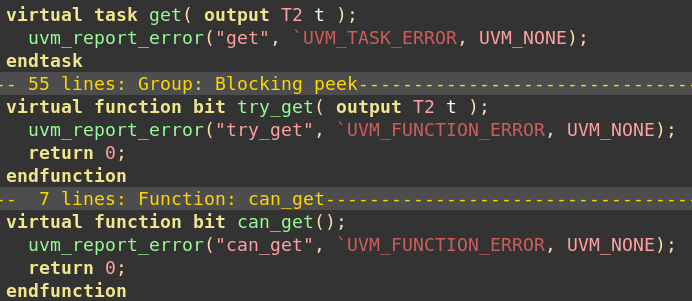

get類函數,一個task,兩個function;

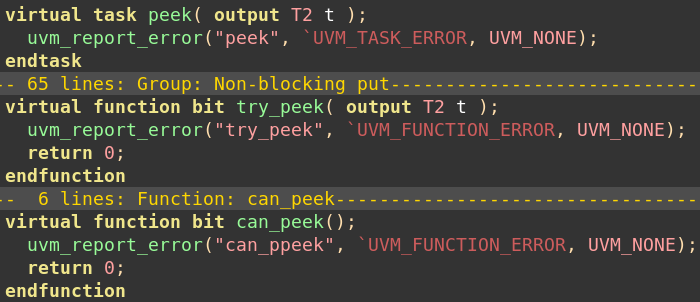

peek類函數,一個task,兩個function;

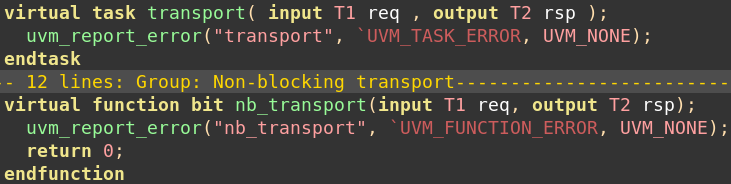

transport類函數,有兩個參數,一個input,一個output;

transport 是一個block的task,nb_transport是一個non block的function;

write類函數,進行broadcast;

![]()

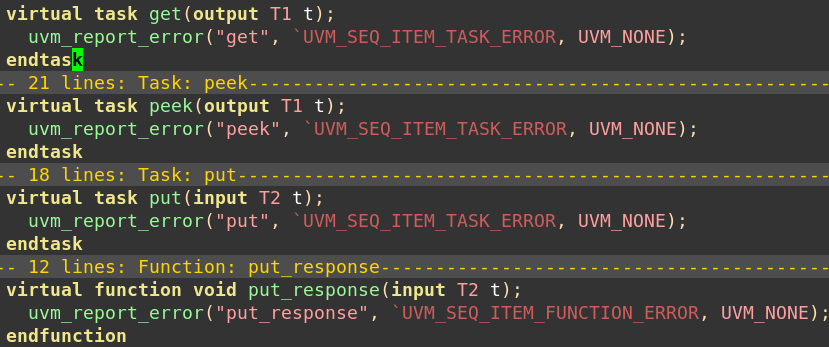

uvm_sqr_if,包含兩個參數化的type定義;主要定義在driver和sequencer之間;進行item和resp的傳遞;

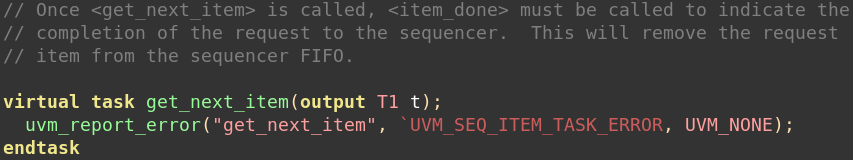

get_next_item。block的peek函數,只有在item_done返回之後,才重新get出fifo中的值;

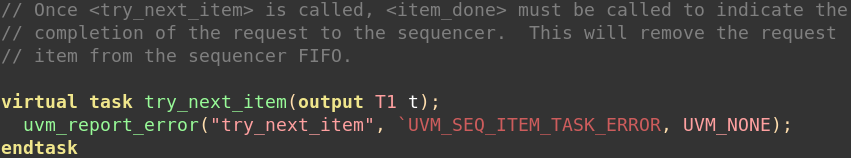

try_next_item,只是try_peek函數,沒有available的情況下,返回null;

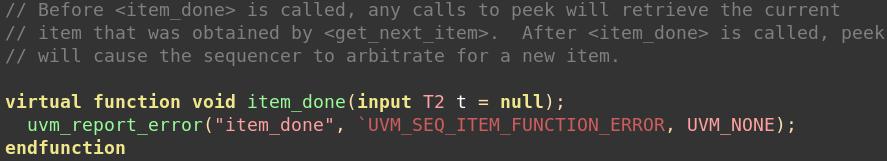

item_done,sequencer收到之後,刪除其中fifo中的值;

sequencer中的兩個function;等待sequence item ready;

純粹tlm的function,不涉及sequencer以及driver之間的item溝通,

兩個item_recording的function;

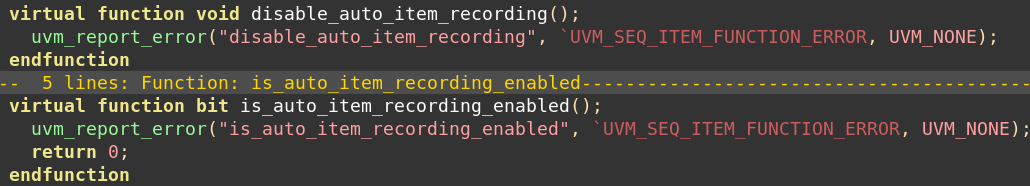

virtual class uvm_port_component_base,定義function原型,從component繼承過來;

繼承類;參數化的類,uvm_port_component,其中的參數化type,為uvm_port_base類型;

主要是為了包含一個該type類型的變量;執行變量中的其他操作;

uvm_port_base,參數化的類,type指tlm_ifs,sqr_ifs;

內部包含一個uvm_port_component #(this_type) m_comp的變量,從而實現comp和port_base的綁定;

內部變量,有一個m_if,主要為了實現具體的ifs的操作,

m_imp_list,保存該port或export連接到的m_imp_list,

m_port_type,表示該port的類型,為extend class使用,

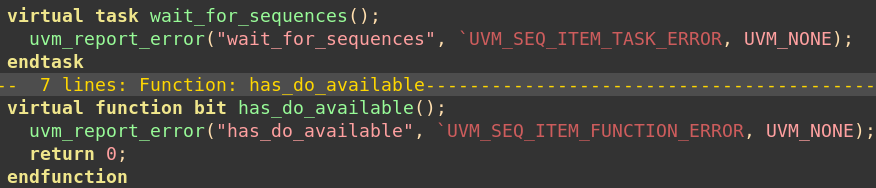

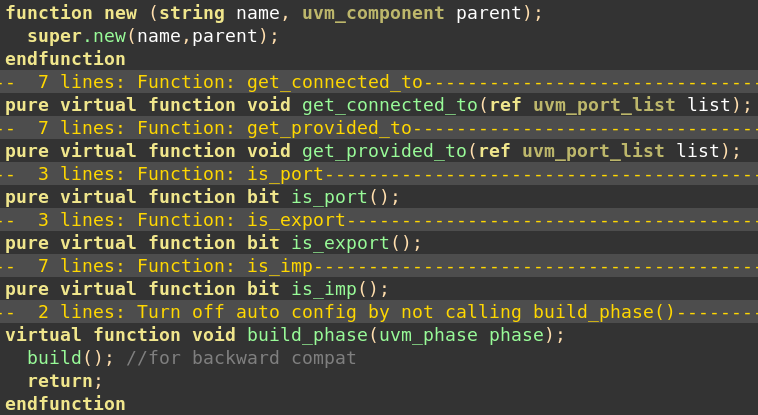

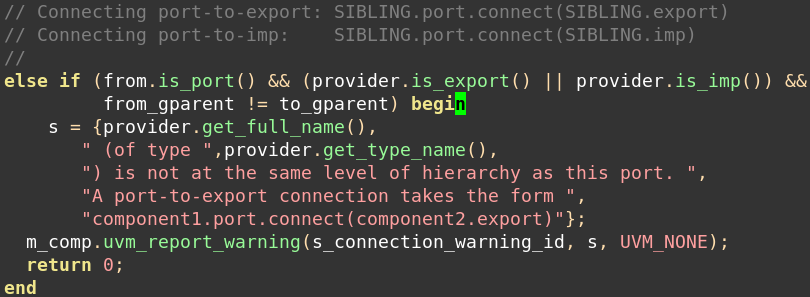

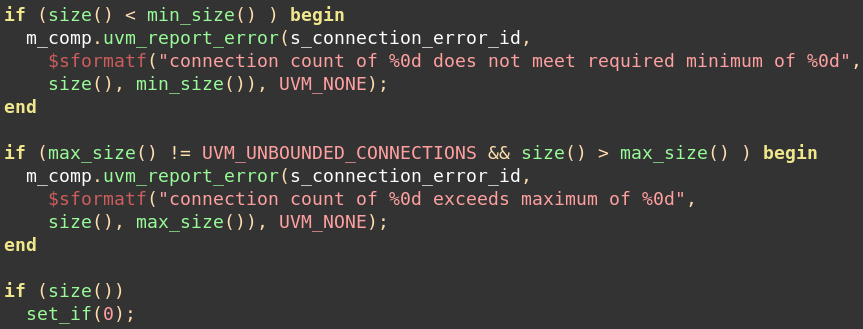

其中最重要的一個function;connect函數;

首先connect這個函數不能再elabration的phase執行;必須在build或者connect phase執行,由於build中執行先後順序的問題

一般放在connect phase;參數名為provider,也就是只有主動的一方才能調用;

![]()

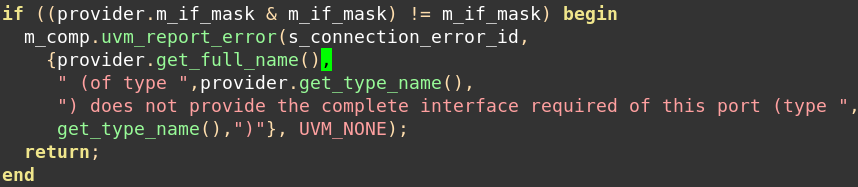

provider為null或this時,也會報error,接著檢查m_If_mask的值是否相同,不同的port在new時,mask都是不同的;

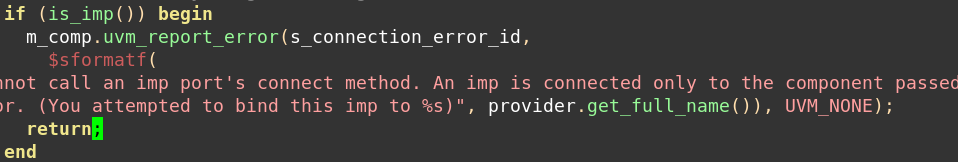

如果調用該方法的對象是imp,直接報錯;imp不允許使用connect;

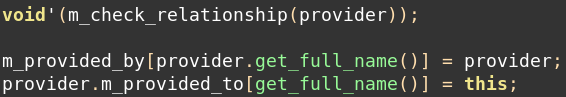

檢查relationship的級聯關系,在將兩個對象中的m_provided_by以及m_provided_to進行初始化;

主要功能只是實現內部provider和provided的賦值;

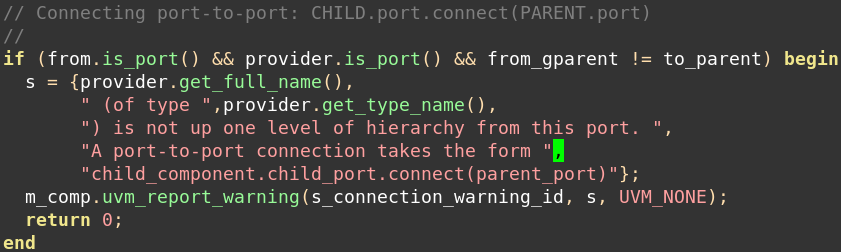

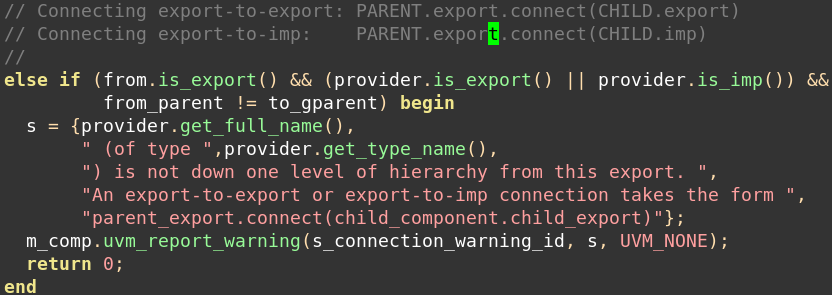

check_relationship的函數,主要檢查port與port的連接,且最開始是一個port;且時child的port連接parent的port;否則報warning;

port連接到export和imp,必須是同一env下的不同comp之間;

export連接到export或者imp,必須是parent到child的;

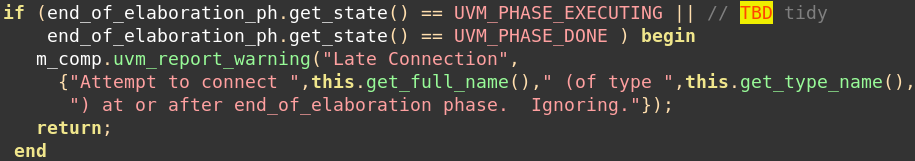

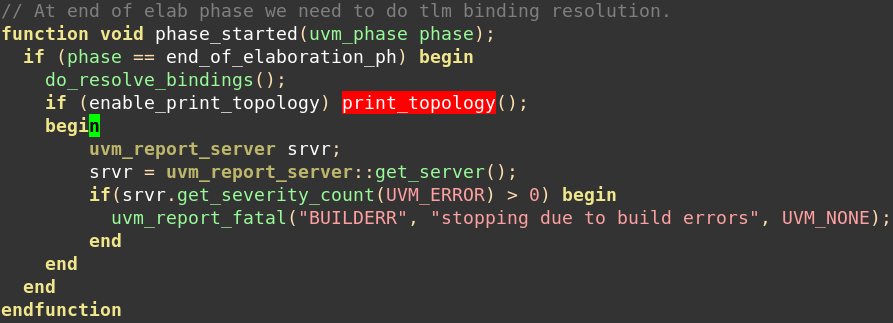

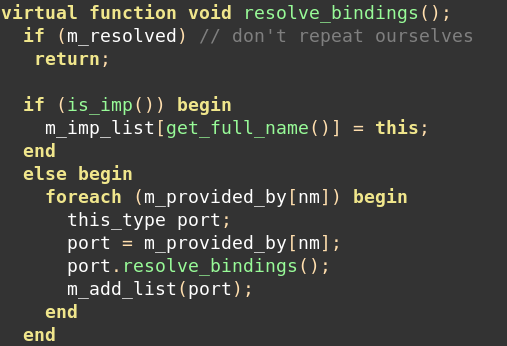

resolve_bindings函數,在end_of_elabration的phase進行自動的遞歸調用,實現imp和port的組裝;

uvm_root從uvm_component繼承而來;重載了phase_started的function,在end_of_elaboration,自動調用

do_resolve_bindings;

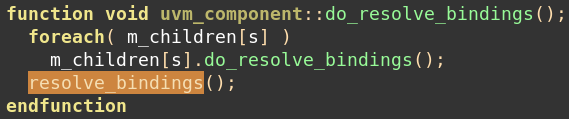

uvm_component中,對child進行遍歷;

port_base中的實現,更新class中的imp_list哈希,如果本身是imp,裏邊只有自己;

否則根據connect函數,賦值的provided_by哈希,在imp_list中添加對象;

m_resolved,防止一個port被反復添加imp;

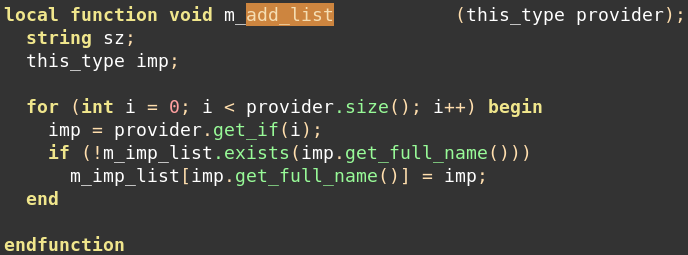

接著判斷imp的個數問題,之後更新內部的m_imp,指向第一個imp_list中的第一個;

m_add_list function,在provider中拿到他的imp_if;所以port,port,export之間可以級聯;指向的imp都是同一個imp;

tlm源碼分析——interface class和port_base