3_認識STM32芯片(1)

我所使用的STM32實驗板芯片類型是STM32F103VBT6,下面詳細介紹這個芯片的資源。

這裏提供這款芯片的中文數據手冊和英文數據手冊:鏈接:http://pan.baidu.com/s/1eR7hW9W 密碼:y6tx

STM32F103VB:使用了高性能的ARM Cortex-M3 32位的RISC內核,工作頻率為72MHZ,內置高速存儲器(128KB的flash,20KB的RAM,CPU能以0等待周期讀寫),豐富的增強I/O端口和連接到兩條APB總線的外設。3個通用定時器,1個高級定時器,7個通信口(2個SPI,2個IIC,3個USART,1個USB,1個CAN),80個通用I/O接口,2個16通道的12位同步ADC。

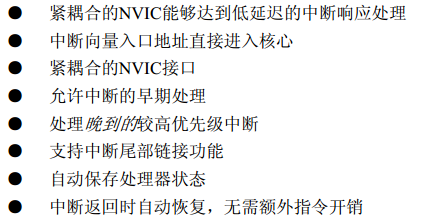

嵌套的向量式中斷控制器(NVIC)

STM32F103XX能處理多達43個可屏蔽中斷通道(不包括16個Cortex-M3的中斷線)和16個優先級

外部中斷/事件控制器(EXTI)

外部中斷/事件控制器包含19個邊沿檢測器,用於產生中斷/事件請求。

每個中斷線都可以獨立地配置它的觸發事件(上升沿,下降沿,雙邊沿),能夠單獨地被屏蔽;有一個掛起寄存器維持所有中斷請求的狀態。

EXTI可以檢測到脈沖寬度小於APB2的時鐘周期。多達80個通用I/O口連接到16個外部中斷線。

時鐘和啟動

系統時鐘的選擇是在啟動時進行,復位時內部8MHZ的RC振蕩器被選為默認的CPU時鐘,隨後可以選擇外部的,具有失效監控的4-16MHZ時鐘;

當外部時鐘失效時,它將被隔離,同時會產生相應的中斷。同樣,在需要時可以采取對PLL時鐘完全的中斷管理(如當一個外接的振蕩器失效時)。

具有多個預分頻器用於配置AHB的頻率,高速APB(APB2)和低速APB(APB1)區域。AHB和高速APB的最高頻率是72MHZ,低速APB的最高頻率為36MHZ。

引導模式

在啟動時,引導管腳被用於選擇三種引導模式中的一種:

從用戶閃存ROM引導

從系統存儲器引導

從SRAM引導

電源供電

VDD=2.0V到3.6V時,VDD管腳提供I/O管腳和內部調壓器的供電。

VSSA,VDDA=2.0-3.6V時,為ADC、復位模塊、RC振蕩器、和PLL的模擬部分提供供電。使用ADC時。VDD不得小於2.4V。

VBAT=1.8-3.6V,當電源開關關閉VDD時,為RTC、外部32Khz振蕩器和後備寄存器供電。

DMA

靈活的7路DMA可以管理存儲器到存儲器、設備到存儲器和存儲器到設備的數據傳輸:DMA控制器支持環形緩沖區的管理,避免了控制器傳輸到達緩沖區結尾時所產生的中斷。

每個通道都有專門的硬件DMA請求邏輯,同時可以由軟件觸發每個通道:傳輸的長度、傳輸的源地址和目標地址都可以通過軟件單獨設置。

DMA可以用於主要的外設:SPI,I2C,USART,通用和高級定時器TIMX和ADC。

RTC和後背寄存器

RTC和後備寄存器通過一個開關來供電,在VDD有效時該開關選擇VDD來供電,否則由VBAT管腳來供電。後備寄存器(10個16位的寄存器)可以用於在VDD消失時保存數據。

3_認識STM32芯片(1)