Verilog中的UDP

概述

Verilog HDL語言提供了一種擴展基元的方法,允許用戶自己定義元件(User Defined Primitives,UDP)。通過UDP,可以把一塊組合邏輯電路或者時序邏輯電路封裝在一個UDP內,並把這個UDP作為一個基本的元件來使用。需要註意的是,UDP不能綜合,只能用於仿真。

UDP的定義與調用

UDP定義的語法和模塊定義類似,但由於UDP和模塊同屬於同級設計,因此,UDP定義不能出現在模塊之內。UDP定義使用由關鍵詞primitive和endprimitive封裝起來的一段代碼,這段代碼定義了該UDP的功能。這種功能的定義是通過表來實現的,即在這段代碼中有一段處於 關鍵詞table和endtable之間的表,用戶可以通過設置該表來規定UDP的功能。

UDP的定義格式如下:

primitive<元件名稱>(<輸出端口名>,<輸入端口名1>,輸入端口名1>...輸入端口名n>);

輸出端口類型聲明(output);

輸入端口類型聲明(input);

輸出端口寄存器 變量說明(reg);

元件初始狀態說明(initial);

table

<table 表項1>;

<table 表項2>;

......

<table 表項n>;

endtable

endprimitive

與Verilog HDL中的模塊相比,UDP具有以下特點:

(1)UDP的輸出端口只能有一個,且必須位於端口列表的第一項。只有輸出端口能定義為REG類型。

(2)UDP的輸入端口可有多個,一般時序電路UDP的輸入端口最多9個,組合電路UDP的輸入端口可多至10個。

(3)所有端口變量的位寬必須是1比特。

(4)在table表項中,只能出現0,1,x這三種狀態,z將被認為是x狀態。

根據UDP包含的基本邏輯功能,可以將UDP分為組合電路UDP、時序電路UDP及混合電路UDP,這幾類UDP的差別主要體現在table表項的描述上。

UDP的調用和verilog HDL中模塊的調用方法相似,通過位置映射。其語法格式如下:

UDP名 例化名(連接端口1信號名,連接端口2信號名,連接端口3信號名,...);

UDP定義的全加器

組合邏輯電路的功能列表類似真值表,規定了不同的輸入值和對應的輸出值,表中每一行的形式是"output ,input1,input2...",排列順序與端口列表中的順序相同。組合電路UDP的輸入端口可多至10個。如果某個輸入,輸出組合沒有定義輸出,那麽就把這種情況的輸出置位x。

3選1多路選擇器

?代表不必關心相應變量的具體值。

UDP原語中可以使用的值

UDP還可以描述具有電平觸發和邊沿觸發特性的時序電路。時序電路擁有內部狀態序列,其內部狀態必須用寄存器變量進行建模,該寄存器的值就是時序電路的的當前狀態,它的下一個狀態是由放在基本功能列表中的狀態轉換表決定的,而且寄存器的下一個狀態就是這個時序電路UDP的輸出值。所以時序電路UDP由兩部分組成——狀態寄存器和狀態列表,定義時序電路UDP的工作也分為兩部分——初始化狀態寄存器和描述狀態列表。

在時序電路的UDP描述中,01、0x、x1代表著信號的上升沿。

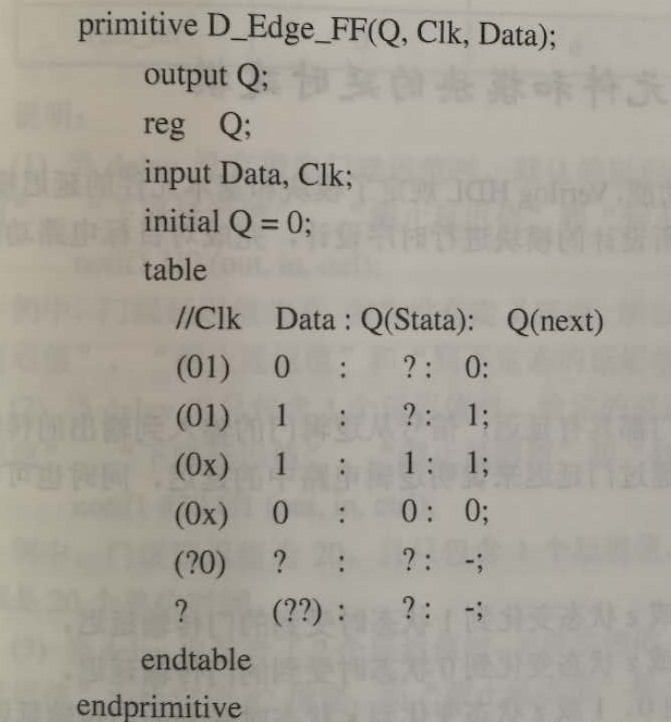

通過verilog hdl語言給出D觸發器的UDP描述

表項(01)表示從0轉換到1,表項(0x)表示從0轉換到x,表項(?0)表示從任意值轉換到0,表項(??)表示任意轉換。對於未定義的轉換,輸出默認為x,假定D_Edge_FF為UDP定義,則它現在就能夠像基本門一樣在模塊中使用。

版權所有權歸卿萃科技 杭州FPGA事業部,轉載請註明出處

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA極客空間 微信公眾號

掃描二維碼關註杭州卿萃科技FPGA極客空間

Verilog中的UDP