[轉] RISC-V架構介紹

1. RISC-V和其他開放架構有何不同

如果僅從“免費”或“開放”這兩點來評判,RISC-V架構並不是第一個做到免費或開放的處理器架構。

在開始之前,我們先通過論述幾個具有代表性的開放架構,來分析RISC-V架構的不同之處以及為什麽其他開放架構沒能取得足夠的成功。

平民英雄——OpenRISC

OpenRISC是OpenCores組織提供的基於GPL協議的開放源代碼RISC處理器。

OpenRISC具有以下特點:

OpenRISC被應用到很多公司的項目之中。可以說,OpenRISC是應用非常廣泛的一種開源處理器實現。

OpenRISC的不足之處在於其側重於實現一種開源的CPU Core,而非立足於定義一種開放的指令集架構,因此其架構的發展不夠完整,指令集的定義也不具備上節中提到的RISC-V架構的優點,更加沒有上升到成立專門的基金會組織的高度。OpenRISC更多的時候被認為是一個開源的Core,而非一種優美的指令集架構。此外,OpenRISC的許可證為GPL,這意味著所有的指令集改動都必須開源(而RISC-V則無此約束)。

豪門顯貴——SPARC

SPARC架構作為經典的RISC微處理器架構之一,SPARC最早於1985年由Sun電腦所設計。SPARC也是SPARC國際公司的註冊商標之一,這家公司於1989年成立,目的是向外界推廣SPARC架構以及為該架構進行兼容性測試。該公司為了推廣SPARC的生態系統,SPARC國際公司將標準開放,並授權予多家生產商采用,包括德州儀器、Cypress半導體和富士通等。由於SPARC架構也對外完全開放,因此,也出現了完全開放源碼的LEON處理器。不僅如此,Sun公司還於1994年推動SPARC v8架構成為IEEE標準(IEEE Standard 1754-1994)。

由於SPARC架構的初衷是面向服務器領域而設計,其最大的特點是擁有一個大型的寄存器窗口,符合SPARC架構的處理器需要實現從72到640個之多的通用寄存器,每個寄存器寬度為64bits,組成一系列的寄存器組,稱之為寄存器窗口。

這種寄存器窗口的架構,由於可以切換不同的寄存器組快速地響應函數調用與返回,因此,能夠產生非常高的性能,但是這種架構由於功耗面積代價太大,而並不適用於PC與嵌入式領域處理器。而SPARC架構也不具備模塊化的特點,使得用戶無法裁剪和選擇。很難作為一種通用的處理器架構對商用的x86和ARM架構形成替代。

設計這種超大服務器CPU芯片又非普通公司與個人所能涉足,而有能力設計這種大型CPU的公司也沒有必要投入巨大的成本來挑戰x86的統治地位。隨著Sun公司的衰弱,SPARC架構現在基本上退出了人們的視野。感興趣的讀者請在網絡上自行搜索文章《再見SPARC處理器,再見Sun》

名校優生——RISC-V

關於RISC-V在伯克利大學誕生的經歷,本節在此不做重復贅述。

因為多年來在CPU領域已經出現過多個免費或開放的架構,很多高校也在科研項目中推出過多種指令集架構。因此,當筆者第一次聽說RISC-V之時,以為又是一個玩具,或純粹學術性質的科研項目而不以為意。

直到筆者親自通讀了一遍RISC-V的架構文檔,不禁為其先進的設計理念所折服。同時,RISC-V架構的各種優點也得到了眾多專業人士的青睞好評和眾多商業公司的相繼加盟。並且2016年RISC-V基金會的正式啟動在業界引起了不小的影響。如此種種,使得RISC-V成為至今為止最具備革命性意義的開放處理器架構。

2. 簡單就是美——RISC-V架構的設計哲學

RISC-V架構作為一種指令集架構,在介紹細節之前,讓我們先了解設計的哲學。所謂設計的“哲學”便是其推崇的一種策略,譬如說我們熟知的日本車的設計哲學是經濟省油,美國車的設計哲學是霸氣外漏等。RISC-V架構的設計哲學是什麽呢?是“大道至簡”。

筆者最為推崇的一種設計原則便是:簡單就是美,簡單便意味著可靠。無數的實際案例已經佐證了“簡單即意味著可靠的”真理,反之越復雜的機器越則越容易出錯。

所謂大道至簡,在IC設計的實際工作中,筆者曾見過最簡潔的設計實現安全可靠,也曾見過最繁復的設計長時間無法穩定收斂。最簡潔的設計往往是最可靠的,在大多數的項目實踐中一次次的得到檢驗。

IC設計的工作性質非常特殊,其最終的產出是芯片,而一款芯片的設計和制造周期均很長,無法像軟件代碼那樣輕易的升級和打補丁,每一次芯片的改版到交付都需要幾個月的周期。不僅如此,芯片的一次制造成本費用高昂,從幾十萬美金到百千萬美金不等。這些特性都決定了IC設計的試錯成本極為高昂,因此能夠有效的降低錯誤的發生就顯得非常的重要。

現代的芯片設計規模越來越大,復雜度越來越高,並不是說要求設計者一味的逃避使用復雜的技術,而是應該將好鋼用在刀刃上,將最復雜的設計用在最為關鍵的場景,在大多數有選擇的情況下,盡量選擇簡潔的實現方案。

筆者在第一次閱讀了RISC-V架構文檔之時,不禁擊節贊嘆,拍案驚奇,因為RISC-V架構在其文檔中不斷地明確強調,其設計哲學是“大道至簡”,力圖通過架構的定義使得硬件的實現足夠簡單。其簡單就是美的哲學,可以從幾個方面容易看出,後續小節將一一加以論述。

無病一身輕——架構的篇幅

在處理器領域,目前主流的架構為x86與ARM架構,筆者曾經參與設計ARM架構的應用處理器,因此需要閱讀ARM的架構文檔,如果對其熟悉的讀者應該了解其篇幅。經過幾十年的發展,現代的x86與ARM架構的架構文檔長達幾百數千頁。打印出來能有半個桌子高,可真是“著作等身”。

之所以現代x86與ARM架構的文檔長達數千頁,且版本眾多,一個主要的原因是因為其架構的發展的過程也伴隨了現代處理器架構技術的不斷發展成熟。

並且作為商用的架構,為了能夠保持架構的向後兼容性,其不得不保留許多過時的定義,或者在定義新的架構部分時為了能夠將就已經存在的技術部分而顯得非常的別扭。久而久之就變得極為冗長。

那麽現代成熟的架構是否能夠選擇重新開始,重新定義一個簡潔的架構呢,可以說是幾乎不可能。其中一個重要的原因便是其無法向前兼容,從而無法得到用戶的接受。試想一下如果我們買了一款新的搭配新的處理器的電腦或者手機回家,之前所有的軟件都無法運行而變磚,那肯定是無法讓人接受的。

而現在才推出的RISC-V架構,則具備了後發優勢,由於計算機體系結構經過多年的發展已經成為比較成熟的技術,多年來在不斷成熟的過程中暴露的問題都已經被研究透徹,因此新的RISC-V架構能夠加以規避,並且沒有背負向後兼容的歷史包袱,可以說是無病一身輕。

目前的“RISC-V架構文檔”分為“指令集文檔”(riscv-spec-v2.2.pdf)和“特權架構文檔”(riscv-privileged-v1.10.pdf)。“指令集文檔”的篇幅為145頁,而“特權架構文檔”的篇幅也僅為91頁。熟悉體系結構的工程師僅需一至兩天便可將其通讀,雖然“RISC-V的架構文檔”還在不斷地豐富,但是相比“x86的架構文檔”與“ARM的架構文檔”,RISC-V的篇幅可以說是極其短小精悍。

感興趣的讀者可以在RISC-V基金會的網站上(https://riscv.org/specifications/)無需註冊便可免費下載其文檔,如圖1所示。

圖1 RISC-V基金會網站上的架構文檔

能屈能伸——模塊化的指令集

RISC-V架構相比其他成熟的商業架構的最大一個不同還在於它是一個模塊化的架構。因此,RISC-V架構不僅短小精悍,而且其不同的部分還能以模塊化的方式組織在一起,從而試圖通過一套統一的架構滿足各種不同的應用。

這種模塊化是x86與ARM架構所不具備的。以ARM的架構為例,ARM的架構分為A、R和M三個系列,分別針對於Application(應用操作系統)、Real-Time(實時)和Embedded(嵌入式)三個領域,彼此之間並不兼容。

但是模塊化的RISC-V架構能夠使得用戶能夠靈活選擇不同的模塊組合,以滿足不同的應用場景,可以說是“老少鹹宜”。譬如針對於小面積低功耗嵌入式場景,用戶可以選擇RV32IC組合的指令集,僅使用Machine Mode(機器模式);而高性能應用操作系統場景則可以選擇譬如RV32IMFDC的指令集,使用Machine Mode(機器模式)與User Mode(用戶模式)兩種模式。而他們共同的部分則可以相互兼容。

濃縮的都是精華——指令的數量

短小精悍的架構以及模塊化的哲學,使得RISC-V架構的指令數目非常的簡潔。基本的RISC-V指令數目僅有40多條,加上其他的模塊化擴展指令總共幾十條指令。

3. RISC-V指令集架構簡介

本章將對RISC-V的指令集架構多方面的特性進行簡要介紹。

模塊化的指令子集

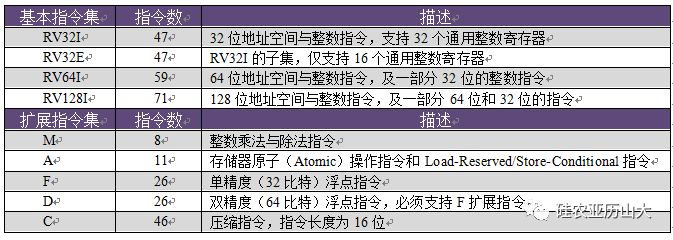

RISC-V的指令集使用模塊化的方式進行組織,每一個模塊使用一個英文字母來表示。RISC-V最基本也是唯一強制要求實現的指令集部分是由I字母表示的基本整數指令子集,使用該整數指令子集,便能夠實現完整的軟件編譯器。其他的指令子集部分均為可選的模塊,具有代表性的模塊包括M/A/F/D/C,如表1所示。

表1 RISC-V的模塊化指令集

為了提高代碼密度,RISC-V架構也提供可選的“壓縮”指令子集,由英文字母C表示。壓縮指令的指令編碼長度為16比特,而普通的非壓縮指令的長度為32比特。以上這些模塊的一個特定組合“IMAFD”,也被稱為“通用”組合,由英文字母G表示。因此RV32G表示RV32IMAFD,同理RV64G表示RV64IMAFD。

為了進一步減少面積,RISC-V架構還提供一種“嵌入式”架構,由英文字母E表示。該架構主要用於追求極低面積與功耗的深嵌入式場景。該架構僅需要支持16個通用整數寄存器,而非嵌入式的普通架構則需要支持32個通用整數寄存器。

通過以上的模塊化指令集,能夠選擇不同的組合來滿足不同的應用。譬如,追求小面積低功耗的嵌入式場景可以選擇使用RV32EC架構;而大型的64位架構則可以選擇RV64G。

除了上述的模塊,還有若幹的模塊包括L、B、P、V和T等。這些擴展目前大多數還在不斷完善和定義中,尚未最終確定,因此本文在此不做詳細論述。

可配置的通用寄存器組

RISC-V架構支持32位或者64位的架構,32位架構由RV32表示,其每個通用寄存器的寬度為32比特;64位架構由RV64表示,其每個通用寄存器的寬度為64比特。

RISC-V架構的整數通用寄存器組,包含32個(I架構)或者16個(E架構)通用整數寄存器,其中整數寄存器0被預留為常數0,其他的31個(I架構)或者15個(E架構)為普通的通用整數寄存器。

如果使用了浮點模塊(F或者D),則需要另外一個獨立的浮點寄存器組,包含32個通用浮點寄存器。如果僅使用F模塊的浮點指令子集,則每個通用浮點寄存器的寬度為32比特;如果使用了D模塊的浮點指令子集,則每個通用浮點寄存器的寬度為64比特。

規整的指令編碼

在流水線中能夠盡早盡快的讀取通用寄存器組,往往是處理器流水線設計的期望之一,這樣可以提高處理器性能和優化時序。這個看似簡單的道理在很多現存的商用RISC架構中都難以實現,因為經過多年反復修改不斷添加新指令後,其指令編碼中的寄存器索引位置變得非常的淩亂,給譯碼器造成了負擔。

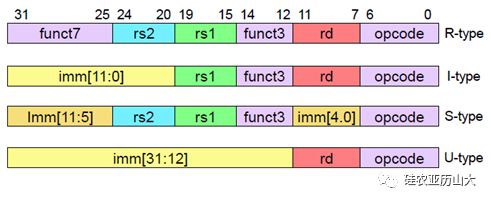

得益於後發優勢和總結了多年來處理器發展的教訓,RISC-V的指令集編碼非常的規整,指令所需的通用寄存器的索引(Index)都被放在固定的位置,如圖2所示。因此指令譯碼器(Instruction Decoder)可以非常便捷的譯碼出寄存器索引然後讀取通用寄存器組(Register File,Regfile)。

圖2 RV32I規整的指令編碼格式

簡潔的存儲器訪問指令

與所有的RISC處理器架構一樣,RISC-V架構使用專用的存儲器讀(Load)指令和存儲器寫(Store)指令訪問存儲器(Memory),其他的普通指令無法訪問存儲器,這種架構是RISC架構的常用的一個基本策略,這種策略使得處理器核的硬件設計變得簡單。

存儲器訪問的基本單位是字節(Byte)。RISC-V的存儲器讀和存儲器寫指令支持一個字節(8位),半字(16位),單字(32位)為單位的存儲器讀寫操作,如果是64位架構還可以支持一個雙字(64位)為單位的存儲器讀寫操作。

RISC-V架構的存儲器訪問指令還有如下顯著特點:

為了提高存儲器讀寫的性能,RISC-V架構推薦使用地址對齊的存儲器讀寫操作,但是地址非對齊的存儲器操作RISC-V架構也支持,處理器可以選擇用硬件來支持,也可以選擇用軟件來支持。

由於現在的主流應用是小端格式(Little-Endian),RISC-V架構僅支持小端格式。有關小端格式和大端格式的定義和區別,本文在此不做過多介紹,若對此不甚了解的初學者可以自行查閱學習。

很多的RISC處理器都支持地址自增或者自減模式,這種自增或者自減的模式雖然能夠提高處理器訪問連續存儲器地址區間的性能,但是也增加了設計處理器的難度。RISC-V架構的存儲器讀和存儲器寫指令不支持地址自增自減的模式。

RISC-V架構采用松散存儲器模型(Relaxed Memory Model),松散存儲器模型對於訪問不同地址的存儲器讀寫指令的執行順序不作要求,除非使用明確的存儲器屏障(Fence)指令加以屏蔽。

這些選擇都清楚地反映了RISC-V架構力圖簡化基本指令集,從而簡化硬件設計的哲學。RISC-V架構如此定義非常合理,能夠達到能屈能伸的效果。譬如:對於低功耗的簡單CPU,可以使用非常簡單的硬件電路即可完成設計;而對於追求高性能的超標量處理器則可以通過復雜設計的動態硬件調度能力來提高性能。

高效的分支跳轉指令

RISC-V架構有兩條無條件跳轉指令(Unconditional Jump),jal與jalr指令。跳轉鏈接(Jump and Link)指令jal可用於進行子程序調用,同時將子程序返回地址存在鏈接寄存器(Link Register:由某一個通用整數寄存器擔任)中。跳轉鏈接寄存器(Jump and Link-Register)指令jalr指令能夠用於子程序返回指令,通過將jal指令(跳轉進入子程序)保存的鏈接寄存器用於jalr指令的基地址寄存器,則可以從子程序返回。

RISC-V架構有6條帶條件跳轉指令(Conditional Branch),這種帶條件的跳轉指令跟普通的運算指令一樣直接使用2個整數操作數,然後對其進行比較,如果比較的條件滿足時,則進行跳轉。因此,此類指令將比較與跳轉兩個操作放到了一條指令裏完成。

作為比較,很多的其他RISC架構的處理器需要使用兩條獨立的指令。第一條指令先使用比較指令,比較的結果被保存到狀態寄存器之中;第二條指令使用跳轉指令,判斷前一條指令保存在狀態寄存器當中的比較結果為真時則進行跳轉。相比而言RISC-V的這種帶條件跳轉指令不僅減少了指令的條數,同時硬件設計上更加簡單。

對於沒有配備硬件分支預測器的低端CPU,為了保證其性能,RISC-V的架構明確要求其采用默認的靜態分支預測機制,即:如果是向後跳轉的條件跳轉指令,則預測為“跳”;如果是向前跳轉的條件跳轉指令,則預測為“不跳”,並且RISC-V架構要求編譯器也按照這種默認的靜態分支預測機制來編譯生成匯編代碼,從而讓低端的CPU也能得到不錯的性能。

為了使硬件設計盡量簡單,RISC-V架構特地定義了所有的帶條件跳轉指令跳轉目標的偏移量(相對於當前指令的地址)都是有符號數,並且其符號位被編碼在固定的位置。因此,這種靜態預測機制在硬件上非常容易實現,硬件譯碼器可以輕松的找到這個固定的位置,並判斷其是0還是1來判斷其是正數還是負數,如果是負數則表示跳轉的目標地址為當前地址減去偏移量,也就是向後跳轉,則預測為“跳”。當然對於配備有硬件分支預測器的高端CPU,則可以采用高級的動態分支預測機制來保證性能。

簡潔的子程序調用

為了理解此節,需先對一般RISC架構中程序調用子函數的過程予以介紹,其過程如下:

- 進入子函數之後需要用存儲器寫(Store)指令來將當前的上下文(通用寄存器等的值)保存到系統存儲器的堆棧區內,這個過程通常稱為“保存現場”。

- 在退出子程序之時,需要用存儲器讀(Load)指令來將之前保存的上下文(通用寄存器等的值)從系統存儲器的堆棧區讀出來,這個過程通常稱為“恢復現場”。

“保存現場”和“恢復現場”的過程通常由編譯器編譯生成的指令來完成,使用高層語言(譬如C或者C++)開發的開發者對此可以不用太關心。高層語言的程序中直接寫上一個子函數調用即可,但是這個底層發生的“保存現場”和“恢復現場”的過程卻是實實在在地發生著(可以從編譯出的匯編語言裏面看到那些“保存現場”和“恢復現場”的匯編指令),並且還需要消耗若幹的CPU執行時間。

為了加速這個“保存現場”和“恢復現場”的過程,有的RISC架構發明了一次寫多個寄存器到存儲器中(Store Multiple),或者一次從存儲器中讀多個寄存器出來(Load Multiple)的指令,此類指令的好處是一條指令就可以完成很多事情,從而減少匯編指令的代碼量,節省代碼的空間大小。但是此種“Load Multiple”和“Store Multiple”的弊端是會讓CPU的硬件設計變得復雜,增加硬件的開銷,也可能損傷時序使得CPU的主頻無法提高,筆者在曾經設計此類處理器時便深受其苦。

RISC-V架構則放棄使用這種“Load Multiple”和“Store Multiple”指令。並解釋,如果有的場合比較介意這種“保存現場”和“恢復現場”的指令條數,那麽可以使用公用的程序庫(專門用於保存和恢復現場)來進行,這樣就可以省掉在每個子函數調用的過程中都放置數目不等的“保存現場”和“恢復現場”的指令。

此選擇再次印證了RISC-V追求硬件簡單的哲學,因為放棄“Load Multiple”和“Store Multiple”指令可以大幅簡化CPU的硬件設計,對於低功耗小面積的CPU可以選擇非常簡單的電路進行實現,而高性能超標量處理器由於硬件動態調度能力很強,可以有強大的分支預測電路保證CPU能夠快速的跳轉執行,從而可以選擇使用公用的程序庫(專門用於保存和恢復現場)的方式減少代碼量,但是同時達到高性能。

無條件碼執行

很多早期的RISC架構發明了帶條件碼的指令,譬如在指令編碼的頭幾位表示的是條件碼(Conditional Code),只有該條件碼對應的條件為真時,該指令才被真正執行。

這種將條件碼編碼到指令中的形式可以使得編譯器將短小的循環編譯成帶條件碼的指令,而不用編譯成分支跳轉指令。這樣便減少了分支跳轉的出現,一方面減少了指令的數目;另一方面也避免了分支跳轉帶來的性能損失。然而,這種“條件碼”指令的弊端同樣會使得CPU的硬件設計變得復雜,增加硬件的開銷,也可能損傷時序使得CPU的主頻無法提高,筆者在曾經設計此類處理器時便深受其苦。

RISC-V架構則放棄使用這種帶“條件碼”指令的方式,對於任何的條件判斷都使用普通的帶條件分支跳轉指令。此選擇再次印證了RISC-V追求硬件簡單的哲學,因為放棄帶“條件碼”指令的方式可以大幅簡化CPU的硬件設計,對於低功耗小面積的CPU可以選擇非常簡單的電路進行實現,而高性能超標量處理器由於硬件動態調度能力很強,可以有強大的分支預測電路保證CPU能夠快速的跳轉執行達到高性能。

無分支延遲槽

很多早期的RISC架構均使用了“分支延遲槽(Delay Slot)”,最具有代表性的便是MIPS架構,在很多經典的計算機體系結構教材中,均使用MIPS對分支延遲槽進行過介紹。分支延遲槽就是指在每一條分支指令後面緊跟的一條或者若幹條指令不受分支跳轉的影響,不管分支是否跳轉,這後面的幾條指令都一定會被執行。

早期的RISC架構很多采用了分支延遲槽誕生的原因主要是因為當時的處理器流水線比較簡單,沒有使用高級的硬件動態分支預測器,所以使用分支延遲槽能夠取得可觀的性能效果。然而,這種分支延遲槽使得CPU的硬件設計變得極為的別扭,CPU設計人員對此往往苦不堪言。

RISC-V架構則放棄了分支延遲槽,再次印證了RISC-V力圖簡化硬件的哲學,因為現代的高性能處理器的分支預測算法精度已經非常高,可以有強大的分支預測電路保證CPU能夠準確的預測跳轉執行達到高性能。而對於低功耗小面積的CPU,由於無需支持分支延遲槽,硬件得到極大簡化,也能進一步減少功耗和提高時序。

無零開銷硬件循環

很多RISC架構還支持零開銷硬件循環(Zero Overhead Hardware Loop)指令,其思想是通過硬件的直接參與,通過設置某些循環次數寄存器(Loop Count),然後可以讓程序自動地進行循環,每一次循環則Loop Count自動減1,這樣持續循環直到Loop Count的值變成0,則退出循環。

之所以提出發明這種硬件協助的零開銷循環是因為在軟件代碼中的for 循環(for i=0; i<="" p=""></N;>

然有得必有失,此類零開銷硬件循環指令大幅地增加了硬件設計的復雜度。因此,零開銷循環指令與RISC-V架構簡化硬件的哲學是完全相反的,在RISC-V架構中自然沒有使用此類零開銷硬件循環指令。

簡潔的運算指令

在本章第2.1節中曾經提到RISC-V架構使用模塊化的方式組織不同的指令子集,最基本的整數指令子集(I字母表示)支持的運算包括加法、減法、移位、按位邏輯操作和比較操作。這些基本的運算操作能夠通過組合或者函數庫的方式完成更多的復雜操作(譬如乘除法和浮點操作),從而能夠完成大多數的軟件操作。

整數乘除法指令子集(M字母表示)支持的運算包括,有符號或者無符號的乘法和除法操作。乘法操作能夠支持兩個32位的整數相乘得到一個64位的結果;除法操作能夠支持兩個32位的整數相除得到一個32位的商與32位的余數。

單精度浮點指令子集(F字母表示)與雙精度浮點指令子集(D字母表示)支持的運算包括浮點加減法,乘除法,乘累加,開平方根和比較等操作,同時提供整數與浮點,單精度與雙精度浮點彼此之間的格式轉換操作。

很多RISC架構的處理器在運算指令產生錯誤之時,譬如上溢(Overflow)、下溢(Underflow)、非規格化浮點數(Subnormal)和除零(Divide by Zero),都會產生軟件異常。RISC-V架構的一個特殊之處是對任何的運算指令錯誤(包括整數與浮點指令)均不產生異常,而是產生某個特殊的默認值,同時,設置某些狀態寄存器的狀態位。RISC-V架構推薦軟件通過其他方法來找到這些錯誤。再次清楚地反映了RISC-V架構力圖簡化基本的指令集,從而簡化硬件設計的哲學。

優雅的壓縮指令子集

基本的RISC-V基本整數指令子集(字母I表示 )規定的指令長度均為等長的32位,這種等長指令定義使得僅支持整數指令子集的基本RISC-V CPU非常容易設計。但是等長的32位編碼指令也會造成代碼體積(Code Size)相對較大的問題。

為了滿足某些對於代碼體積要求較高的場景(譬如嵌入式領域),RISC-V定義了一種可選的壓縮(Compressed)指令子集,由字母C表示,也可以由RVC表示。RISC-V具有後發優勢,從一開始便規劃了壓縮指令,預留了足夠的編碼空間,16位長指令與普通的32位長指令可以無縫自由地交織在一起,處理器也沒有定義額外的狀態。

RISC-V壓縮指令的另外一個特別之處是,16位指令的壓縮策略是將一部分普通最常用的的32位指令中的信息進行壓縮重排得到(譬如假設一條指令使用了兩個同樣的操作數索引,則可以省去其中一個索引的編碼空間),因此每一條16位長的指令都能一一找到其對應的原始32位指令。因此,程序編譯成為壓縮指令僅在匯編器階段就可以完成,極大的簡化了編譯器工具鏈的負擔。

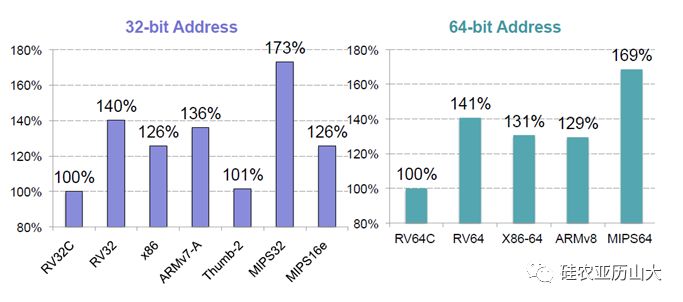

RISC-V架構的研究者進行了詳細的代碼體積分析,如圖3所示,通過分析結果可以看出,RV32C的代碼體積相比RV32的代碼體積減少了百分之四十,並且與ARM,MIPS和x86等架構相比都有不錯的表現。

圖3 各指令集架構的代碼密度比較(數據越小越好)

特權模式

RISC-V架構定義了三種工作模式,又稱特權模式(Privileged Mode):

- Machine Mode:機器模式,簡稱M Mode。

- Supervisor Mode:監督模式,簡稱S Mode。

- User Mode:用戶模式,簡稱U Mode。

RISC-V架構定義M Mode為必選模式,另外兩種為可選模式。通過不同的模式組合可以實現不同的系統。

RISC-V架構也支持幾種不同的存儲器地址管理機制,包括對於物理地址和虛擬地址的管理機制,使得RISC-V架構能夠支持從簡單的嵌入式系統(直接操作物理地址)到復雜的操作系統(直接操作虛擬地址)的各種系統。

CSR寄存器

RISC-V架構定義了一些控制和狀態寄存器(Control and Status Register,CSR),用於配置或記錄一些運行的狀態。CSR寄存器是處理器核內部的寄存器,使用其自己的地址編碼空間和存儲器尋址的地址區間完全無關系。

CSR寄存器的訪問采用專用的CSR指令,包括CSRRW、CSRRS、CSRRC、CSRRWI、CSRRSI以及CSRRCI指令。

中斷和異常

中斷和異常機制往往是處理器指令集架構中最為復雜而關鍵的部分。RISC-V架構定義了一套相對簡單基本的中斷和異常機制,但是也允許用戶對其進行定制和擴展。

矢量指令子集

RISC-V架構目前雖然還沒有定型矢量(Vector)指令子集,但是從目前的草案中已經可以看出,RISC-V矢量指令子集的設計理念非常的先進,由於後發優勢及借助矢量架構多年發展成熟的結論,RISC-V架構將使用可變長度的矢量,而不是矢量定長的SIMD指令集(譬如ARM的NEON和Intel的MMX),從而能夠靈活的支持不同的實現。追求低功耗小面積的CPU可以選擇使用長度較短的硬件矢量進行實現,而高性能的CPU則可以選擇較長的硬件矢量進行實現,並且同樣的軟件代碼能夠彼此兼容。

自定制指令擴展

除了上述闡述的模塊化指令子集的可擴展、可選擇,RISC-V架構還有一個非常重要的特性,那就是支持第三方的擴展。用戶可以擴展自己的指令子集,RISC-V預留了大量的指令編碼空間用於用戶的自定義擴展,同時,還定義了四條Custom指令可供用戶直接使用,每條Custom指令都有幾個比特位的子編碼空間預留,因此,用戶可以直接使用四條Custom指令擴展出幾十條自定義的指令。

總結與比較

處理器設計技術經過幾十年的衍進,隨著大規模集成電路設計技術的發展直至今天,呈現出如下特點:

- 由於高性能處理器的硬件調度能力已經非常強勁且主頻很高,因此,硬件設計希望指令集盡可能的規整、簡單,從而,使得處理器可以設計出更高的主頻與更低的面積。

- 以IoT應用為主的極低功耗處理器更加苛求低功耗與低面積。

- 存儲器的資源也比早期的RISC處理器更加豐富。

如上種種這些因素,使得很多早期的RISC架構設計理念(依據當時技術背景而誕生),時至今日不僅不能幫助現代處理器設計,反而成了負擔桎梏。某些早期RISC架構定義的特性,一方面使得高性能處理器的硬件設計束手束腳;另一方面又使得極低功耗的處理器硬件設計背負不必要的復雜度。

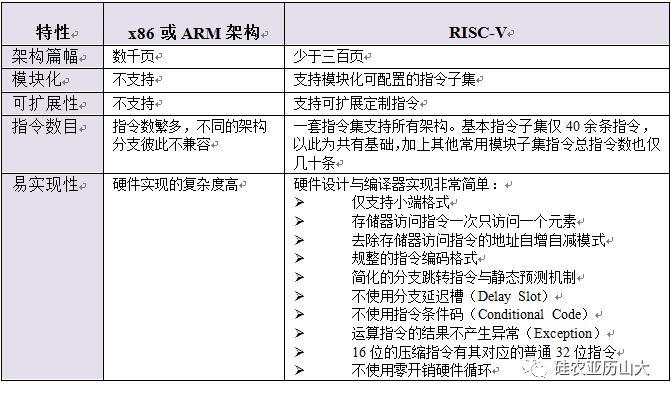

得益於後發優勢,全新的RISC-V架構能夠規避所有這些已知的負擔,同時,利用其先進的設計哲學,設計出一套“現代”的指令集。本節再次將其特點總結如表2所示。

表2 RISC-V指令集架構特點總結

[轉] RISC-V架構介紹