FPGA構建人工神經網絡系統應用實例——視障人士便攜導航系統

以下為楊陽老師演講實錄

源起:使用FPGA搭建視障人士便攜導航系統

在剛剛過去的第八屆華為杯中國大學生智能設計競賽,我們用PaddlePaddle來搭建一個人工神經網絡放到我們自己的硬件平臺裏,實現了基於深度學習的視障人士便攜導航系統,獲得了二等獎。我們選擇這個題目的原因,是考慮中國有大批的視障人群,這些視障人群在出行方面會遇到不少困難。我們傳統的方式需要一些專門的人力、物力幫助視障人士出行,但是這種傳統方式有一定的缺陷性,一般來說需要專人的陪同,另一方面,如果希望視障人士有很好的出行體驗的話,我們需要很昂貴的導盲系統設備。

首先我們通過大規模的行人出行指示圖象,用PaddlePaddle進行大規模的訓練,然後在PaddlePaddle裏搭建一套深度學習神經網絡,將這些深度神經網絡的參數訓練好之後寫到FPGA裏。

當時我們做了一個六層網絡作為核心的單元,網絡系數是通過PaddlePaddle對行人的指示標誌圖象訓練獲得,指示標誌的樣本我們采用了一個國外的實驗室給的一個數據集,比賽的時間比較短,來不及自己采集,直接就用了一個別人的實驗室給我的一個行人指示標誌的圖片,一共是3400張,這就是給一個例子,比如說這樣的情況行人是允許通過的,因為前面可能有斑馬線,這種情況可能是前面施工就禁止通行。

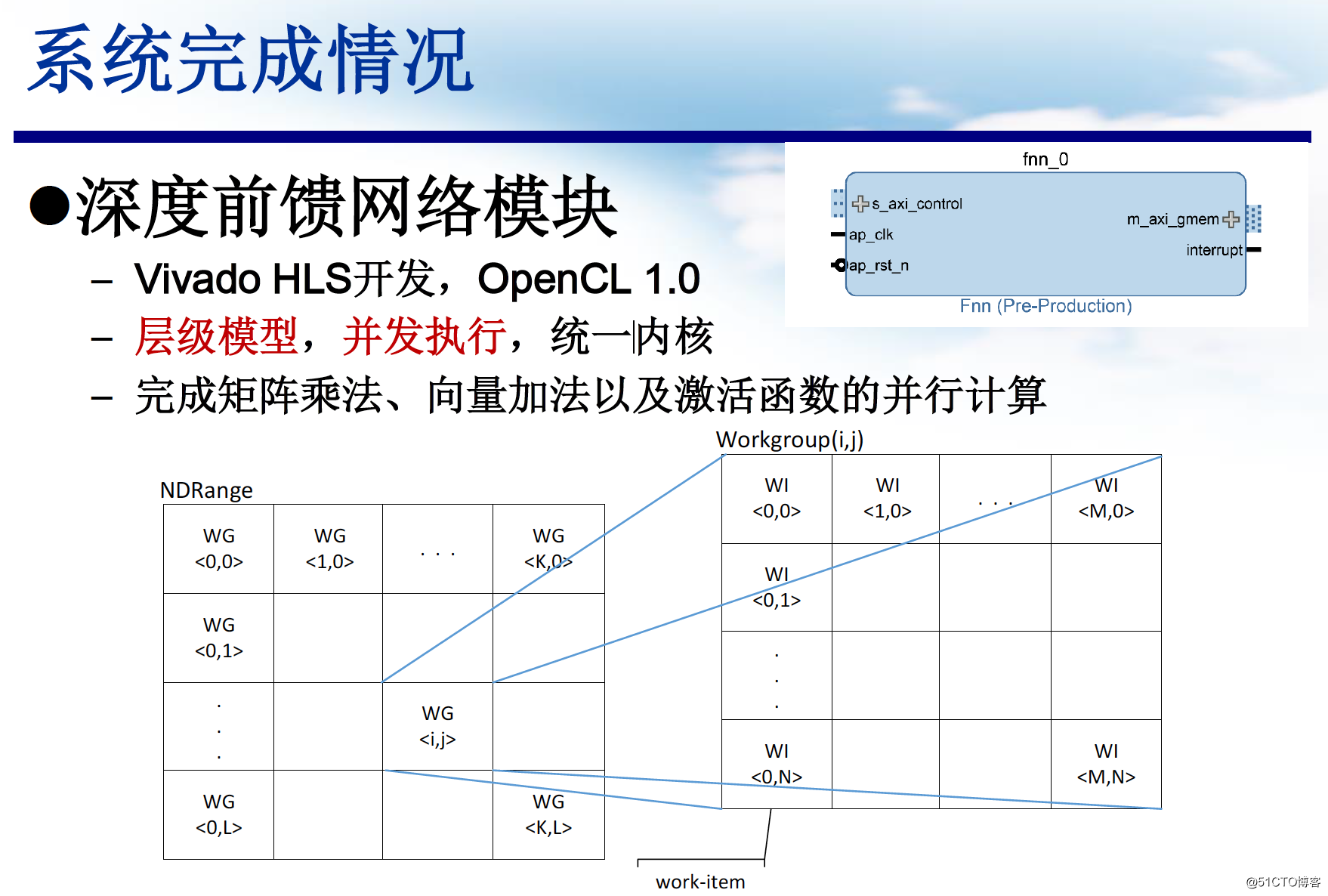

圖一 FPGA並行執行結構

zynq7000包括神經前饋網絡模塊、AXI直接存儲器接入模塊。用AXI這款芯片有一個好處,上層的AIM芯片和底層FPGA的邏輯是通過AXI總線直接連接。第三部分是實時圖象的數據輸入模塊,還有一個偵提取模塊。最核心的是這個,實現了一個將PaddlePaddle的參數直接導入進來以後的模塊,我們采用的是vivado hls、opencl1.0的方式,現在的方式都支持高層,比如說你對C或者C++比較熟悉的時候就可以采用這個方式進行開發。我後面也會講到如何利用高層語言進行一個轉換,就避免了要重新去學習一些底層的繁瑣的硬件代碼。

圖二、數據的讀入、處理顯示以及輸出過程流圖

整個我們當時做的系統流程就是像這樣的情況:首先我們要導入PaddlePaddle生成的網絡參數,然後初始化深度的神經網絡,接下來USB攝像頭捕捉一些圖象送到這個總線當中,接下來AXI直接讀入數據,寫入緩存,接下來就是FPGA處理數據,接下來是實時顯示並輸出,行人在路上走的時候可以實時看到圖象,並且能夠實時輸出。

因為時間關系,我們當時只做在了顯示器上。顯示器會給出一個,信息顯示你能否通行或者不能通行,實際上我們後續希望做出一個音頻的給出一個信號,有一個聲音提示行人。

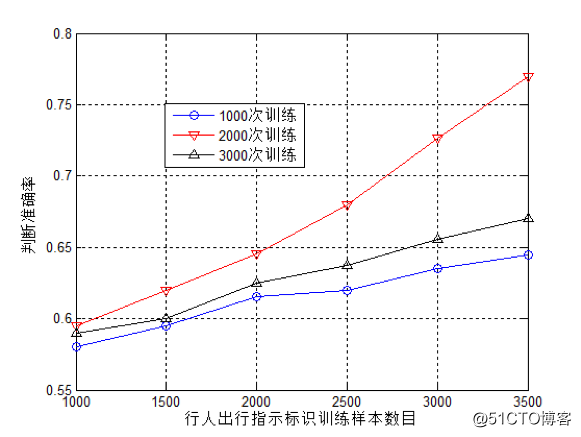

圖三、行人指示標識圖像訓練樣本數目vs. 判斷準確率

參賽的時候訓練集比較有限,我們采用的圖片一共3400張,所以整個訓練襲來,我們最高準確率也只達到了75%。深度學習進行行人指示能否通過和不通過本身是一個概率的事情,我們達到了最高是2000次訓練的,實際上這條曲線3000次訓練沒有2000次訓練好,因為3000次達到了一個過擬合的情況,所以反而沒有2000次的好。但是總體趨勢是這樣,隨著PaddlePaddle的訓練圖片數目的不斷增大,準確率不斷上升。如果我們後期加大數據集的話,可能準確率還會有所上升。

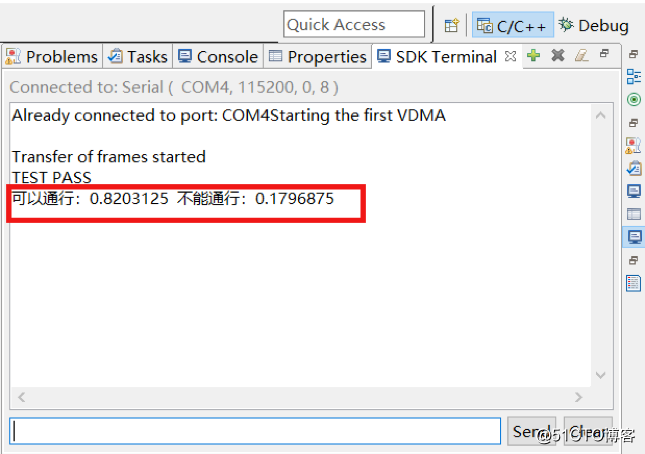

圖四、單張行人指示標識圖像判斷結果示例

這個地方給出了一個單張行人指示標識的判斷結果,最後判斷出來的時候實際上是一個概率事件,你最後出來的時候,我們用的是一個什麽,判斷一下這個是0.8,我們認為比不能通行的概率大就可以通行。

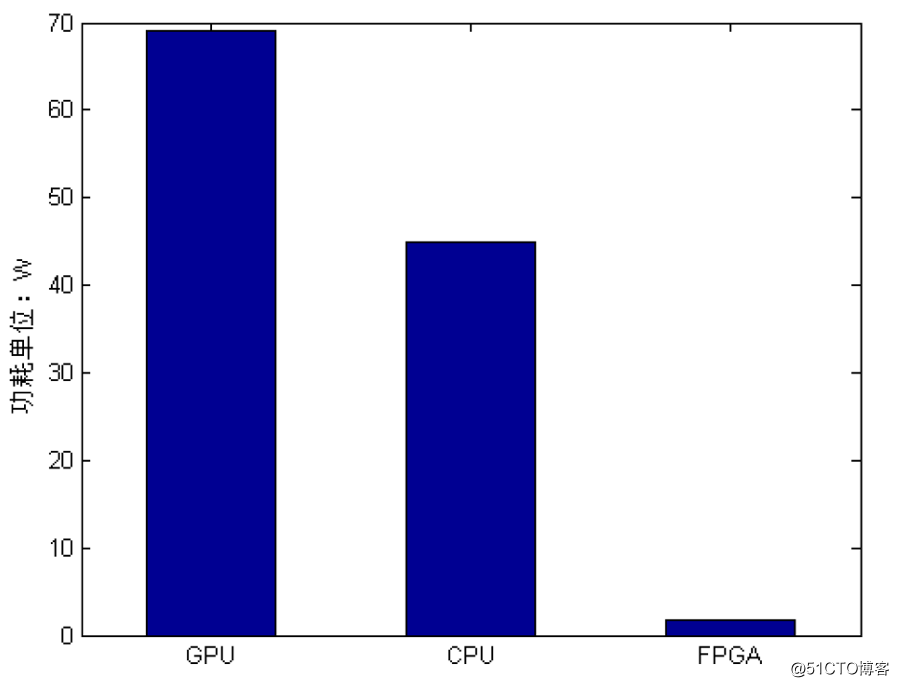

FPGA的性能優勢

使用FPGA,可以大大降低功耗,如果你把整個深度神經網絡在GPU上或者CPU上實現,功耗會非常高,而用FPGA功耗最低可達1.725瓦。這兩個參數我們測的時候是采用了看GPU實際運行中的額定功率,GPU功耗是比較大的。而且使用GPU識別的時候,不便於小型化,因為不可能背著GPU出去到處走。用FPGA功耗比較低是一個亮點,超低的功耗使得FPGA在續航和小型化方面優點比較明顯,體積小是另一個亮點。

圖五、GPU、CPU與FPGA功耗對比

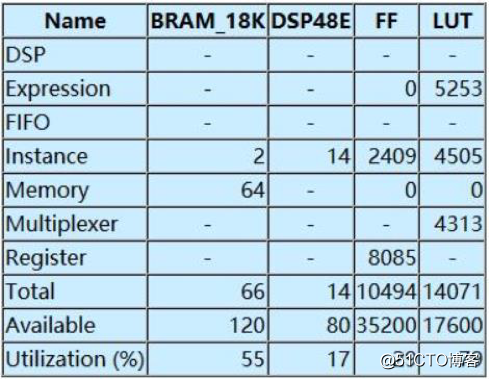

圖六、系統資源占用情況

然後我們給出了一個資源占用情況分析,因為你在FPGA當中做的是定點數的計算,所以我們要對網絡,因為你不管是PaddlePaddle生成出來的參數也好,你最後寫入到FPGA的時候可能要考慮到從一個浮點數轉到靜點數。所以我們就要采點數,這和本身芯片設計有關系,芯片大小決定了你能放多大的深度神經網絡,我們當時使用的是六層的神經網絡,資源占用率是達到了79%,滿足了芯片的要求,後期可以選擇更大的FPGA的芯片。

FPGA的應用潛力

傳統的深度學習框架很多都是跑在GPU和CPU上,對於FPGA目前為止好像還沒有成熟的深度學習框架,在這個地方我希望通過一個拋磚引玉的思路給大家一個思路,如果大以後有興趣可以在FPGA上實現深度學習框架。現在很多主流的廠商,他們都在做自己的一些想在自己的FPGA上搭自己的深度學習框架。

應用背景是隨著大數據的爆發式增長,人工智能技術也得到了快速的發展,高性能計算的需求日益增長,可以看到像這樣的數據中心,還有一些人工智能的判斷,包括百度的阿波羅做無人駕駛這方面,我們在傳統計算當中已經不能滿足我們現在需要的這種計算的速度,所以我們需要用FPGA進行一個加速,傳統芯片提升功耗比方面遇到了一個極大的挑戰。

與計算平臺的對比,實際上可以看到如果你采用傳統的ASIC開發芯片,功耗是很低的,但是開發周期是非常長的,因為你要把所有的可能性想好之後做定制,定制需要的ASIC芯片。GPU開發周期短,性能也好,但是功耗太高了。FPGA介於這兩者之間,開發周期較短,性能好,也比較適合做深度學習的計算,功耗特別低,所以一般來說我們可以考慮使用介於兩者之間的FPGA進行一個開發。

深度學習分為兩部分,首先第一部分是訓練,第二部分是推斷。訓練這一部分是從已有的深度學習學習到新的能力,推斷是將學習的新能源應用到新數據當中,比如說形成一個深度神經網絡的話就可以捎入到需要的芯片當中。很多的深度學習框架都不支持FPGA,但是前段時間PaddlePaddle提供了一些支持FPGA的接口,所以大家有興趣可以看一下提供的接口的鏈接:https://github.com/PaddlePaddle/paddle-mobile/tree/ca32dc7f40e75080d203b7de3cd1ae30feb612c9/src/operators/kernel/fpga。

這個地方我們希望PaddlePaddle可以做更好的支持,首先是支持FPGA上訓練和推斷,第二是優化FPGA的計算加速,訓練模型在FPGA和CPU,GPU之間可以無縫對接,有了這樣的深度學習框架可以在GPU上跑,可以在CPU上跑,也可以在FPGA上跑。

使用FPGA搭建CNN模型

如何在FPGA上面搭一個深度學習框架,我們當時采用的是xilinx的開發板,其實也可以采用其他的開發板,這個板子也挺貴的,兩萬三一個。當時采用的操作系統是centos,開發環境是vivado、SDX,上層是支持C的,在上層的時候可以用C或者C++進行開發,底層實際運行可以進行一個轉換,效率上可能會低一些,但是會加速你的開發的周期,這樣的話可以用上層的語言。首先通過我們的主機端,通過板子構成一整個的深度學習框架的開發的硬件環境,他有一些包括裏面的PCl-e的控制器,整個框架支持C++和Opencl的開發,有了這樣的硬件環境對於你後期想在這上面部署一個深度學習框架其實是有好處的。

框架是如何實現,這是一個自己向上的設計和思路,我們分了幾部分,第一部分blob,進行封裝數據的讀寫。第二部分采用layer,把封裝好的數據利用blob進行不同功能的具體計算,接下來用net進行組合,就是把所有的每一個層進行串起來,串起來之後把每一個層組合神經網絡,最後有一個solve控制神經網絡的流程。

設備端可以做一個優化,實際上FPGA比較適合來做定點數的,浮點數對於FPGA來說不是一個特別有優勢的功能,我們的定點數實際上位寬比較少,節省資源。第二個是整型的數據,利於硬件的運算,這兒給出了一個例子,當然這個例子其實在網上大家也可以看到很多定點數和浮點數的轉換。

最後你可以看到精度損失是比較小的,一般是可以忽略的。實際上最後也給出了一個引證,我們在FPGA上,如果想去搭深度學習框架,如果采用定點數,實際上是有一定的可能性的。我們當時比較了一下,進行一次兩次的加法,乘法節省的時間分別達到40%和29%,所以從這個圖上可以看到32位單精度浮點數,我們的定點數位寬Q=11的時候可以節省相應的資源。同時我們用了手寫數字的數據集運行了一下數據集,如果在FPGA上搭這樣的一個深度學習的框架,其實你可以看到定點和浮點這兩個準確率幾乎可以達到一致。

其實FPGA裏還有一個很好的特色就是有一個pipeline,就是所謂的流水線,用定點數據依賴,增加算法硬件實現的並行性的數字設計方法,用串型的計算,比如說8個周期進行傳統的計算的時候,比如說8個周期是一個串型的計算,利用這個流水線把每個單元進行並行化,實際上可以看到采用更少的時間周期可以進行並行的計算,可以大大降低邏輯資源。

實錄結束

楊陽

2015年博士畢業於北京郵電大學信息與通信工程學院,同年進入清華大學電子系從事博士後研究工作,目前就職於北京郵電大學,任職講師,研究興趣方向為人工智能、智能硬件與通信網絡,國家自然科學基金青年基金獲得者,中國博士後科學基金面上項目獲得者,發表SCI期刊論文6篇,EI期刊17篇,申請國際專利3項,國內專利4項,參與國家國家重大專項項目一項。指導留學生3名,碩士研究生四名並獲得國家級學科競賽獎勵四項。

FPGA構建人工神經網絡系統應用實例——視障人士便攜導航系統