PCB設計流程

基本流程:前期準備->PCB結構設計->PCB布局->布線->布線優化和絲印->網絡和DRC檢查和結構檢查->制版。

1.前期準備

軟件工具+相應的庫(一定要積累,形成自己的原理圖庫和封裝庫)

元件庫要求:

1.管腳屬性和PCB相對應

2.簡單清晰易懂

比如畫芯片時在原理圖上最好能看到芯片大小形狀和1腳等,便於在焊接調試對照。

封裝庫:

尺寸要求,焊盤要比datasheet的大一點,註意常用1206 0805 0603 0402以免弄混。過孔也要大一點。

(原則上先做封裝庫再做原理圖庫)

常用封裝:

SMD:surface mount devices 表面貼裝

BGA:ball grid array 球形觸點陣列

SIP:single in-line package 單排直插封裝

DIP:dual in-line package 雙排直插封裝

QFP:quad flat package 四側引腳偏平封裝

四側引腳扁平封裝。引腳中心距有1.0mm、0.8mm、0.65mm、0.5mm、0.4mm、0.3mm 等多種規格。

日本將引腳中心距小於 0.65mm 的QFP稱為 QFP(FP)。但現在日本電子機械工業會對QFP的

外形規格進行了重新評價。在引腳中心距上不加區別,而是根據封裝本體厚度分為

QFP(2.0mm~3.6mm 厚)、LQFP(1.4mm 厚)和 TQFP(1.0mm 厚)三種。

另外,有的 LSI 廠家把引腳中心距為 0.5mm 的 QFP 專門稱為收縮型 QFP 或 SQFP、VQFP。

但有的廠家把引腳中心距為 0.65mm 及 0.4mm 的 QFP 也稱為 SQFP,至使名稱稍有一些混

亂。

FQFP:fine pitch quad flat package 小引腳中心距 QFP,e<0.65mm

LQFP:low profile quad flat package 薄型QFP ,本體厚度=1.4mm

TQFP:本體厚度=1mm

CQFP:Ceramic Quad Flat Pack 陶瓷QFP

QFN:無引出腳封裝,又稱為LCC、PCLC、P-LCC等;e=1.27mm ,0.65mm ,0.5mm ,

SOP:Small Out-Line Package 小外形封裝,e=1.27mm,8~44腳

SSOP:shrink small-outline package 窄間距小外形塑封,e<1.27mm,常用的e=0.65mm

TSOP:Thin Small Outline Package 微型薄片式封裝,本體厚度<1.27mm

TSSOP:Thin Shrink Small Outline Package

SOJ:塑料J形線封裝

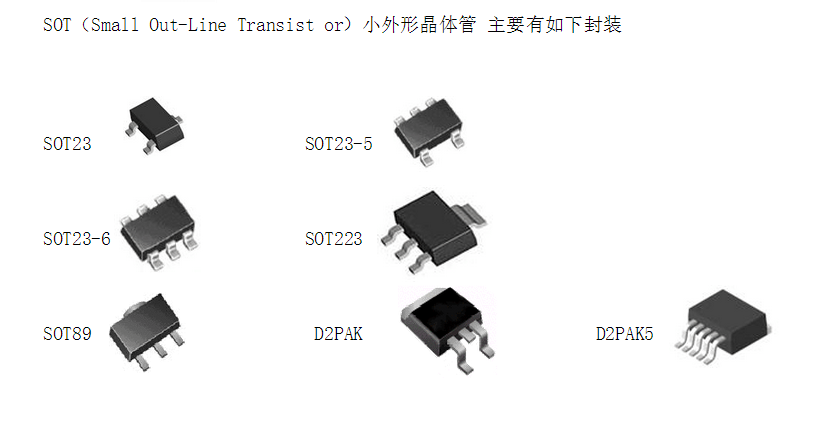

SOT:small out-line transistor 小外形晶體管,e=0.95mm

2.PCB結構設計

根據已經確定的電路板尺寸和各項機械定位,在PCB 設計環境下繪制PCB板面,並按定位要求放置所需的接插件、按鍵/開關、螺絲孔、裝配孔等等。並充分考慮和確定布線區域和非布線區域(如螺絲孔周圍多大範圍屬於非布線區域)。

3.PCB布局

①. 按電氣性能合理分區,一般分為:數字電路區(即怕幹擾、又產生幹擾)、模擬電路區(怕幹擾)、功率驅動區(幹擾源);

②. 完成同一功能的電路,應盡量靠近放置,並調整各元器件以保證連線最為簡潔;同時,調整各功能塊間的相對位置使功能塊間的連線最簡潔;

③. 對於質量大的元器件應考慮安裝位置和安裝強度;發熱元件應與溫度敏感元件分開放置,必要時還應考慮熱對流措施;

④. I/O驅動器件盡量靠近印刷板的邊、靠近引出接插件;

⑤. 時鐘產生器(如:晶振或鐘振)要盡量靠近用到該時鐘的器件;

⑥. 在每個集成電路的電源輸入腳和地之間,需加一個去耦電容(一般采用高頻性能好的獨石電容);電路板空間較密時,也可在幾個集成電路周圍加一個鉭電容。

鉭電容的優點:容量變化受外界環境影響小,體積小,使用溫度範圍寬,耐高溫以及壽命長,絕緣電阻高,漏電流小和容量誤差小等都是鉭電容所存在的優點,而且能在極其嚴峻在條件下工作。

獨石電容:也被稱之為是瓷介電容,這類電容具有容量大,體積小的優勢,而且具有較強的耐高溫性能。相對而言是電容類型中優點諸多的電容之一。

⑦. 繼電器線圈處要加放電二極管(1N4148即可);

⑧. 布局要求要均衡,疏密有序,不能頭重腳輕或一頭沈

一定要考路元器件的大小封裝高度相對位置,修改器件的擺放,使之整齊美觀。

4.布線

布線是整個PCB設計中最重要的工序。這將直接影響著PCB板的性能好壞。

①.一般情況下,首先應對電源線和地線進行布線,以保證電路板的電氣性能。在條件允許的範圍內,盡量加寬電源、地線寬度,最好是地線比電源線寬,它們的關系是:地線>電源線>信號線,通常信號線寬為:0.2~0.3mm,最細寬度可達0.05~0.07mm,電源線一般為1.2~2.5mm。對數字電路的 PCB可用寬的地導線組成一個回路, 即構成一個地網來使用(模擬電路的地則不能這樣使用)

②. 預先對要求比較嚴格的線(如高頻線)進行布線,輸入端與輸出端的邊線應避免相鄰平行,以免產生反射幹擾。必要時應加地線隔離,兩相鄰層的布線要互相垂直,平行容易產生寄生耦合。

③. 振蕩器外殼接地,時鐘線要盡量短,且不能引得到處都是。時鐘振蕩電路下面、特殊高速邏輯電路部分要加大地的面積,而不應該走其它信號線,以使周圍電場趨近於零;

④. 盡可能采用45o的折線布線,不可使用90o折線,以減小高頻信號的輻射;(要求高的線還要用雙弧線)

⑤. 任何信號線都不要形成環路,如不可避免,環路應盡量小;信號線的過孔要盡量少;

⑥. 關鍵的線盡量短而粗,並在兩邊加上保護地。

⑦. 通過扁平電纜傳送敏感信號和噪聲場帶信號時,要用“地線-信號-地線”的方式引出。

⑧. 關鍵信號應預留測試點,以方便生產和維修檢測用

⑨.原理圖布線完成後,應對布線進行優化;同時,經初步網絡檢查和DRC檢查無誤後,對未布線區域進行地線填充,用大面積銅層作地線用,在印制板上把沒被用上的地方都與地相連接作為地線用。或是做成多層板,電源,地線各占用一層。

①. 線

一般情況下,信號線寬為0.3mm(12mil),電源線寬為0.77mm(30mil)或1.27mm(50mil);線與線之間和線與焊盤之間的距離大於等於0.33mm(13mil),實際應用中,條件允許時應考慮加大距離;

布線密度較高時,可考慮(但不建議)采用IC腳間走兩根線,線的寬度為0.254mm(10mil),線間距不小於0.254mm(10mil)。特殊情況下,當器件管腳較密,寬度較窄時,可按適當減小線寬和線間距。

②. 焊盤(PAD)

焊盤(PAD)與過渡孔(VIA)的基本要求是:盤的直徑比孔的直徑要大於0.6mm;例如,通用插腳式電阻、電容和集成電路等,采用盤/孔尺寸 1.6mm/0.8mm(63mil/32mil),插座、插針和二極管1N4007等,采用1.8mm/1.0mm(71mil/39mil)。實際應用中,應根據實際元件的尺寸來定,有條件時,可適當加大焊盤尺寸;

PCB板上設計的元件安裝孔徑應比元件管腳的實際尺寸大0.2~0.4mm左右。

③. 過孔(VIA)

一般為1.27mm/0.7mm(50mil/28mil);

當布線密度較高時,過孔尺寸可適當減小,但不宜過小,可考慮采用1.0mm/0.6mm(40mil/24mil)。

④. 焊盤、線、過孔的間距要求

PAD and VIA : ≥ 0.3mm(12mil)

PAD and PAD : ≥ 0.3mm(12mil)

PAD and TRACK : ≥ 0.3mm(12mil)

TRACK and TRACK : ≥ 0.3mm(12mil)

密度較高時:

PAD and VIA : ≥ 0.254mm(10mil)

PAD and PAD : ≥ 0.254mm(10mil)

PAD and TRACK : ≥ 0.254mm(10mil)

TRACK and TRACK : ≥ 0.254mm(10mil)

5.布線優化和絲印

一般設計的經驗是:優化布線的時間是初次布線的時間的兩倍。感覺沒什麽地方需要修改之後,就可以鋪銅了(Place->polygon Plane)。

6.網絡的DRC檢查和結構檢查

首先,在確定電路原理圖設計無誤的前提下,將所生成的PCB網絡文件與原理圖網絡文件進行物理連接關系的網絡檢查(NETCHECK),並根據輸出文件結果及時對設計進行修正,以保證布線連接關系的正確性;

網絡檢查正確通過後,對PCB設計進行DRC檢查,並根據輸出文件結果及時對設計進行修正,以保證PCB布線的電氣性能。最後需進一步對PCB的機械安裝結構進行檢查和確認。

7.制版

PCB設計流程