《XDC約束技巧之時鐘篇

阿新 • • 發佈:2018-11-04

《XDC約束技巧之時鐘篇》中曾對I/O約束做過簡要概括,相比較而言,XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應用特性決定了其在介面上有多種構建和實現方式,所以從UCF到XDC的轉換過程中,最具挑戰的可以說便是本文將要討論的I/O約束了。

繼《XDC約束技巧之I/O篇(上)》 詳細描述瞭如何設定Input介面約束後,我們接著來聊聊怎樣設定Output介面約束,並分析UCF與XDC在介面約束上的區別。

Input介面型別和約束

FPGA做Output的介面時序同樣也可以分為系統同步與源同步。在設定XDC約束時,總體思路與Input類似,只是換成要考慮下游器件的時序模型。另外,在源同步介面中,定義介面約束之前,需要用create_generated_clock先定義送出的隨路時鐘。

系統同步介面

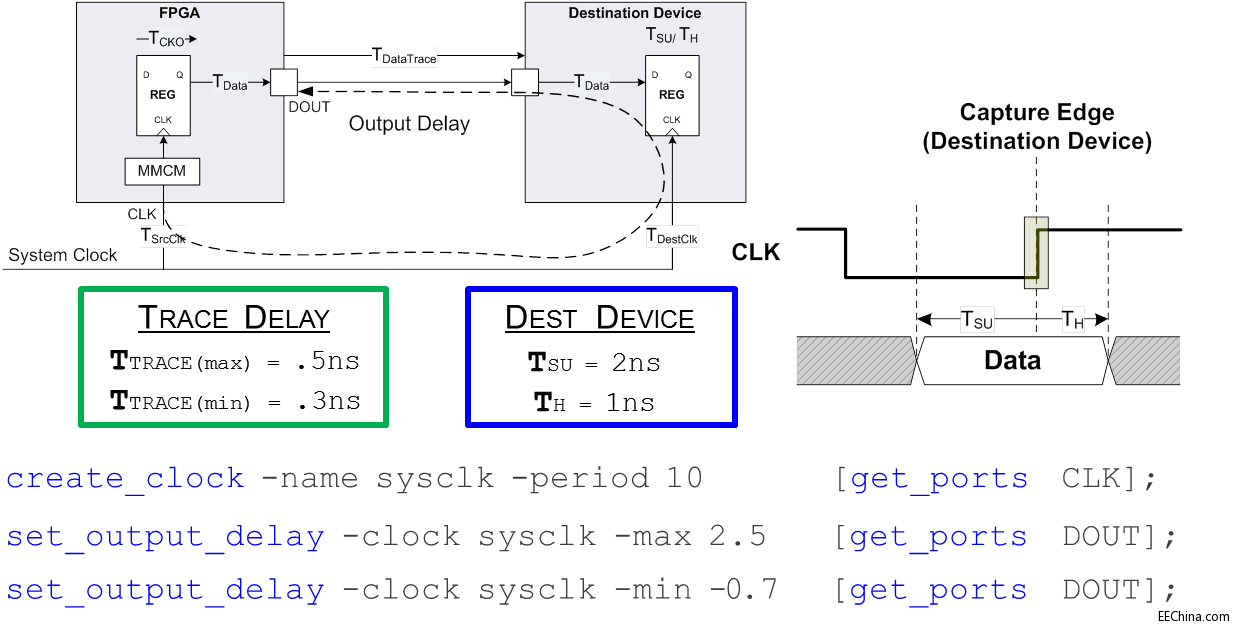

與Input的系統同步介面一樣,FPGA做Output介面的系統同步設計,晶片間只傳遞資料訊號,時鐘訊號的同步完全依靠板級設計來對齊。所以設定約束時候要考慮的僅僅是下游器件的Tsu/Th和資料在板級的延時。

上圖是一個SDR上升沿取樣系統同步介面的Output約束示例。其中,-max後的數值是板級延時的最大值與下游器件的Tsu相加而得出,-min後的數值則是板級延時的最小值減去下游器件的Th而來。

源同步介面

與源同步介面的Input約束設定類似,FPGA做源同步介面的Output也有兩種方法可以設定約束。

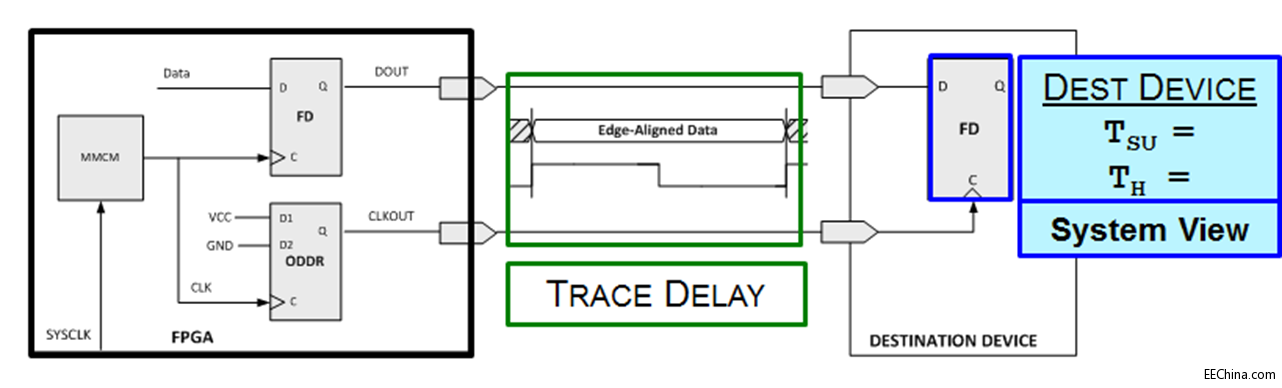

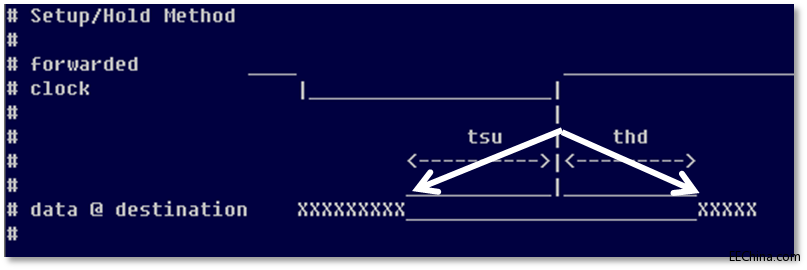

方法一我們稱作Setup/Hold Based Method,與上述系統同步介面的設定思路基本一致,僅需要了解下游器件用來鎖存資料的觸發器的Tsu與Th值與系統板級的延時便可以設定。方法二稱作 Skew Based Method,此時需要了解FPGA送出的資料相對於時鐘沿的關係,根據Skew的大小和時鐘頻率來計算如何設定 Output約束。

具體約束時可以根據不同的已知條件,選用不同的約束方式。一般而言,FPGA作為輸出介面時,資料相對時鐘的Skew關係是已知條件(或者說,把同步資料相對於時鐘沿的Skew限定在一定範圍內是設計源同步介面的目標),所以方法二更常見。

Vivado IDE的Language Templates中關於源同步輸出介面的XDC約束模板包含了以上兩種方式的設定方法。

方法一Setup/Hold Based Method

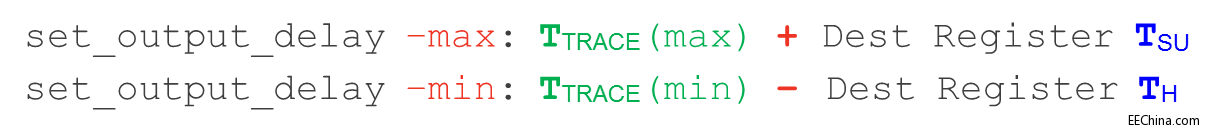

Setup/Hold Method的計算公式如下,可以看出其跟系統同步輸出介面的設定方法完全一樣。如果換成DDR方式,則可參考上一篇I/O約束方法中關於Input源同 步DDR介面的約束,用 兩個可選項-clock_fall與 -add_delay來新增針對時鐘下降沿的約束值。

如果板級延時的最小值(在源同步介面中,因為時鐘與訊號同步傳遞,所以板級延時常常可以視作為0)小於接收端暫存器的Th,這樣計算出的結果就會在 -min 後出現負數值,很多時候會讓人誤以為設定錯誤。其實這裡的負數並不表示負的延遲,而代表最小的延遲情況下,資料是在時鐘取樣沿之後才有效。同樣的,- max後的正數,表示最大的延遲情況下,資料是在時鐘取樣沿之前就有效了。

這便是介面約束中最容易混淆的地方,請一定牢記set_output_delay中 -max/-min的定義,即時鐘取樣沿到達之前最大與最小的資料有效視窗。

如果我們在紙上畫一下接收端的波形圖,就會很容易理解:用於setup分析的 -max之後跟著正數,表示資料在時鐘取樣沿之前就到達,而用於hold分析的 -min之後跟著負數,表示資料在時鐘取樣沿之後還保持了一段時間。只有這樣才能滿足接收端用於鎖存介面資料的觸發器的Tsu和Th要求。

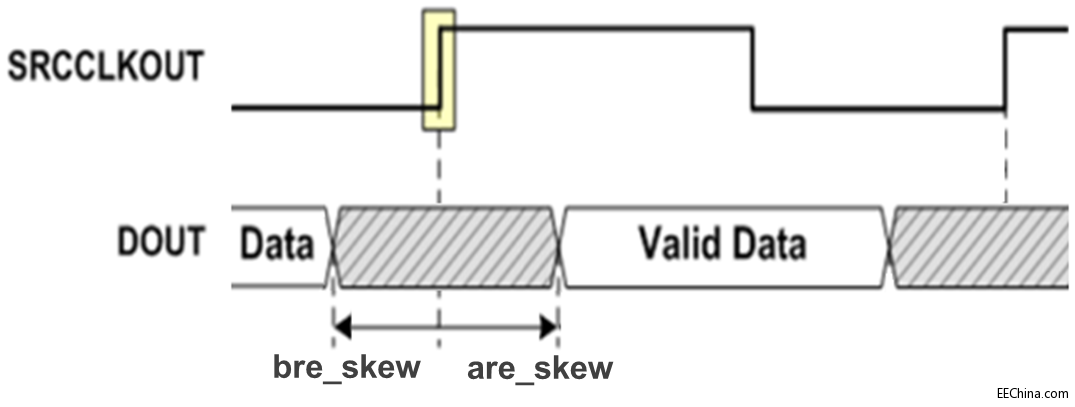

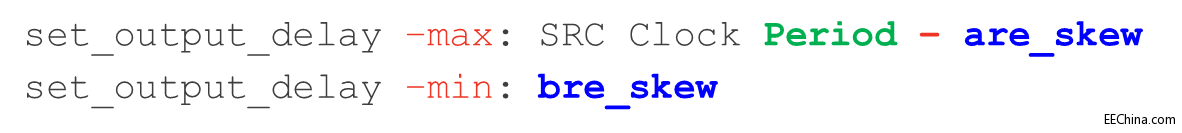

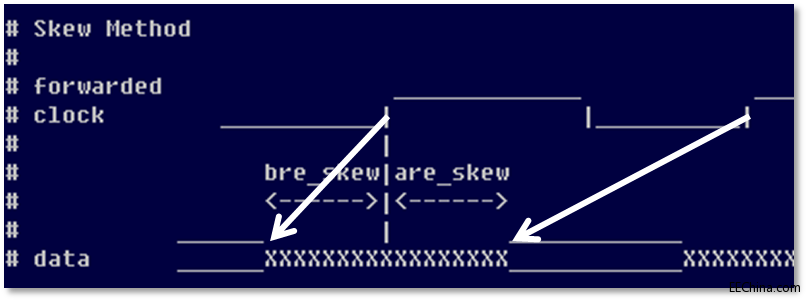

方法二 Skew Based Method

為了把同步資料相對於時鐘沿的Skew限定在一定範圍內,我們可以基於Skew的大小來設定源同步輸出介面的約束。此時可以不考慮下游取樣器件的Tsu與Th值。

我們可以通過波形圖來再次驗證 set_output_delay中 -max/-min的定義,即時鐘取樣沿到達之前最大與最小的資料有效視窗。

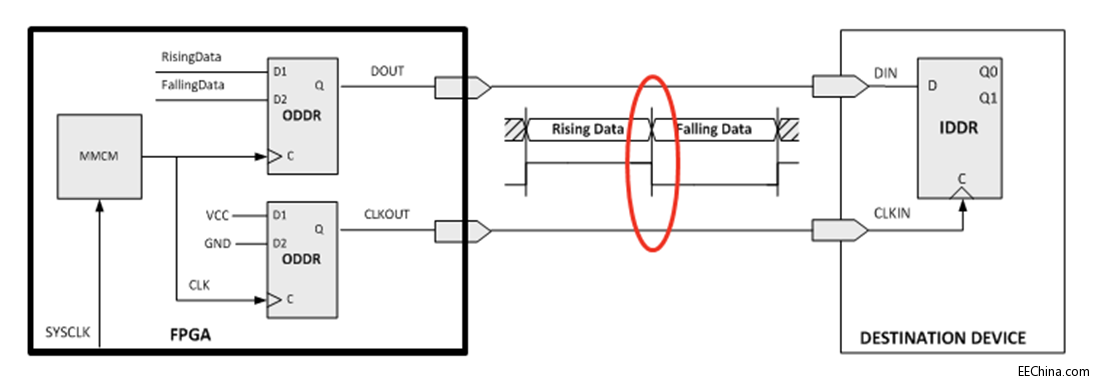

DDR介面的約束設定

DDR介面的約束稍許複雜,需要將上升沿和下降沿分別考慮和約束,以下以源同步介面為例,分別就Setup/Hold Based 方法和Skew Based方法舉例。

方法一Setup/Hold Based Method

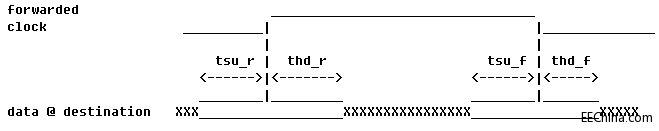

已知條件如下:

時鐘訊號 src_sync_ddr_clk的頻率: 100 MHz

隨路送出的時鐘src_sync_ddr_clk_out的頻率: 100 MHz

資料匯流排: src_sync_ddr_dout[3:0]

接收端的上升沿建立時間要求 ( tsu_r ) :7 ns

接收端的上升沿保持時間要求 (thd_r ) :3 ns

接收端的下降沿建立時間要求 (tsu_f) :6 ns

接收端的下降沿保持時間要求 (thd_f ) :4 ns

板級走線延時:0 ns

可以這樣計算輸出介面約束:已知條件包含接收端上升沿和下降沿的建立與保持時間要求,所以可以分別獨立計算。上升沿取樣資料的 -max 是板級延時的最大值加上接收端的上升沿建立時間要求(tsu_r),對應的-min 就應該是板級延時的最小值減去接收端的上升沿保持時間要求(thd_r);下降沿取樣資料的 -max 是板級延時的最大值加上接收端的下降沿建立時間要求(tsu_f),對應的-min 就應該是板級延時的最小值減去接收端的下降沿保持時間要求(thd_f)。

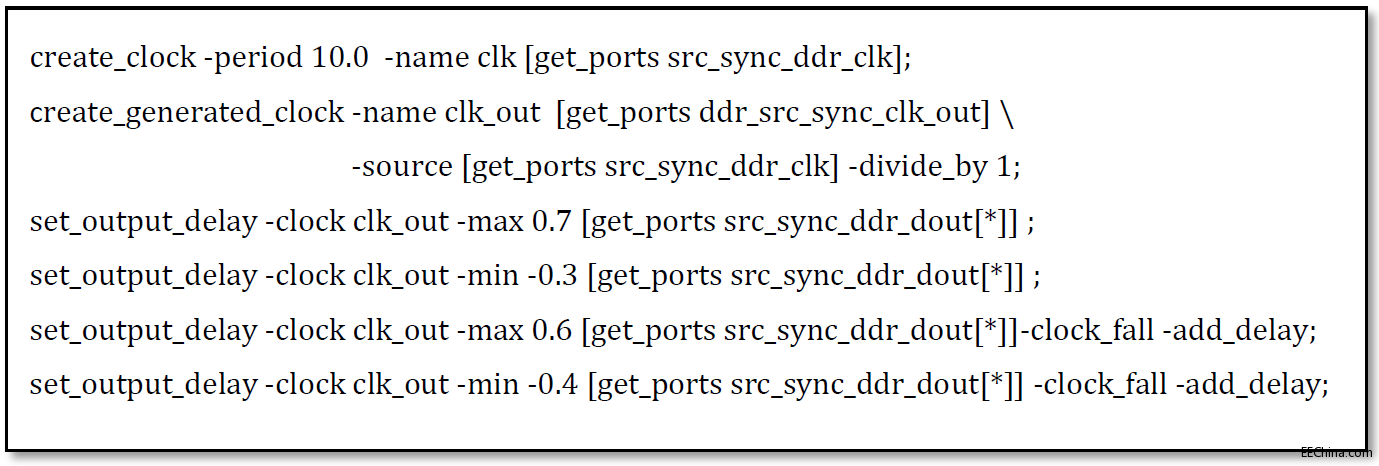

所以最終寫入XDC的Output約束應該如下所示:

方法二 Skew Based Method

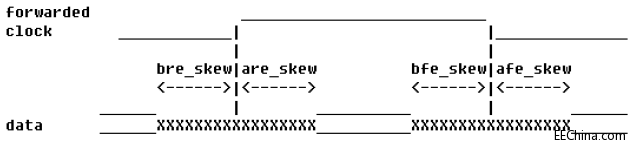

已知條件如下:

時鐘訊號 src_sync_ddr_clk的頻率: 100 MHz

隨路送出的時鐘src_sync_ddr_clk_out的頻率: 100 MHz

資料匯流排: src_sync_ddr_dout[3:0]

上升沿之前的資料skew ( bre_skew ) :4 ns

上升沿之後的資料skew ( are_skew ) :6 ns

下降沿之前的資料skew ( bfe_skew ) :7 ns

下降沿之後的資料skew ( afe_skew ) :2 ns

可以這樣計算輸出介面約束:時鐘的週期是10ns,因為是DDR方式,所以資料實際的取樣週期是時鐘週期的一半;上升沿取樣的資料的 -max 應該是取樣週期減去這個資料的傳送沿(下降沿)之後的資料skew即afe_skew,而對應的-min 就應該是上升沿之前的資料skew值bre_skew ;同理,下降沿取樣資料的 -max 應該是取樣週期減去這個資料的傳送沿(上升沿)之後的資料skew值are_skew,而對應的-min 就應該是下降沿之前的資料skew值bfe_skew 。

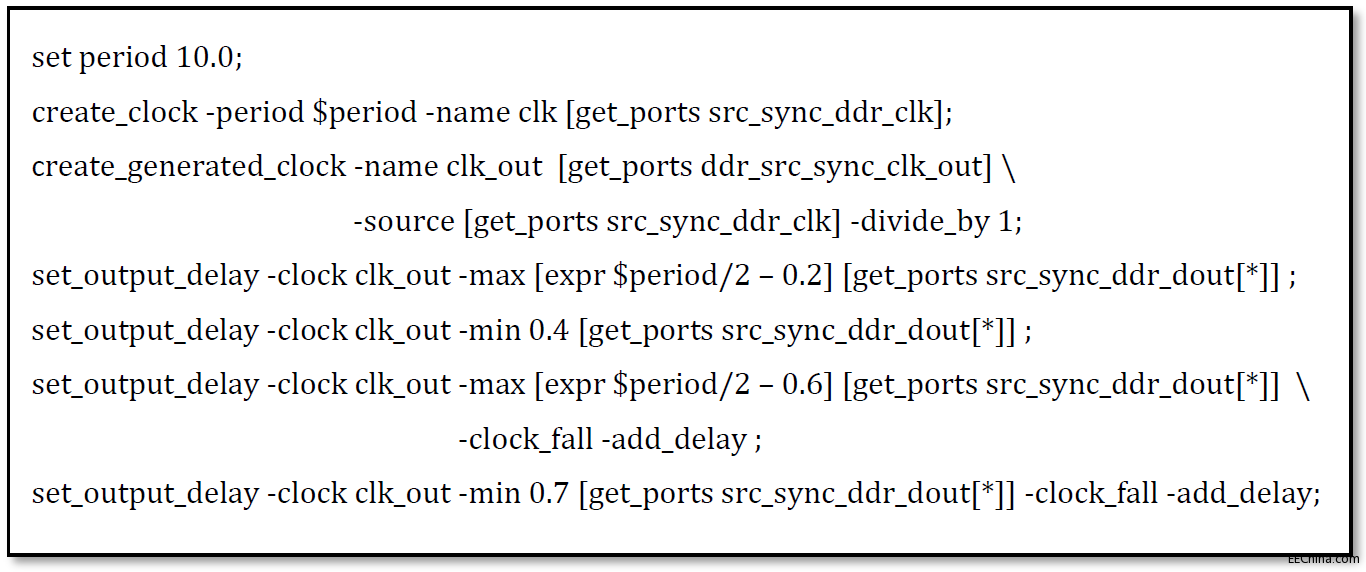

所以最終寫入XDC的Output約束應該如下所示:

對以上兩種方法稍作總結,就會發現在設定DDR源同步輸出介面時,送出的資料是中心對齊的情況下,用Setup/Hold Based 方法來寫約束比較容易,而如果是邊沿對齊的情況,則推薦使用Skew Based方法來寫約束。

在Vivado中設定介面約束

FPGA的介面約束種類多變,遠非一篇短文可以完全覆蓋。在具體設計中,建議使用者參照Vivado IDE的Language Templates 。其中關於介面約束的例子有很多,而且也是按照本文所述的各種分類方法分別列出。

具體使用時,可以在列表中找到對應的介面型別,按照模板所示調整成自己設計中的資料,然後可以方便地計算出實際的約束值,並應用到FPGA工程中去。

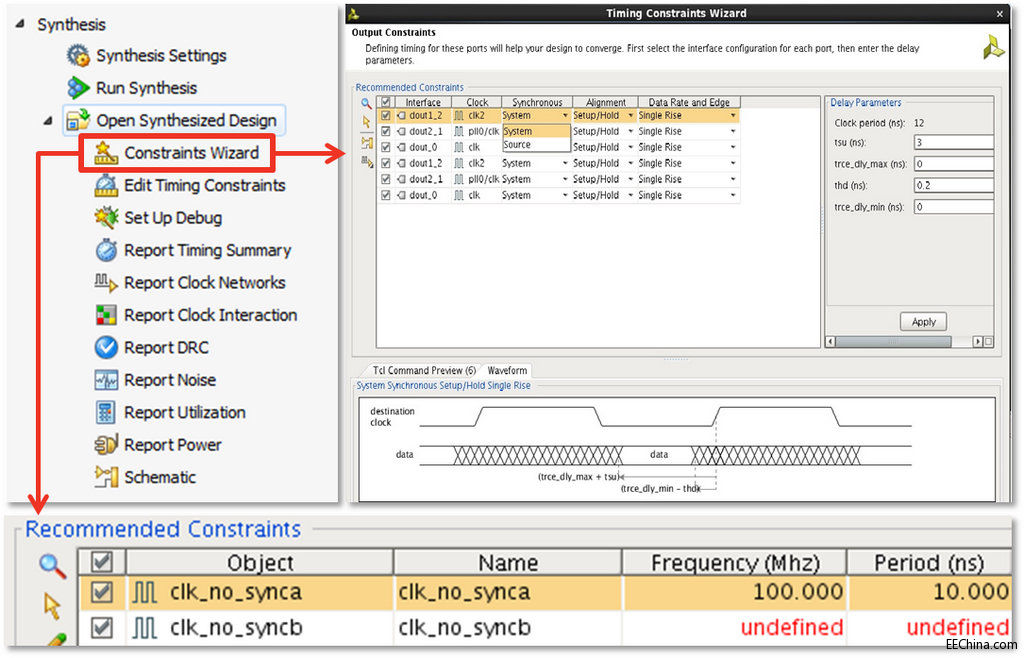

自2014.1版開始,Vivado還提供一個Constraints Wizard可供使用者使用。只需開啟綜合後的設計,然後啟動Wizard,工具便可以根據讀到的網表和設計中已有的XDC時序約束(也可以任何約束都不加 而開始用Wizard)一步步指引使用者如何新增Timing約束,包括時鐘、I/O 以及時序例外約束等等。

Constraints Wizard的調出方法和介面如下圖所示。

UCF與XDC的區別

《XDC約束技巧》開篇描述XDC基礎語法時候曾經提到過設定介面約束時UCF與XDC的區別,簡單來講,UCF是原生的FPGA約束,所以分析問題的視角是FPGA本身,而XDC則是從系統設計的全域性角度來分析和設定介面約束。

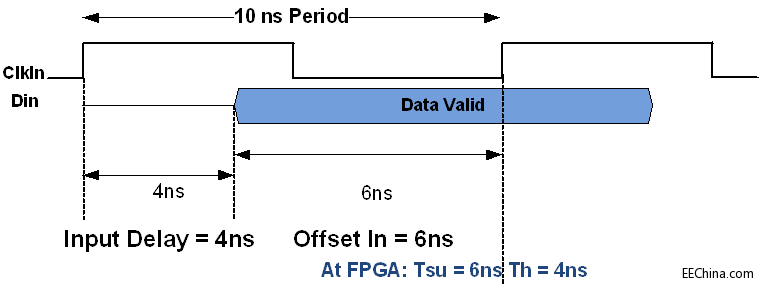

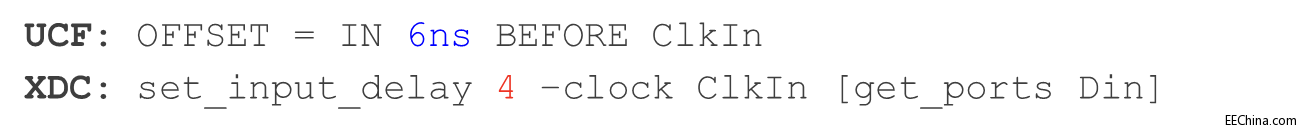

以最基礎的SDR系統同步介面來舉例。輸入側的設定,UCF用的是OFFSET = IN,而XDC則是set_input_delay 。

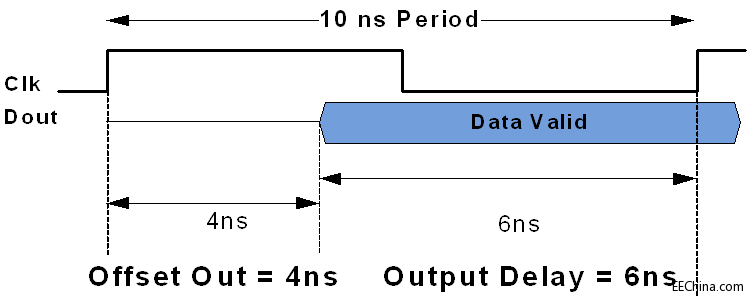

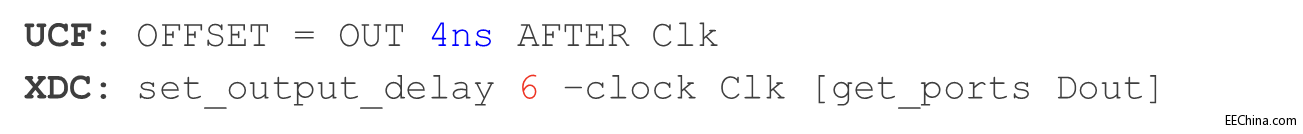

輸出側的設定,UCF用的是OFFSET =OUT,而XDC則是set_output_delay 。

如果需要從舊設計的UCF約束轉到XDC約束,可以參考上述例子。以一個取樣週期來看,UCF中與XDC中設定的介面約束值加起來正好等於一個週期的值。

小結

這一系列《XDC約束技巧》的文章至此暫時告一段落。其實讀懂這幾篇涵蓋了時鐘、CDC以及介面約束的短文,基本上已經足夠應對絕大多數的FPGA設計約 束問題。當然在這麼短的篇幅內,很多問題都無法更加深入地展開,所以也提醒讀者,需要關注文中推薦的各類Xilinx 官方文件,以及Vivado本身自帶的幫助功能與模板。

希望各位能從本文中吸取經驗,少走彎路,儘快地成為Vivado和XDC的資深使用者,也希望本文能真正為您的設計添磚加瓦,達到事半功倍的效果。

3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1 3_201504272135101qzL1

3_201504272135101qzL1