verilog學習()關於同步狀態機

阿新 • • 發佈:2018-11-09

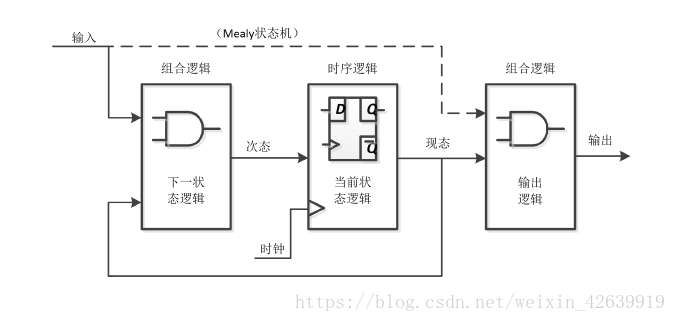

狀態機是許多數字系統的核心部件,是一類重要的時序邏輯電路。通常包括三個部分:一是下一個狀態的邏輯電路,二是儲存狀態機當前狀態的時序邏輯電路,三是輸出組合邏輯電路。通常,狀態機的狀態數量有限,稱為有限狀態機(FSM)。由於狀態機所有觸發器的時鐘由同一脈衝邊沿觸發,故也稱之為同步狀態機。

根據狀態機的輸出訊號是否與電路的輸入有關分為Mealy 型狀態機和Moore 型狀態機。電路的輸出訊號不僅與電路當前狀態有關,還與電路的輸入有關,稱為Mealy 型狀態機,而電路的輸出僅僅與各觸發器的狀態,不受電路輸入訊號影響或無輸入,稱為

Moore 型狀態機。其標準模型如下所示:

狀態機的描述通常有三種方法,稱為一段式狀態機,二段式狀態機和三段式狀態機。狀態機的描述通常包含以下四部分:

1)利用引數定義語句parameter 描述狀態機各個狀態名稱,即狀態編碼。狀態編碼通常有很多方法包含自然二進位制編碼,One-hot 編碼,格雷編碼碼等;

2)用時序的always 塊描述狀態觸發器實現狀態儲存;

3)使用敏感表和case 語句(也採用if-else 等價語句)描述狀態轉換邏輯;

4)描述狀態機的輸出邏輯。