zedboard通過BRAM實現PS和PL的簡單通訊

使用Block Memory進行PS和PL的資料互動或者資料共享,通過zynq PS端的Master GP0埠向BRAM寫資料,然後再通過PS端的Mater GP1把資料讀出來,將結果列印輸出到串列埠終端顯示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。

本文所使用的開發板是zedboard

PC 開發環境版本:Vivado 2016.2 Xilinx SDK 2016.2

---------------------

作者:wangdaling

來源:CSDN

原文:https://blog.csdn.net/rzjmpb/article/details/50365915 https://blog.csdn.net/rzjmpb/article/details/50365915

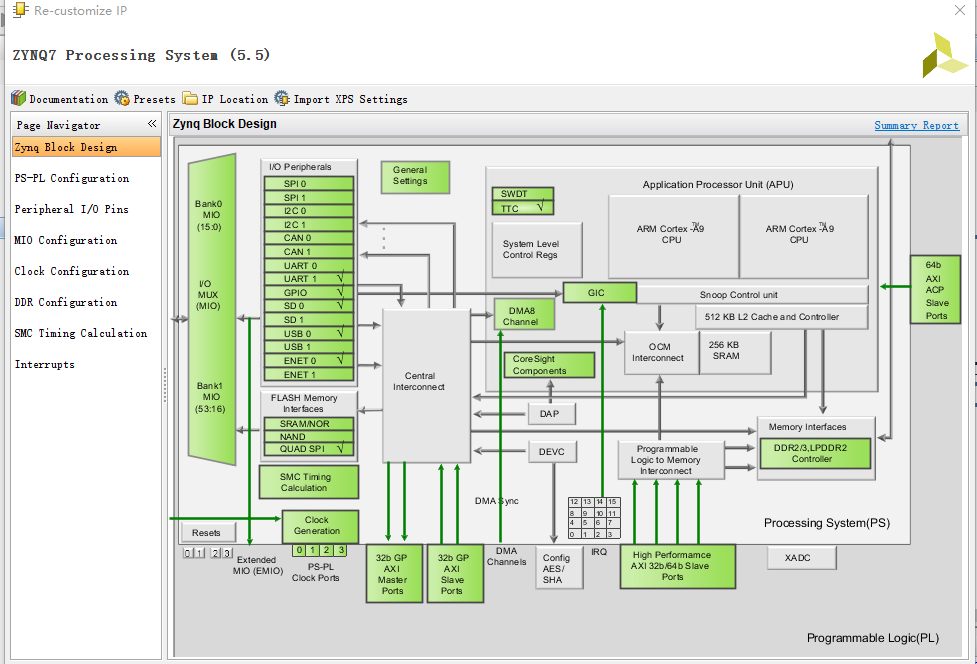

一、實現的結構原理圖

1、PL端硬體架構搭建

新建工程後在Create Block Design中新增IP,點選新增IP的按鈕後在彈出的搜尋框中搜索ZYNQ時新增PS,搜尋BRAM時新增AXI BRAM Controller 和Block Memory Generator,然後對PS中的相應介面做引數設定

2、軟體SDK中的程式碼如下:

#include <stdio.h>

#include "platform.h"

#include "xparameters.h"

#include"xparameters_ps.h"

#include"xil_printf.h"

#include"xil_io.h"

//#define DDR_BASEARDDR XPAR_DDR_MEM_BASEADDR+0x10000000

int main()

{

init_platform();

int i;

int rev;

xil_printf("-----The test is start...\n\r");

for(i=0;i<15;i++)

{

Xil_Out32(XPAR_BRAM_0_BASEADDR+i*4,0x10000000+i);

}

for(i=0;i<15;i++)

{

rev=Xil_In32(XPAR_BRAM_0_BASEADDR+i*4);

xil_printf("the address at %x data is: %x \n\r",XPAR_BRAM_0_BASEADDR+i*4,rev);

}

xil_printf("-----The test is end!-------\n\r");

cleanup_platform();

return 0;

}

3、編譯軟體部分的程式碼,

4、將zedboard 板子的JTAG和PROG的埠與PC電腦端相連

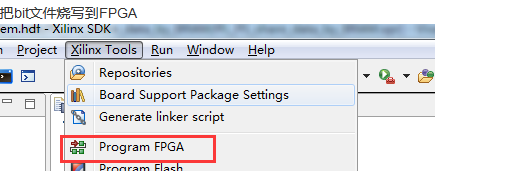

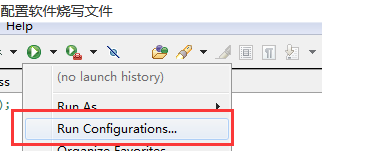

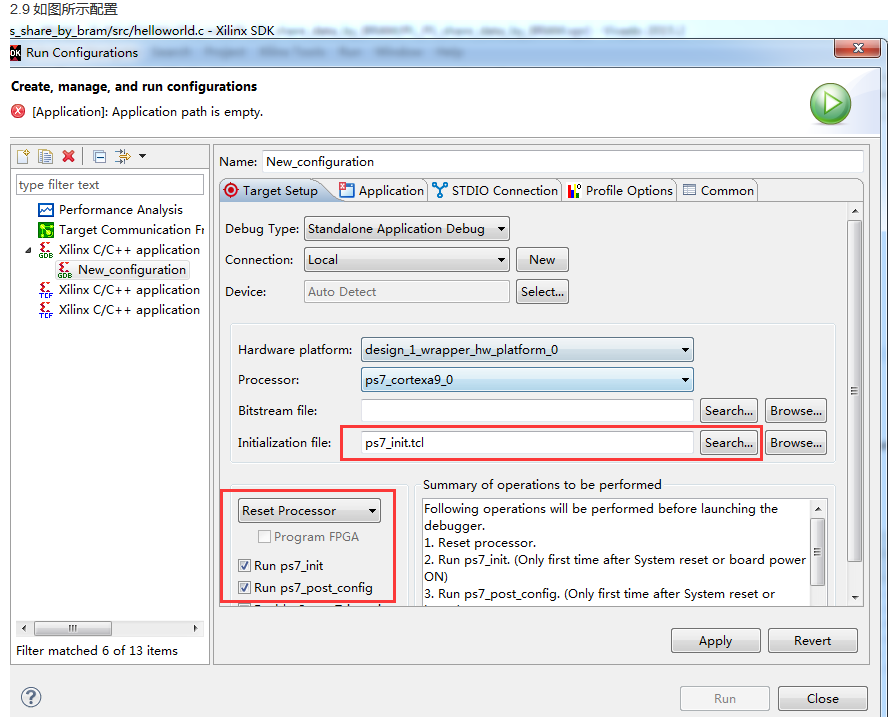

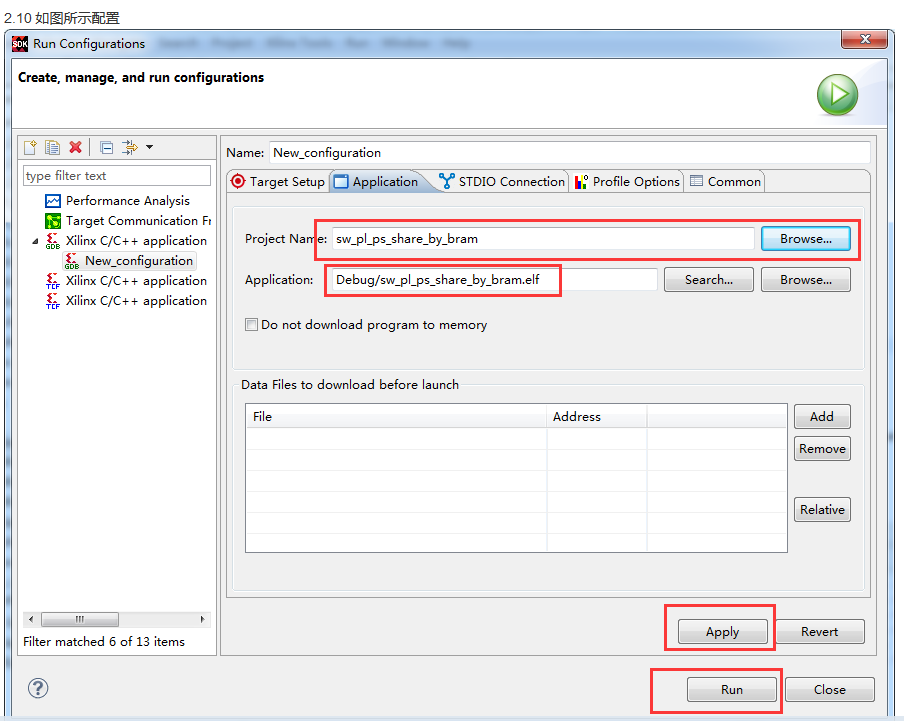

5、然後program FPGA(從硬體部分生成的bitstream),run configuration,run