7 Serial Configuration 理解(二)

*Serial Configuration Mode

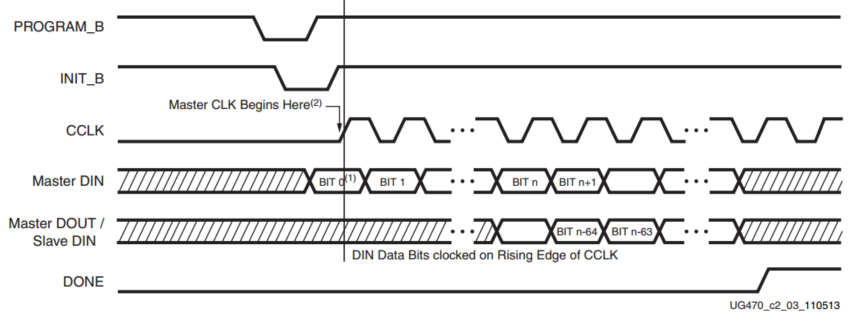

序列配置模式分為:Master Serial 和 Slave Serial (如下圖)兩類; 兩者的區別在與CCLK的輸入輸出方向;主動模式下為輸出方向,從模式下為輸入方向;

Slave Serial模式最典型應用於序列菊花鏈或者用外部控制器和CPLD配置單個FPGA。Master Serial模式中,CCLK作為輸出;

在Slave Serial 和 Master Serial 模式的時序圖如下。Master DIN輸入的第一個BIT0 代表第一個BYTE的最高位。

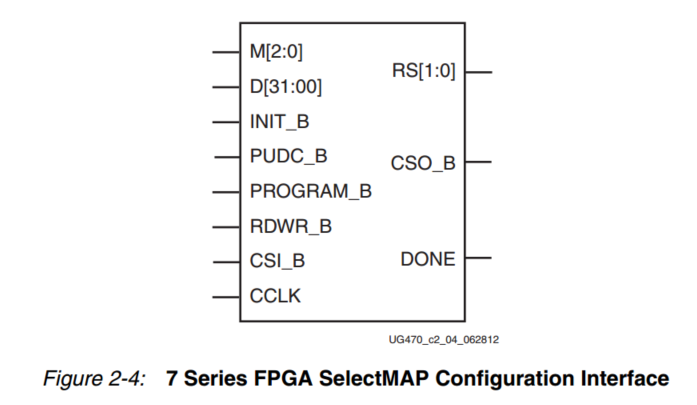

*SelectMAP configuration Mode

SelectMap配置介面提供了8/16/32bit位寬的雙向資料匯流排到7系列FPGA的配置邏輯中,可以用來配置和回讀。回讀只能用與Slave SelectMap模式中。匯流排位寬是自動檢測的。

SelectMap模式中支援多種配置方法:

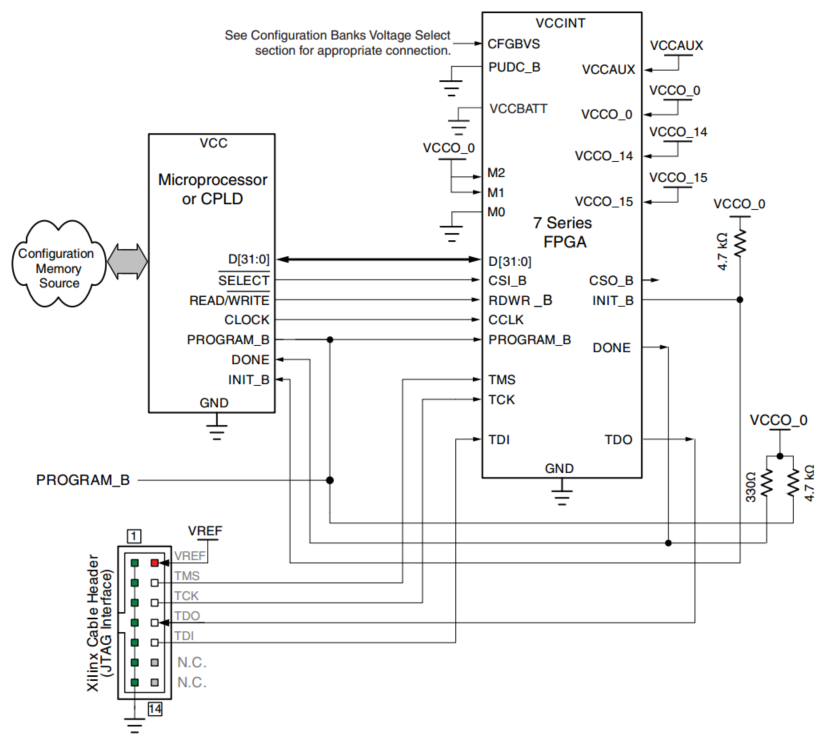

1.單器件Slave SelectMap:(如下圖) 外部控制器/CPLD提供時鐘和資料,通過Slave SelectMap介面配置FPGA。 Master SelectMap與Slave SelectMap相比,後者是首選模式。

2.多器件菊花鏈SelectMap匯流排:多個FPGA序列配置來自一個flash或者處理器的不同的映象;

3.多器件協同SelectMap:多個FPGA並行配置來自一個flash或處理器的相同映象。當使用平行flash時,建議使用BPI配置模式。

reference : UG626

reference: XAPP583

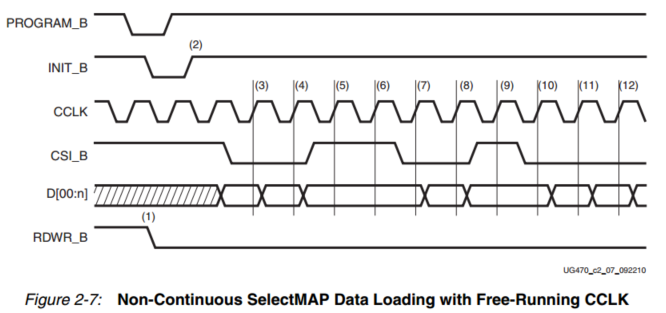

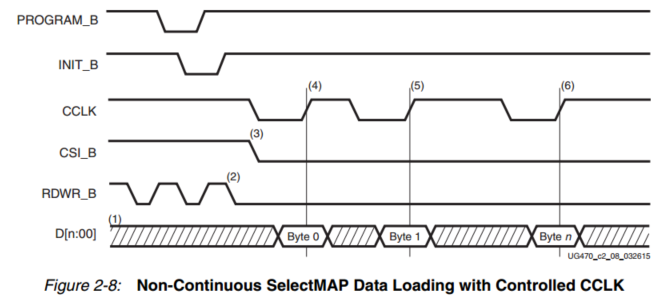

SelectMap支援連續資料寫入(如下圖)和非連續資料寫入;非連續資料寫入分為:CSI_B選擇控制和CCLK中斷控制。

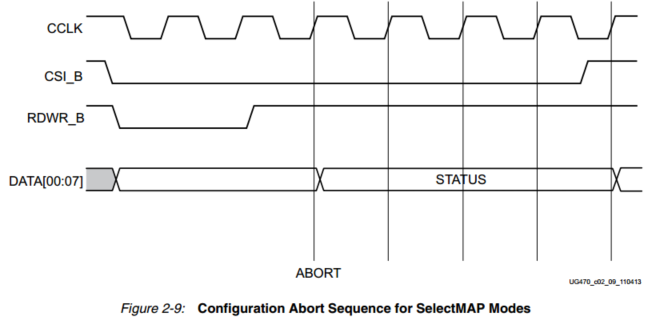

*SelectMAP ABORT

在SelectMAP配置和回讀中,當CCLK取樣下,RDWR_B改變同時CSI_B斷言,將會出現中斷。在一個配置中斷中,通過四拍CCLK將內部狀態輸出到D[4:7]管腳上,其他D管腳保持拉高狀態。在中斷完成後,使用者可以重新同步配置邏輯,繼續配置。

配置中斷序列:

1.配置順序正常開始。

2.選擇器件,將RDWR_B引腳拉高,同步到CCLK(CSI_B置為低電平)。

3.如果RDWR_B保持設定為讀控制(邏輯高電平),FPGA會將狀態字驅動到資料引腳上。

4. ABORT持續四個時鐘週期,並更新狀態。

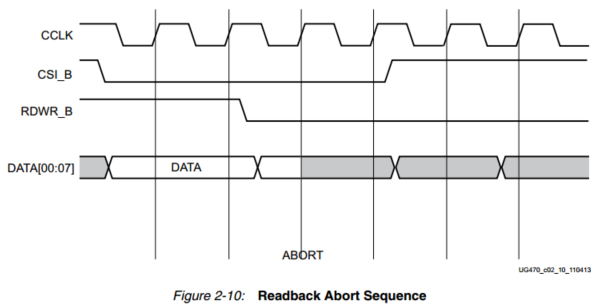

回讀中斷序列:

1.回讀序列正常開始。

2.當器件被選中時,將RDWR_B引腳拉低至CCLK同步(CSI_B置為低電平)。

3.當CSI_B被置為無效時,ABORT結束。

注:回讀期間的ABORT後面沒有狀態字,因為RDWR_B訊號被設定為寫控制(D 引腳是輸入)。

中斷狀態字:

在配置中斷下,器件驅動狀態字到D[4:7]引腳;其他引腳保持為高。

在最後一個週期之後,可以重新載入同步字以建立資料對齊。

ABORT後有兩種方法可以恢復配置或回讀:

•ABORT完成後,裝置可以重新同步。

•可以通過任意時間將PROGRAM_B置為低電平來複位器件。

要重新同步裝置,必須取消置位CSI_B然後再重新置位。 通過傳送ABORT發生時正在進行的最後一個配置或回讀資料包,可以恢復配置或回讀。 或者,可以從頭重新開始配置或回讀。

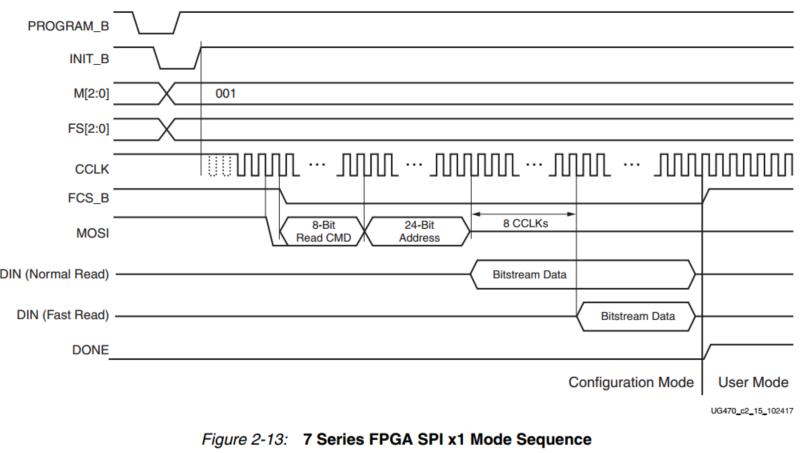

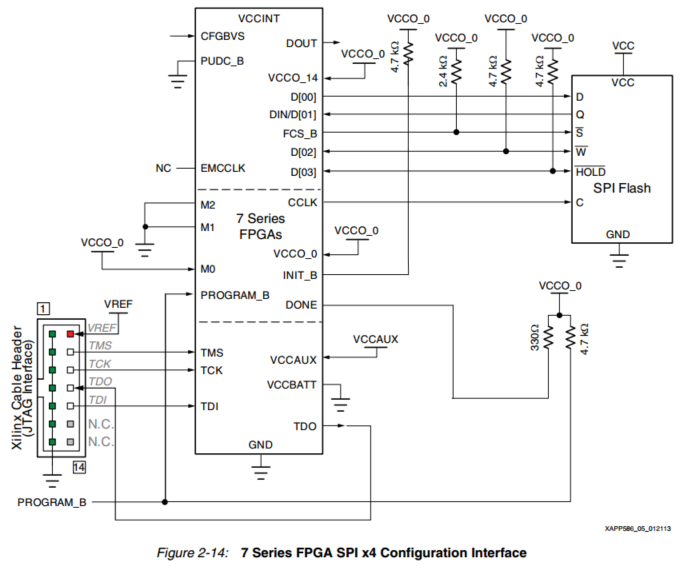

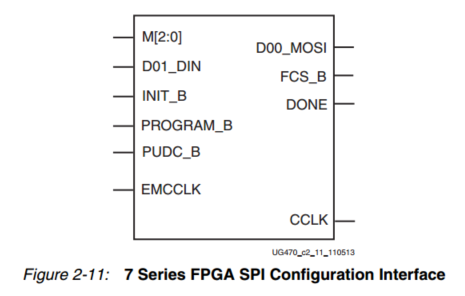

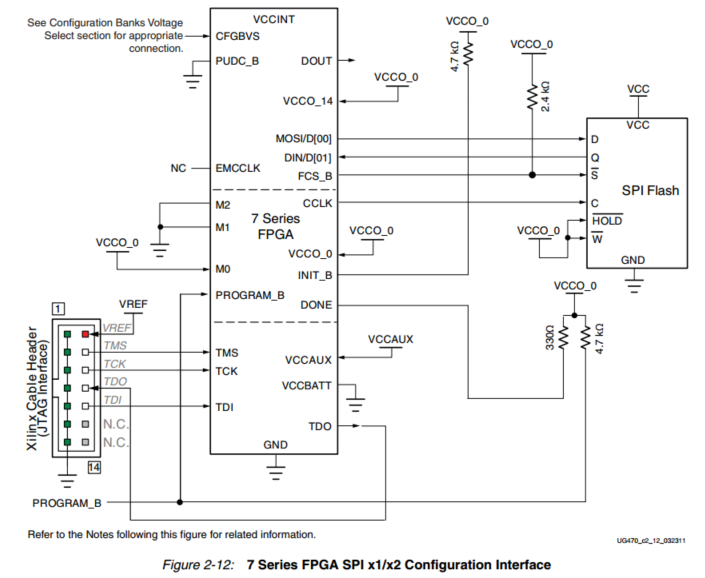

*Master SPI Configuration Mode

主SPI配置模式允許使用低引腳數,工業標準SPI快閃記憶體器件進行位元流儲存。 FPGA支援直接連線SPI快閃記憶體器件的事實上標準的四引腳介面,用於讀取儲存的位元流。

7系列FPGA主SPI配置模式 ,可以從支援x2和x4快速輸出讀操作的SPI器件讀取, 這些輸出模式比標準的1位SPI介面成比例地快。 此外,負邊沿時鐘模式可用於更好地利用整個時鐘週期並允許更高的配置速度。 還支援超過128 Mb的SPI快閃記憶體密度,需要32位定址。

SPI x1/x2 連線是相同的,因為x2模式使用D00_MOSI引腳作為雙用途資料輸入/輸出引腳。

DOUT應連線到下游FPGA的DIN,以實現菊花鏈SPI x1配置模式。 x2或x4 SPI模式不支援菊花鏈。

對於從快閃記憶體到FPGA的資料路徑,應考慮串聯電阻,以最大限度地減少過沖。 可以通過仿真確定適當的電阻值。