intel電源管理技術中I2C和SVID

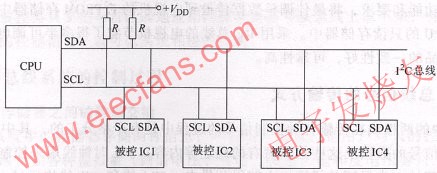

1.I2C匯流排架構圖:

2.Gemini Lake 平臺所支援的PMIC 是哪種型別?

POR 是SVID PMIC, i2c PMIC 會影響效能。

3.SerialVID, 總共有三個訊號線 時鐘(clock) , 訊號(data) Alert (報警) 組成的。 是一種串行同步介面。

4.VID(Voltage Identification,電壓識別)是一種電壓識別技術,裝上不同的CPU,會產生不同的電壓。

VID可分壓PVID(並行VID)和SVID(序列VID)。

VID(Voltage Identification)是一種電壓識別技術,可分為PVID(並行VID)和SVID(序列VID)。

在AMD早期和INTEL 5系列晶片組之前,都採用PVID,其基本原理就是在CPU上設定了4-8個VID 識別腳,並通過預設在這些識別腳上的高低電平值,形成一組VID識別訊號,這些訊號傳輸到CPU供電電路中的電源管理晶片後,電源管理晶片根據所得到的VID訊號使CPU供電電路輸出的電壓與預設的VID所代表的值一致。

AMD從AM2+ CPU開始,CPU包含兩部分電壓,一是CPU的核心電壓,另一是CPU內整合的北橋的電壓。並行VID控制模組無法在同一時間內非同步控制這兩種電壓,除非再提供一組並行VID控制CPU中的北橋電壓,但這樣會增加晶片的複雜度。於是AMD率先推出新一代電壓調節模組規範,採用序列VID(SVID)模式來解決這一問題。序列VID是一種匯流排型別的協議。從硬體上來看,所需要的外部介面由以前的多個VIDXX引腳變成SVC(序列時鐘)、SVD(序列資料)兩個引腳,簡單了很多。不過,序列VID的實現需要軟體的配合。

傳統行動式筆記本、一體機、桌上型電腦等一般都是採用intel的技術架構。其待機、休眠、高負載環境下的電壓調節都有一套成熟的應用方案,英特爾從6系列平臺開始,匯入VR12(VoltageRegulator電壓調節)規範,也就是SVID(SerialVoltageIdentification串聯電壓識別)模式,通過CPU自身SVID匯流排偵測CPU的電壓,即CPU作為PMBUS(PowerManagementBus電源管理匯流排)的主裝置,SVID模組通過DATA(資料)和CLK(時鐘)匯流排向VRM(VoltageRegulatorModule電源管理模組)晶片發出呼叫,等待著VRM晶片來讀取電壓設定資訊。當VRM晶片對CPU內SVID模組的呼叫做出應答,並讀出電壓設定資訊,CPU主供電VCORE(VoltageCore核電壓)產生,之後依據CPU電壓來調控PWM(PulseWidthModulation脈寬調製)供電的相數。硬體電路和通訊機制都已經形成一種固定機制,每一系列的CPU主機板必須相容相應的PWM控制器,由於CPU和VRM必須通過SVID匯流排進行通訊,而SVID是一種匯流排工作模式,整個鏈路需要軟體的配合,硬體成本較高。

VID調節CPU電壓

VID(Voltage Identification,電壓識別)是一種電壓識別技術,裝上不同的CPU,會產生不同的電壓。VID可分壓PVID(並行VID)和SVID(序列VID)。

在AMD早期和INTEL 5系列晶片組(HM55等)之前,都是屬於PVID,其基本原理就是在CPU上設定了4-8個VID 識別腳,並通過預設在這些識別腳上的高低電平值,形成一組VID識別訊號,當VID識別腳上為高電平時,則為二進位制的1狀態,當VID識別腳上為低電平時,則為二進位制的0狀態。根據這些1與0的組合,就形成了一組最基本的機器語言訊號,並由CPU傳輸到CPU供電電路中的電源管理晶片,電源管理晶片根據所得到的VID訊號,調整輸出脈衝訊號的佔空比,迫使CPU供電電路輸出的直流電壓與預設的VID所代表的值一致。

INTEL公司為其不同時間生產的各款CPU制定了相應的電壓調節模組(Voltage Regulation Model——VRM)設計規範,從Prescott核心微處理器開始,電壓調節規範改用VRD(Voltage Regulation Down)來命名,在膝上型電腦中,使用的是移動電壓配置IMVP(Intel Mobile Voltage Positioning),各版本供電設計規範中的VID位數、電壓調節精度和電壓調節範圍都各不相同。

這種模式的VID,可以通過裝入假負載把CPU電壓”騙”出來:當裝上假負載後,將VID0-VID7其中的一個或多個VID訊號接地,此時電源IC的VID0-VID7引腳上就得到了新的電壓組合,電源IC會根據這個不同的組合,控制發出相應的電壓。也就是說,讓CPU供電晶片誤以為是真CPU裝入。

由下表可以看出,伴隨著VRM/VRD/IMVP標準的增高,VID位數在逐漸增加,電壓調節精度變小,電壓範圍也隨之變小。

使用PVID的晶片,引腳上必然有VID*訊號,如下圖ISL6262晶片中37-43腳:

AMD從AM2+ CPU開始,CPU包含著兩部分電壓(AMD稱之為Dual-Plane),一個是CPU的核心電壓,一個是CPU內整合的北橋的電壓,一組並行VID控制模組無法在同一時間內非同步控制這兩種電壓,除非再提供一組並行VID控制CPU中的北橋電壓,但這樣會顯得比較複雜。於是AMD率先推出新一代電壓調節模組規範,採用序列VID(SVID)模式來解決這一問題。序列VID是一種匯流排型別的協議。從硬體上來看,所需要的外部介面由以前的VID0~VID5共6個變成SVC(序列時鐘)、SVD(序列資料)兩個,可以說是簡單了很多。不過,由於序列VID是一種匯流排工作模式,所以需要軟體的配合,但同時也意味著後期調整的可操作性會更強。前期大部分AMD主機板為了相容AM2/AM2+/AM3,採用了PVI/SVI相容的PWM控制器。

英特爾在5系列平臺搭配的Core i3/i5/i7 CPU集成了顯示核心,為了更好地控制這兩組電源,因此提供了兩組PVID介面以分別控制CPU的核心電壓和顯示核心電壓,這兩組電壓都符合英特爾 VRD11.1的規範,這顯然是稍顯複雜了一些。

英特爾從6系列平臺開始,匯入VRD12規範,也就是序列VID模式,和AMD SVID模式如出一轍。INTEL平臺的SVID有三根線:SVD(序列VID資料),(SVC序列VID時鐘),ALERT#(警示訊號)。採用SVID的電源管理晶片,引腳上必須有這幾個訊號。如下圖晶片4-6腳:

下圖為INTEL平臺SVID訊號波形截圖,黃色線為SVC訊號,藍色線為SVD訊號。

根據INTEL 6系列晶片組收據手冊得知,CPU是在獲得了PROCPWRGD後,才發出SVID訊號,INTEL 6系列標準時序圖截圖:

所以,新的6系列及以後的主機板,如果出現沒有CPU供電的情況,應使用示波器抓取CPU是否發出SVID訊號給電源管理晶片。

如果沒有波形,則應按照時序圖先查CPU是否獲得PROCPWRGD這個高電平訊號,若PROCPWRGD不正常,需要追查PCH的相關PG訊號,以及PCH是否追查讀取BIOS等。

另外,CPU內整合顯示卡的供電是在CPU核心供電出來之後才產生。同樣是由SVID控制。