APB匯流排學習彙總

APB簡介

APB(Advanced Peripheral Bus),外圍匯流排。APB屬於AMBA 3 協議系列,它提供了一個低功耗的介面, 並降低了介面的複雜性。 APB介面用在低頻寬和不需要高效能匯流排的外圍裝置上。 APB是非流水線結構,所有的訊號僅與時鐘上升沿相關,這樣就可以簡化APB外圍裝置的設計流程,每個傳輸至少耗用兩個週期。APB可以與AMBA高階高效能匯流排(AHB-Lite) 和AMBA 高階可擴充套件介面 (AXI)連線。

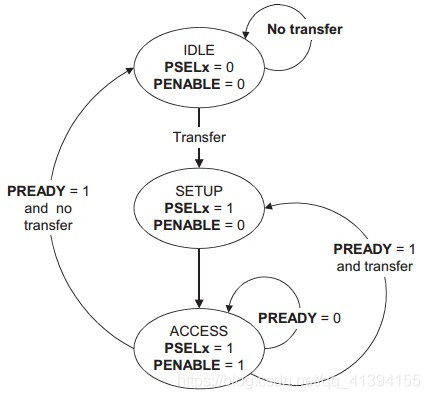

APB主要用於低頻寬的周邊外設之間的連線,例如UART、1284等,它的匯流排架構不像AHB支援多個主模組,在APB裡面唯一的主模組就是APB 橋。其特性包括:兩個時鐘週期傳輸;無需等待週期和迴應訊號;控制邏輯簡單,只有四個控制訊號。APB上的傳輸可以用狀態圖來說明。

Operating states

a) 系統初始化為IDLE狀態,此時沒有傳輸操作,也沒有選中任何從模組。

b) 當有傳輸要進行時,PSELx=1,PENABLE=0,系統進入SETUP狀態,並只會在SETUP 狀態停留一個週期。當PCLK的下一個上升沿時到來時,系統進入ENABLE 狀態。

c) 系統進入ENABLE狀態時,維持之前在SETUP 狀態的PADDR、PSEL、PWRITE不變,並將PENABLE置為1。傳輸也只會在ENABLE狀態維持一個週期,在經過SETUP與ENABLE狀態之後就已完成。之後如果沒有傳輸要進行,就進入IDLE狀態等待;如果有連續的傳輸,則進入SETUP狀態。

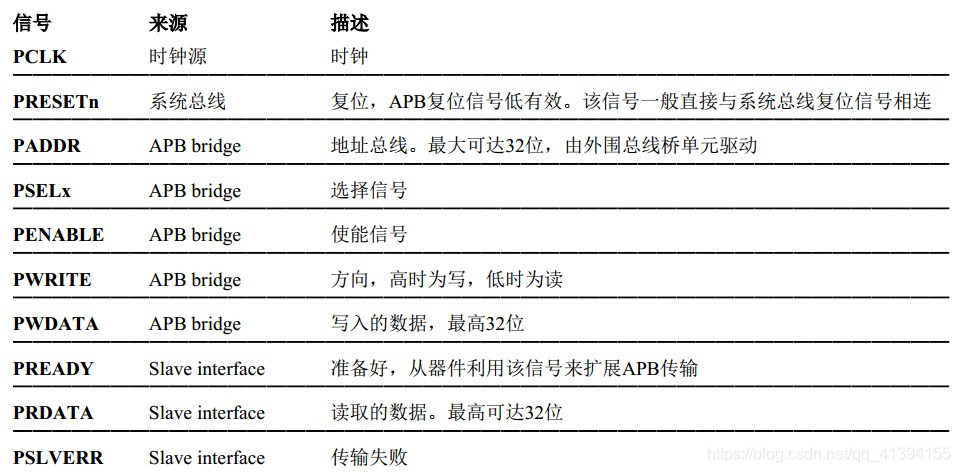

訊號描述

下表給出了APB的訊號。APB的支援最大32-bit的資料位寬。APB協議有兩個獨立的資料通道,讀通道和寫通道,由於APB的兩個通道沒有自己的handshake訊號(vaild/ ready),因此兩個通道不會同時使用。

APB signal descriptions

除了上表的訊號外,APB還有兩個訊號介面:

PPROT: 保護型別,分為 normal, privileged, secure, data/instruction 訪問。

PSTRRB: 寫選通訊號,指示哪個位元組是有效的資料,PSTRB與PWDATA之間的關係為PSTRB[n] <--> PWDATA[(8n+7):(8n)]

傳輸

寫傳輸

寫傳輸包括兩種型別:無等待狀態和有等待狀態

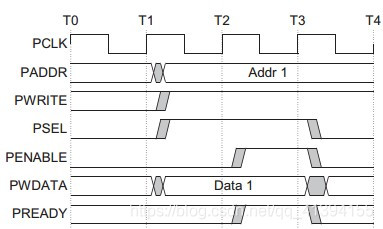

無等待狀態

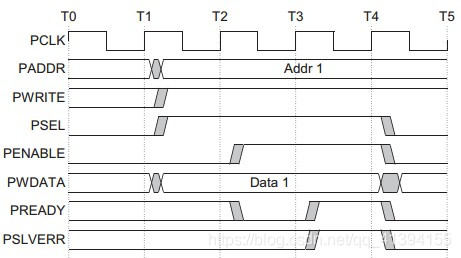

下圖顯示了一個基本的無等待狀態的寫傳輸。

Write transfer with no wait states

地址、寫入資料、寫入訊號和選擇訊號都在時鐘上升沿後改變。第一個時鐘週期叫做Setup phase。 下一個時鐘沿後使能訊號PENABLE被置位,表示Access phase就位。地址、資料和控制訊號在Access phase期間有效。傳輸在該週期後結束。使能訊號PENABLE, 在傳輸結束後清空。 選擇訊號PSELx同樣被置低,除非緊接著下一傳輸開始。

有等待狀態

下圖展示了 PREADY 訊號是如何擴充套件了從器件的傳輸。

Write transfer with wait states

在Access phase期間,當PENABLE為高,傳輸可以通過拉低PREADY來擴充套件傳輸。下述訊號仍舊不變:• 地址: PADDR• 寫訊號: PWRITE• 選擇訊號: PSEL• 使能訊號:PENABLE• 寫入的資料: PWDATA.

讀傳輸

讀傳輸包括以下兩種型別:無等待狀態和有等待狀態

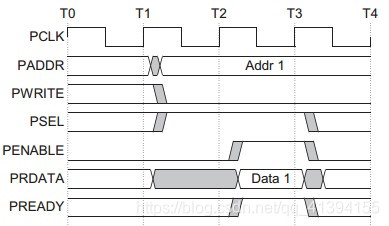

無等待狀態

下圖顯示了一個讀傳輸的無等待狀態的時序圖。從器件必須在讀傳輸結束前提供資料。

Read transfer with no wait states

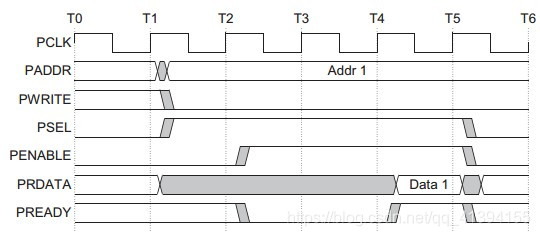

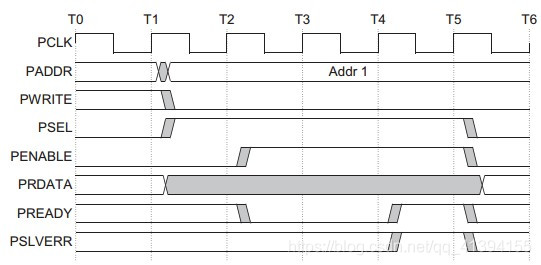

有等待狀態

下圖顯示了訊號是如何擴充套件傳輸的。如果在Access phase期間PREADY訊號拉低,則傳輸被擴充套件。但下述訊號不變:• 地址: PADDR• 寫訊號: PWRITE• 選擇訊號: PSEL• 使能訊號: PENABLE.

圖中顯示瞭如何使用PREADY訊號來新增兩個週期,你也可以新增數個週期。

Read transfer with wait states

錯誤響應

使用PSLVERR來指示APB傳輸錯誤。當PSEL, PENABLE以及PREADY 都為高時,PSLVERR才在最後一個週期進行判斷。 當任何一個PSEL, PENABLE或者PREADY為低時,你可以將PSLVERR拉低,這是推薦,並不是強制要求。 收到一個錯誤後,可能或不可能改變外圍器件的狀態。 APB外圍裝置不要求必須支援PSLVERR引腳,當不使用該引腳時,應被置低。

寫傳輸失敗的例子。

Example failing write transfer

讀傳輸同樣可以使用錯誤響應,下圖便是一個錯誤響應的例子

PSLVERR對映:

AXI橋接到APB: AXI的RRESP/BRESP = APB的SLVERR(read: PSLVERR -> RRESP[1], write: PSLVERR -> BRESP[1])

AHB橋接到APB: PSLVERR被對映到HRESP = ERROR(PSLVERR -> HRESP[0])

操作狀態

下圖給出了 APB的操作流程

State diagram

狀態機按照下面的狀態執行:

IDLE 這是預設的APB狀態

SETUP 當傳輸被請求時,匯流排進入SETUP狀態,選擇訊號 PSELx,被置位。匯流排僅在SETUP 狀態停留一個時鐘週期,並在下一個時鐘週期進入ACCESS狀態

ACCESS 使能訊號PENABLE, 在ACCESS狀態中置位。在傳輸從SETUP狀態到ACCESS狀態轉變的過程中address, write, select和write data訊號必須保持不變。從ACCESS狀態退出,由從器件的PREADY 訊號控制:a) 如果PREADY 為低,保持ACCESS狀態。b)如果PREADY 為高,則退出ACCESS狀態,如果此時沒有其它傳輸請求,匯流排返回IDLE狀態,否則進入SETUP狀態。