AXI匯流排學習彙總

本文轉自:http://www.cnblogs.com/lkiller/p/4773235.html

0.緒論

AXI是高階擴充套件介面,在AMBA3.0中提出,AMBA4.0將其修改升級為AXI4.0。AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream

AXI4.0-lite是AXI的簡化版本,ACE4.0 是AXI快取一致性擴充套件介面,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA進行以資料為主導的大量資料的傳輸應用。

1.簡介

1.1 關於AXI協議

AMBA AXI協議支援支援高效能、高頻率系統設計。

適合高頻寬低延時設計

無需複雜的橋就能實現高頻操作

能滿足大部分器件的介面要求

適合高初始延時的儲存控制器

提供互聯架構的靈活性與獨立性

向下相容已有的AHB和APB介面

關鍵特點:

分離的地址/控制、資料相位

使用位元組線來支援非對齊的資料傳輸

使用基於burst的傳輸,只需傳輸首地址

分離的讀、寫資料通道,能提供低功耗DMA

支援多種定址方式

支援亂序傳輸

允許容易的新增暫存器級來進行時序收斂

1.2 AXI架構

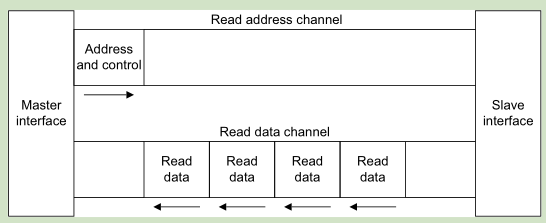

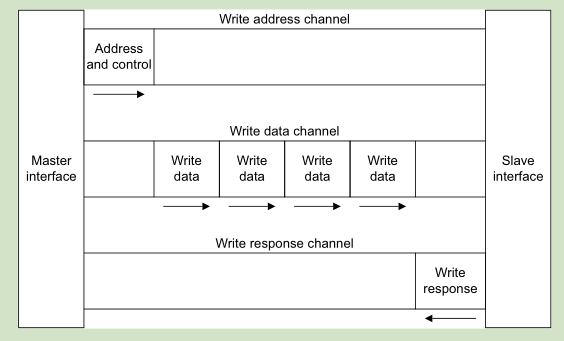

AXI協議是基於burst的傳輸,並且定義了以下5個獨立的傳輸通道:讀地址通道、讀資料通道、寫地址通道、寫資料通道、寫響應通道。

地址通道攜帶控制訊息用於描述被傳輸的資料屬性,資料傳輸使用寫通道來實現“主”到“從”的傳輸,“從”使用寫響應通道來完成一次寫傳輸;讀通道用來實現資料從“從”到“主”的傳輸。

圖 1-1 讀架構

- 1

圖 1-2 寫架構

- 1

AXI是基於VALID/READY的握手機制資料傳輸協議,傳輸源端使用VALID表明地址/控制訊號、資料是有效的,目的端使用READY表明自己能夠接受資訊。

讀/寫地址通道:讀、寫傳輸每個都有自己的地址通道,對應的地址通道承載著對應傳輸的地址控制資訊。

讀資料通道:讀資料通道承載著讀資料和讀響應訊號包括資料匯流排(8/16/32/64/128/256/512/1024bit)和指示讀傳輸完成的讀響應訊號。

寫資料通道:寫資料通道的資料資訊被認為是緩衝(buffered)了的,“主”無需等待“從”對上次寫傳輸的確認即可發起一次新的寫傳輸。寫通道包括資料匯流排(8/16…1024bit)和位元組線(用於指示8bit 資料訊號的有效性)。

寫響應通道:“從”使用寫響應通道對寫傳輸進行響應。所有的寫傳輸需要寫響應通道的完成訊號。

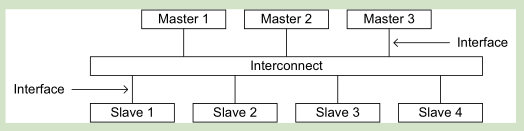

圖 1-3 介面與互聯

- 1

AXI協議提供單一的介面定義,能用在下述三種介面之間:master/interconnect、slave/interconnect、master/slave。

可以使用以下幾種典型的系統拓撲架構:

共享地址與資料匯流排

共享地址匯流排,多資料匯流排

multilayer多層,多地址匯流排,多資料匯流排

在大多數系統中,地址通道的頻寬要求沒有資料通道高,因此可以使用共享地址匯流排,多資料匯流排結構來對系統性能和互聯複雜度進行平衡。

暫存器片(Register Slices):

每個AXI通道使用單一方向傳輸資訊,並且各個通道直接沒有任何固定關係。因此可以可以在任何通道任何點插入暫存器片,當然這會導致額外的週期延遲。

使用暫存器片可以實現週期延遲(cycles of latency)和最大操作頻率的折中;使用暫存器片可以分割低速外設的長路徑。

2.訊號描述

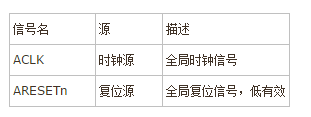

表 2-1 全域性訊號

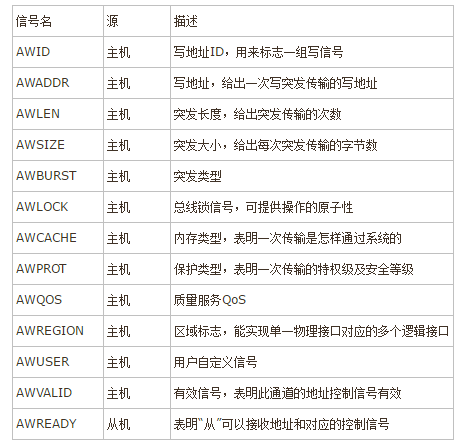

表 2-2 寫地址通道訊號

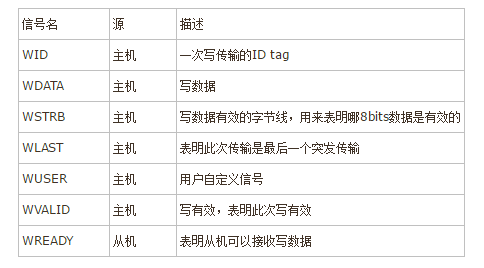

表 2-3 寫資料通道訊號

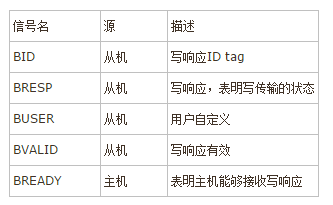

表 2-4 寫響應通道訊號

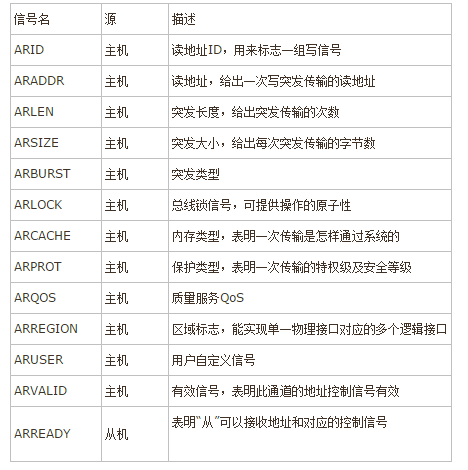

表 2-5 讀地址通道訊號

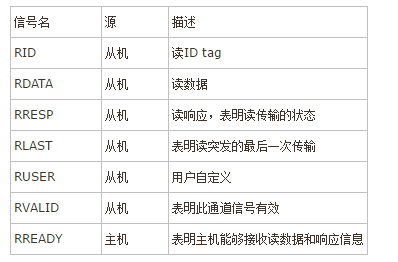

表 2-6 讀資料通道訊號

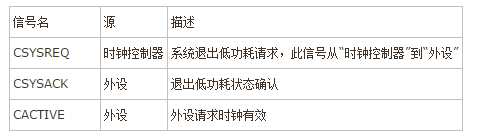

表 2-7 低功耗介面訊號

3.訊號介面要求

3.1時鐘復位

時鐘

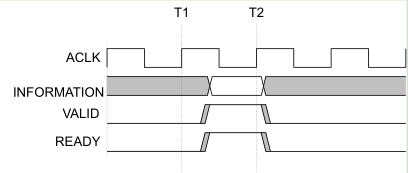

每個AXI元件使用一個時鐘訊號ACLK,所有輸入訊號在ACLK上升沿取樣,所有輸出訊號必須在ACLK上升沿後發生。

復位

AXI使用一個低電平有效的復位訊號ARESETn,復位訊號可以非同步斷言,但必須和時鐘上升沿同步去斷言。

復位期間對介面有如下要求:①主機介面必須驅動ARVALID,AWVALID,WVALID為低電平;②從機介面必須驅動RVALID,BVALID為低電平;③所有其他訊號可以被驅動到任意值。

在復位後,主機可以在時鐘上升沿驅動ARVALID,AWVALID,WVALID為高電平。

3.2基本讀寫傳輸

握手過程

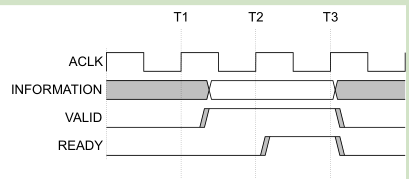

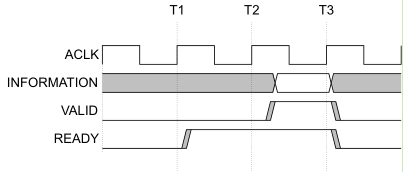

5個傳輸通道均使用VALID/READY訊號對傳輸過程的地址、資料、控制訊號進行握手。使用雙向握手機制,傳輸僅僅發生在VALID、READY同時有效的時候。下圖是幾種握手機制:

圖 3-1 VALID before READY 握手

圖 3-2 READY before VALID 握手

圖 3-3 VALID with READY 握手

通道訊號要求

通道握手訊號:每個通道有自己的xVALID/xREADY握手訊號對。

寫地址通道:當主機驅動有效的地址和控制訊號時,主機可以斷言AWVALID,一旦斷言,需要保持AWVALID的斷言狀態,直到時鐘上升沿取樣到從機的AWREADY。AWREADY預設值可高可低,推薦為高(如果為低,一次傳輸至少需要兩個週期,一個用來斷言AWVALID,一個用來斷言AWREADY);當AWREADY為高時,從機必須能夠接受提供給它的有效地址。

寫資料通道:在寫突發傳輸過程中,主機只能在它提供有效的寫資料時斷言WVALID,一旦斷言,需要保持斷言狀態,知道時鐘上升沿取樣到從機的WREADY。WREADY預設值可以為高,這要求從機總能夠在單個週期內接受寫資料。主機在驅動最後一次寫突發傳輸是需要斷言WLAST訊號。

寫響應通道:從機只能它在驅動有效的寫響應時斷言BVALID,一旦斷言需要保持,直到時鐘上升沿取樣到主機的BREADY訊號。當主機總能在一個週期內接受寫響應訊號時,可以將BREADY的預設值設為高。

讀地址通道:當主機驅動有效的地址和控制訊號時,主機可以斷言ARVALID,一旦斷言,需要保持ARVALID的斷言狀態,直到時鐘上升沿取樣到從機的ARREADY。ARREADY預設值可高可低,推薦為高(如果為低,一次傳輸至少需要兩個週期,一個用來斷言ARVALID,一個用來斷言ARREADY);當ARREADY為高時,從機必須能夠接受提供給它的有效地址。

讀資料通道:只有當從機驅動有效的讀資料時從機才可以斷言RVALID,一旦斷言需要保持直到時鐘上升沿取樣到主機的BREADY。BREADY預設值可以為高,此時需要主機任何時候一旦開始讀傳輸就能立馬接受讀資料。當最後一次突發讀傳輸時,從機需要斷言RLAST。

通道間關係

AXI協議要求通道間滿足如下關係:

寫響應必須跟隨最後一次burst的的寫傳輸

讀資料必須跟隨資料對應的地址

通道握手訊號需要確認一些依耐關係

通道握手訊號的依耐關係

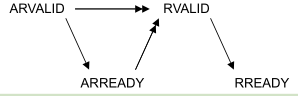

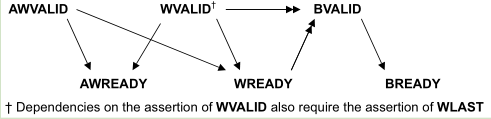

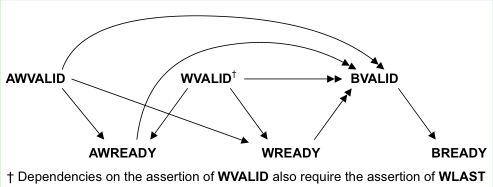

為防止死鎖,通道握手訊號需要遵循一定的依耐關係。①VALID訊號不能依耐READY訊號。②AXI介面可以等到檢測到VALID才斷言對應的READY,也可以檢測到VALID之前就斷言READY。下面有幾個圖表明依耐關係,單箭頭指向的訊號能在箭頭起點訊號之前或之後斷言;雙箭頭指向的訊號必須在箭頭起點訊號斷言之後斷言。

圖 3-4 讀傳輸握手依耐關係

圖 3-5 寫傳輸握手依耐關係

圖 3-6 從機寫響應握手依耐關係

3.3傳輸結構

地址結構

AXI協議是基於burst的,主機只給出突發傳輸的第一個位元組的地址,從機必須計算突發傳輸後續的地址。突發傳輸不能跨4KB邊界(防止突發跨越兩個從機的邊界,也限制了從機所需支援的地址自增數)。

1)突發長度

ARLEN[7:0]決定讀傳輸的突發長度,AWLEN[7:0]決定寫傳輸的突發長度。AXI3只支援1~16次的突發傳輸(Burst_length=AxLEN[3:0]+1),AXI4擴充套件突發長度支援INCR突發型別為1~256次傳輸,對於其他的傳輸型別依然保持1~16次突發傳輸(Burst_Length=AxLEN[7:0]+1)。

burst傳輸具有如下規則:

wraping burst ,burst長度必須是2,4,8,16

burst不能跨4KB邊界

不支援提前終止burst傳輸

所有的元件都不能提前終止一次突發傳輸。然而,主機可以通過解斷言所有的寫的strobes來使非所有的寫位元組來減少寫傳輸的數量。讀burst中,主機可以忽略後續的讀資料來減少讀個數。也就是說,不管怎樣,都必須完成所有的burst傳輸。

注:對於FIFO,忽略後續讀資料可能導致資料丟失,必須保證突發傳輸長度和要求的資料傳輸大小匹配。

突發大小

ARSIZE[2:0],讀突發傳輸;AWSIZE[2:0],寫突發傳輸。

AxSIZE[2:0] bytes in transfer

‘b000 1

‘b001 2

‘b010 4

‘b011 8

‘b100 16

‘b101 32

‘b110 64

‘b111 128

突發型別

FIXED:突發傳輸過程中地址固定,用於FIFO訪問

INCR:增量突發,傳輸過程中,地址遞增。增加量取決AxSIZE的值。

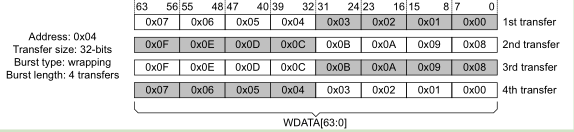

WRAP:迴環突發,和增量突發類似,但會在特定高地址的邊界處回到低地址處。迴環突發的長度只能是2,4,8,16次傳輸,傳輸首地址和每次傳輸的大小對齊。最低的地址整個傳輸的資料大小對齊。迴環邊界等於(AxSIZE*AxLEN)。

AxBURST[1:0] burst type

‘b00 FIXED

‘b01 INCR

‘b10 WRAP

‘b11 Reserved

Start_Address=AxADDR

Number_Bytes=2^AxSIZE

Burst_Length=AxLEN+1

Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。

對於INCR突發和WRAP突發但沒有到達迴環邊界,地址由下述方程決定:

Address_N=Aligned_Address+(N-1)xNumber_Bytes

WRAP突發,突發邊界:

Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length)

資料讀寫結構

WSTRB[n:0]對應於對應的寫位元組,WSTRB[n]對應WDATA[8n+7:8n]。WVALID為低時,WSTRB可以為任意值,WVALID為高時,WSTRB為高的位元組線必須指示有效的資料。

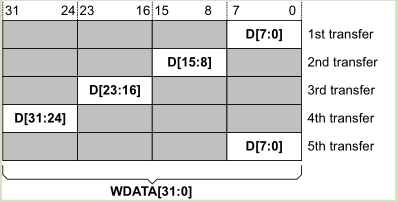

窄傳輸

當主機產生比它資料匯流排要窄的傳輸時,由地址和控制訊號決定哪個位元組被傳輸:

INCR和WRAP,不同的位元組線決定每次burst傳輸的資料,FIXED,每次傳輸使用相同的位元組線。

下圖給出了5次突發傳輸,起始地址為0,每次傳輸為8bit,資料匯流排為32bit,突發型別為INCR。

圖 3-7 窄傳輸示例1

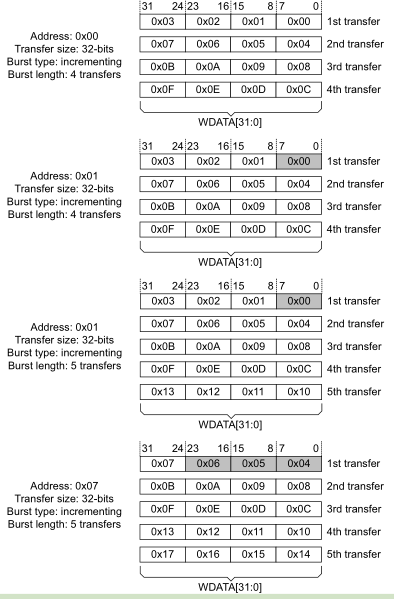

下圖給出3次突發,起始地址為4,每次傳輸32bit,資料匯流排為64bit。

圖 3-8 窄傳輸示例2

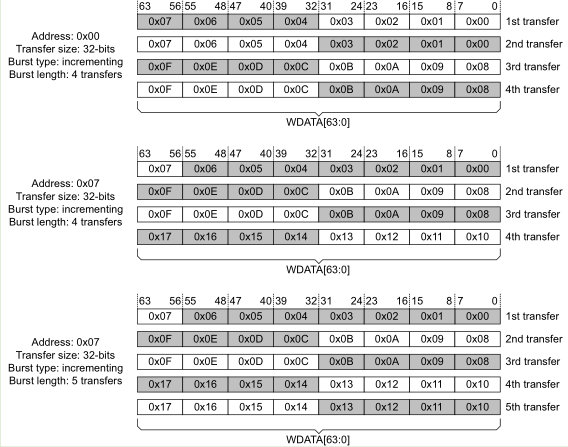

非對齊傳輸

AXI支援非對齊傳輸。在大於一個位元組的傳輸中,第一個自己的傳輸可能是非對齊的。如32-bit資料包起始地址在0x1002,非32bit對齊。

主機可以①使用低位地址線來表示非對齊的起始地址;②提供對齊的起始地址,使用位元組線來表示非對齊的起始地址。

圖 3-9 對齊非對齊傳輸示例1-32bit匯流排

圖 3-10 對齊非對齊傳輸示例2-64bit匯流排

圖 3-11 對齊的迴環傳輸示例

讀寫響應結構

讀傳輸的響應資訊是附加在讀資料通道上的,寫傳輸的響應在寫響應通道。

RRESP[1:0],讀傳輸

BRESP[1:0],寫傳輸

OKAY(‘b00):正常訪問成功

EXOKAY(‘b01):Exclusive 訪問成功

SLVERR(‘b10):從機錯誤。表明訪問已經成功到了從機,但從機希望返回一個錯誤的情況給主機。

DECERR(‘b11):譯碼錯誤。一般由互聯元件給出,表明沒有對應的從機地址。