FPGA基礎之非同步復位和同步釋放電路的詳細解釋

版權宣告:轉載請註明出處:http://blog.csdn.net/lg2lh https://blog.csdn.net/lg2lh/article/details/8488224

假設rst_async_n撤除時發生在clk上升沿,如果如下電路則可能發生亞穩態事件。

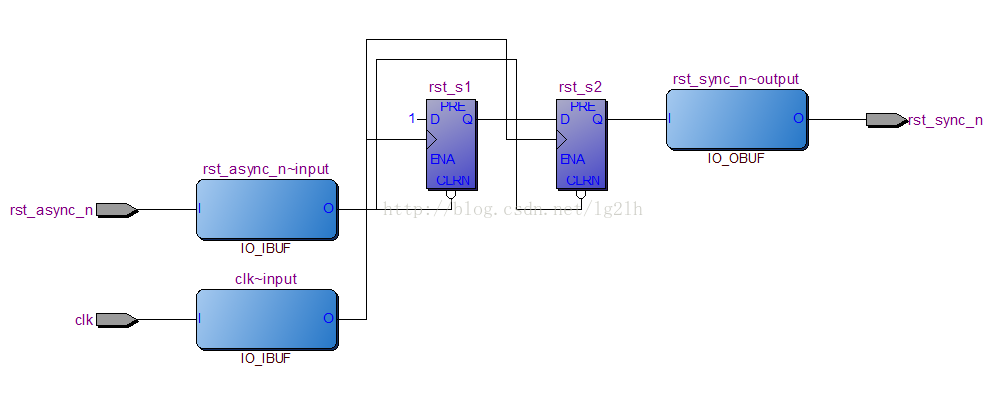

如圖第一個方框內是非同步復位和同步釋放電路。有兩個D觸發器構成。第一級D觸發器的輸入時VCC,第二級觸發器輸出是可以非同步復位,同步釋放後的復位訊號。

電路目的:方式復位訊號撤除時產生亞穩態事件。

所謂非同步復位和同步釋放,是指復位訊號是非同步有效的,即復位的發生與clk無關。後半句“同步釋放”是指復位訊號的撤除(釋放)則與clk相關,即同步的。

下面說明一下如何實現非同步復位和同步釋放的。

非同步復位:顯而易見,rst_async_n非同步復位後,rst_sync_n將拉低,即實現非同步復位。

同步釋放:這個是關鍵,看如何實現同步釋放,即當復位訊號rst_async_n撤除時,由於雙緩衝電路的作用,rst_sync_n復位訊號不會隨著rst_async_n的撤除而撤除。

第二級的觸發器的輸入之前是低電平,所以復位撤除時,不存在亞穩態的問題,他不用考慮是該高電平還是低電平,因為一直為低電平,但是第一級觸發器,復位撤除之前輸出是低電平,撤除之後因為輸入是高電平,這時候輸出有可能是低電平,也可能是高電平,就有亞穩態的問題了,但是經過一個時鐘週期就穩定了。

假設rst_async_n撤除時發生在clk上升沿,如果不加此電路則可能發生亞穩態事件。但是加上此電路以後,假設第一級D觸發器clk上升沿時rst_async_n正好撤除,則D觸發器1可能輸出高電平“1”,也可能輸出亞穩態,也可能輸出低電平,但此時第二級觸發器不會立刻更新輸出,第二級觸發器輸出值為前一級觸發器次clk來之前時的第一級觸發器Q1的輸出狀態。顯然Q1之前為低電平,顧第二級觸發器輸出保持復位低電平,直到下一個clk來之後,才隨著變為高電平。即同步釋放。

-

module ex1 ( -

output rst_sync_n, -

input clk, rst_async_n); -

reg rst_s1, rst_s2; -

always @ (posedge clk, posedge rst_async_n) -

if (rst_async_n) begin -

rst_s1 <= 1'b0; -

rst_s2 <= 1'b0; -

end -

else begin -

rst_s1 <= 1'b1; -

rst_s2 <= rst_s1; -

end -

assign rst_sync_n = rst_s2; -

endmodule

對於實際的實現TECH MAP檢視