非同步復位和同步釋放電路的詳細解釋

1、首先給出非同步復位訊號亞穩態的原因:

復位結束也就是釋放的時刻恰在時鐘上升沿的建立時間和保持時間之間時無法決定現在的復位狀態是1還是0,造成亞穩態。

下面是具體解釋:

在帶有復位端的D觸發器中,當reset訊號“復位”有效時,它可以直接驅動最後一級的與非門,令Q端“非同步”置位為“1”or“0”。這就是非同步復位。當這個復位訊號release時,Q的輸出由前一級的內部輸出決定。

然而,由於復位訊號不僅直接作用於最後一級門,而且也會做為前級電路的一個輸入訊號,因此這個前一級的內部輸出也受到復位訊號的影響。前一級的內部電路實際上是實現了一個“保持”的功能,即在時鐘沿跳變附近鎖住當時的輸入值,使得在時鐘變為高電平時不再受輸入訊號的影響。對於這一個“維持”電路,在時鐘沿變化附近,如果“reset”訊號有效,那麼,就會鎖存住“reset”的值;如果reset訊號釋放,那麼這個“維持”電路會去鎖當時的D輸入端的資料。因此,如果reset訊號的“釋放”發生在靠時鐘沿很近的時間點,那麼這個“維持”電路就可能既沒有足夠時間“維持”住reset值,也沒有足夠時間“維持”住D輸入端的值,因此造成亞穩態,並通過最後一級與非門傳到Q端輸出。如果reset訊號的“釋放”時間能夠晚一點點,也就是說,讓“維持”電路有足夠的時間去鎖住“reset”的值,那麼,我們就可以肯定輸出為穩定的“reset”狀態了。這一小段鎖住“reset”值所需要的時間,就是暫存器的removal

time要求。

2、如果上面的沒有看懂,那麼下面的解釋得比較清楚。

轉自:http://www.xue5.com/Developer/Software/665219.html

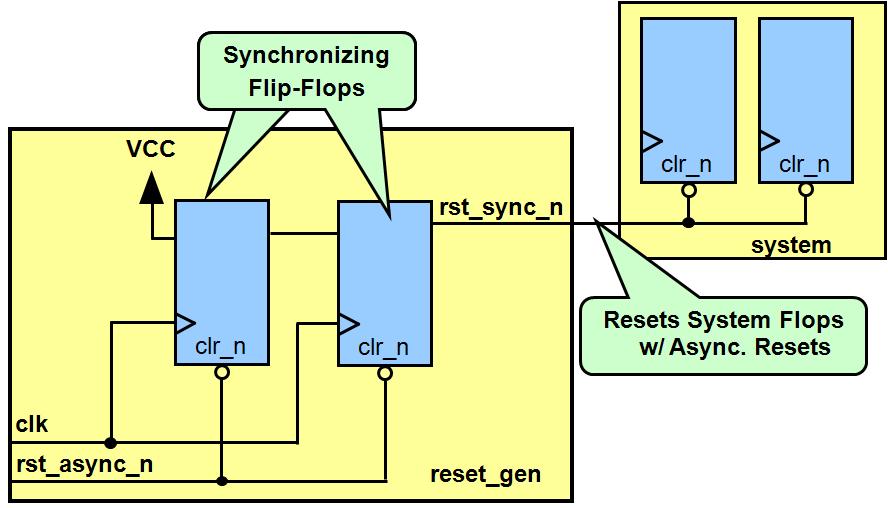

如圖第一個方框內是非同步復位和同步釋放電路。有兩個D觸發器構成。第一級D觸發器的輸入時VCC,第二級觸發器輸出是可以非同步復位,同步釋放後的復位訊號。

1)電路目的:防止復位訊號撤除時產生亞穩態事件。

2)什麼是非同步復位和同步釋放:是指復位訊號是非同步有效的,即復位的發生與clk無關。後半句“同步釋放”是指復位訊號的撤除也與clk無關,但是復位訊號是在下一個clk來到後起的作用(釋放)。

下面說明一下如何實現非同步復位和同步釋放的。

非同步復位:顯而易見,rst_async_n非同步復位後,rst_sync_n將拉低,即實現非同步復位。

同步釋放:這個是關鍵,看如何實現同步釋放,即當復位訊號rst_async_n撤除時,由於雙緩衝電路(雙暫存器)的作用,rst_sync_n復位訊號不會隨著rst_async_n的撤除而撤除。

假設rst_async_n撤除時發生在clk上升沿,如果不加此電路則可能發生亞穩態事件,但是加上此電路以後,假設第一級D觸發器clk上升沿時rst_async_n正好撤除,則D觸發器1輸出高電平“1”,此時第二級觸發器也會更新輸出,但是輸出值為前一級觸發器clk來之前時的Q1輸出狀態。顯然Q1之前為低電平,顧第二級觸發器輸出保持復位低電平,直到下一個clk來之後,才隨著變為高電平。即同步釋放。

1 module reset_gen ( output rst_sync_n, input clk, rst_async_n); 2 reg rst_s1, rst_s2; 3 wire rst_sync_n ; 4 5 always @ (posedge clk, posedge rst_async_n) 6 if (rst_async_n) 7 begin 8 rst_s1 <= 1'b0; 9 rst_s2 <= 1'b0; 10 end 11 else 12 begin 13 rst_s1 <= 1'b1; 14 rst_s2 <= rst_s1; 15 end 16 17 assign rst_sync_n = rst_s2; //注意這裡的rst_sync_n才是我們真正對系統輸出的復位訊號 18 19 endmodule