UDP千兆乙太網FPGA_verilog實現(二、知識蒐集)

阿新 • • 發佈:2018-11-20

:

該晶片主要由三部分組成:

傳送端物理編碼子層(PCS TX)、接收端物理編碼子層(PCS RX)和配置介面(management interface) 。PCS RX主要是用來接收外部模擬訊號,並將接收到的模擬訊號進行處理,如魔術轉換、交叉檢測及自動校正、極性校正、自適應均衡、串擾消除、回聲消除等,最終將處理好的數字訊號傳輸給FPGA。management interface就是用來配置或讀取PHY晶片內部的暫存器。

RTL8211EG晶片的管腳,由於RTL8211EG晶片有兩種介面方式:RGMII和GMII

上述圖片來自於某家FPGA機構gao石,我發現又tm有錯。傳送/接收 口描述錯了

以下來自於官方的datasheet:

下圖說明了這款PHY晶片的管腳分配,在GMII模式下。每個管腳的意義。

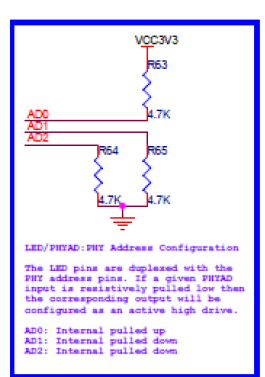

某石的原理圖,將PHYAD0上拉=1,PHYAD1下拉=0,PHYAD2下拉=0 倘若三個PHY全是0,那麼說明這是來自MAC的一個廣播,所有的PHY晶片都必須迴應。

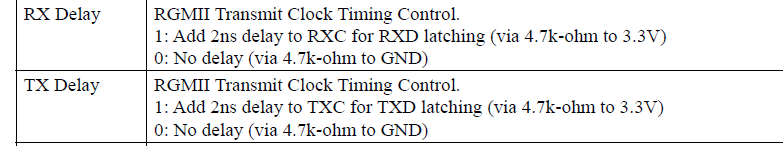

下面來看RX—Delay管腳

RX—Delay和TX-Delay引腳都為上拉狀態,則表示在RGMII介面的傳輸時序中為了給TXD和RXD引腳鎖存而給TXC和RXC引腳延時2ns

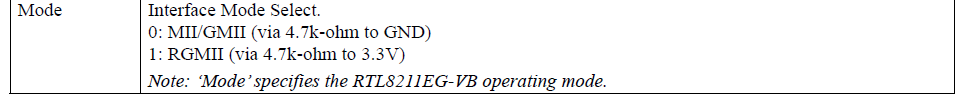

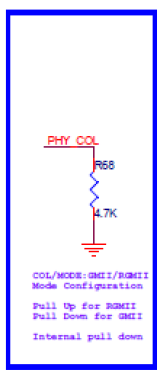

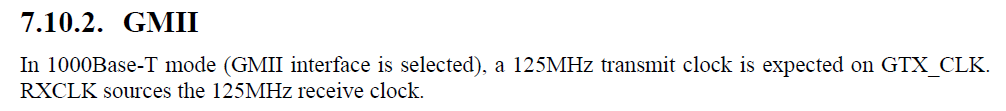

PHY-COL管腳接地,所以為GMII模式。PHY-COL為下拉狀態,則晶片通過GMII介面完成與MAC層之間的資料傳輸。

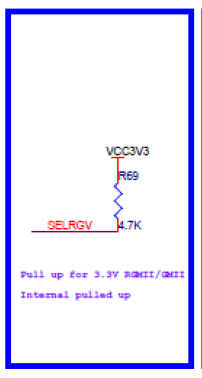

SELRGV引腳為上拉狀態,則表示GMII介面為3.3V的電壓標準。

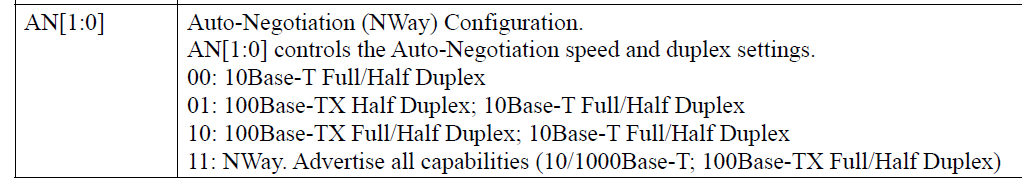

AN0和AN1引腳都為上拉狀態,則表示配置為自動協商模式,支援10/1000Base-T,100Base-TX 全/半雙工模式。

’—

‘-------------------

所以,由於我們使用FPGA完全代替了MAC晶片,所以FPGA的管腳直接與RTL8211EG晶片內部的PCS TX和PCS RX介面相連,RTL8211EG晶片的MDI【3:0】引腳與乙太網變壓器介面HR911130相連,完成乙太網資料包的傳送與接收。

’--------------------------------------------------------------------------

總結下: