[轉帖]超能課堂:2018-5-10 納米制程背後的真真假假

超能課堂(135):納米制程背後的真真假假

2018-5-10 15:19 | 作者:樑俊豪 | 關鍵字:CPU,工藝製程,納米,超能課堂

http://www.expreview.com/60806.html

分享到我們經常在某手機發佈會現場聽到,“××處理器採用了最先進的10nm工藝製造”,那麼究竟這個10nm代表著什麼意思呢?納米制程對於CPU、SoC而言到底多重要?又與電晶體、FinFET以及EUV有什麼關係呢 ?

我們經常在某手機發佈會現場聽到,“××處理器採用了最先進的10nm工藝製造”,那麼究竟這個10nm代表著什麼意思呢?納米制程對於CPU、SoC而言到底多重要?又與電晶體、FinFET以及EUV有什麼關係呢 ?

![]()

×× nm製造工藝是什麼概念?

我們曾經在超能課堂(66):沙子做的CPU,憑什麼賣那麼貴?完整闡述了一顆CPU誕生過程,其中第七步的紫外線曝光就是最重要的光刻技術,而光刻工藝是積體電路製造過程中最直接體現其工藝先程序度的技術,其中光刻技術的解析度是指光刻系統所能分辨和加工的最小線條尺寸,決定了CPU中的電晶體最小特徵尺寸。

![]()

ASML NXE-3350B光刻系統尺寸,頂級光刻機精細度高,系統結構非常複雜

根據ITRS《國際半導體技術藍圖》裡面的相關規定,我們平常說說的16nm、14nm、10nm就是用來描述半導體制程工藝的節點代數,而它應在不同半導體元件上,所描述的物件可能有所不一樣,比方說在DRAM中,可能是描述在DRAM Cell中兩條金屬線間最小允許間距Pitch值的一半長度Half-Pitch半節距長度;而用在CPU上時,可能描述的則是CPU電晶體中最小柵極線寬。

總的來說,××nm製程描述了該工藝代下加工尺度的精確度,但它並非指半導體器件中某一具體結構的特徵尺寸,而是加工精度的尺寸的最小值。

這裡我們主要討論的是關於CPU的製程問題,因為製程對於CPU效能、功耗、發熱來說有著比較重要地位,製程的改變對於CPU效能的影響也是非常之大的。之前我們也講到,14nm通常就是用來描述電晶體的柵極線寬。

![]()

Gate Length就是柵極線寬

為什麼要用柵極線寬而不是其他的線寬來表徵工藝節點?

這個主要是涉及到電晶體結構問題,一般來說CPU內部邏輯閘電路都是使用MosFET,它有三個電極,柵極(Gate)、源極(Source)、漏極(Drain),其中柵極與源極之間的電壓差可以控制從源極流向漏極的電流大小,因此柵極起到了控制作用。

![]()

目前常見的FinFET結構 MosFET(Oxide,氧化層;Body,襯底)

同時諸如電晶體電子遷移率等等特性是完全依賴於摻雜離子以及生產工藝所決定,基本上是不能動,不過其中的電晶體柵極的長寬比還是可以做做文章,電壓一樣的情況下,柵極寬度越小,電子就有可能通過晶體襯底從負極向正極流動,造成漏電,而漏電問題會帶來靜態功耗的上升。

因此柵極線寬作用是非常重要,柵極線寬通常都是考量超大規模積體電路設計的最重要引數,也因此以它作為半導體工藝的節點劃代,這個是傳統意義上工藝製程的規範。

那麼意思是製程越小越好咯?

確實是這樣,你想,線寬越小,那麼單個電晶體的尺寸就越小,那麼做出來的CPU die面積就越小啦,同一塊晶圓就能生產出更多的CPU die,那麼無形中就增加了廠商收入(成片越多)。反過來,你也可以在相同的die面積下整合更多的電晶體,那麼CPU效能也會得到提升(當然這不是絕對的)。

其次由於柵極線寬變小了,那麼工作電壓會相應降低,CPU的功耗也會隨之降低,此外在更先進的工藝下,電晶體截止頻率上會有更好表現,CPU也自然能工作在更高的頻率上。所以我們經常看到某某SoC、CPU說,我們採用了更先進的10nm,功耗下降了××%,頻率提升了××%,效能提升了××%。

臺積電的10nm都量產已久,Intel卻還沒出貨,Intel的無敵工藝不行了?

前幾年Intel從22nm進入14nm時代,大家都在說Intel在工藝製程上起碼領先於其他家3-5年以上,但是好景不長,大家發現卻發現Intel 14nm居然打磨了一遍又一遍,從Skylake(14nm)、Kaby Lake(14nm+)、Coffee Lake(14nm++),歷經三代依然在用,據說還會有14nm+++,原本說好的10nm遭遇大量技術問題而難產。

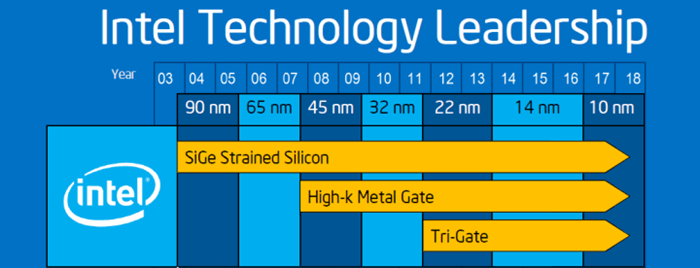

Intel之前公佈的工藝線路圖,10nm本該2017年就用上,直到現在還沒有影

反觀對手臺積電、三星在代工路上風生水起,16/14nm節點上追趕上了Intel的進度,令人驚訝的是,臺積電、三星的10nm工藝量產遠遠早於Intel,相關產品(例如高通驍龍835)甚至在市場上已經賣了整整一年,臺積電甚至在今年量產7nm晶片,這又是怎麼回事?

普羅大眾都認為10nm肯定比14nm先進,12nm都比14nm好,就在Intel被消極輿論聲音即將淹沒的時候,Intel點破了納米制程工藝數字背後“奧祕”,因為臺積電、三星的工藝數字都經過不同程度的“美化”,在命名上耍小聰明,也就是“數字”壓制,雖然Intel在“數字”上輸了,但是從工藝各個層面在一些關鍵技術引數上來說,Intel其實更勝一籌。之前的14nm就曾經出現過這種情況,××nm製程已經開始脫離原先的範疇,大家開始“造假”。

14nm時代,Intel已經踢爆過一次幕後的祕密

![]()

Techinsights也做過對比,Intel 14nm確實優於三星的14nm LPE

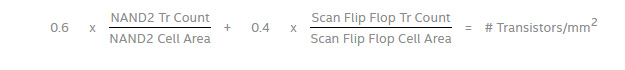

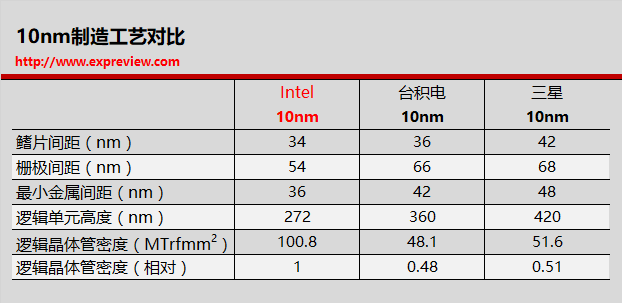

Intel表示線寬僅僅代表工藝節點,但要衡量這個工藝的好壞,Gate Pitch柵極間距、Fin Pitc鰭片間距、Fin Pitch最小金屬間距、Logic Cell Height邏輯單元高度的引數更具參考意義。同時Intel處理器架構與整合部門主管、高階院士Mark Bohr提出以Transistor Density電晶體密度來衡量半導體工藝水平,並提出了以下公式:

不過計算過程很麻煩,怎麼算就交給專業人士就行,我們只看結果

比如在去年9月,Intel舉辦的Technology and Manufacturing Day上,主動公佈出三家10nm工藝相關技術引數指標,我們看到Intel在這些關鍵性技術指標上都是吊打其餘兩家,例如Intel的10nm光刻技術製造出來的鰭片、柵極間隔更小(注意Intel公佈的是間隔對比,不是線寬,更有比較意義)。因此在電晶體密度上幾乎是臺積電、三星的兩倍,達到了每平方毫米1億個電晶體,同時保持了邏輯單元高度低的優良傳統,在3D堆疊上更有優勢。

最近Semiwiki報道了三星的10nm、8nm以及7nm工藝電晶體密度情況,其10/8/7nm工藝的電晶體密度分別是是55.10/64.4/101.23 MTr/mm2。可以看到,三星的7nm工藝在電晶體密度上才追勉強上Intel的10nm,誰在玩小把戲,你不會不知道吧?

那工藝的極限在哪裡?

當製程低於20nm時候,由於二氧化矽絕緣層太薄了,只有幾個原子那麼厚,那麼這個時候對於電晶體來說是十分不穩定的,會導致電子隨意穿過壁壘導致漏電,導致晶片功耗增加。不過這個還算是小問題,Intel弄出了高介電常數薄膜和金屬門積體電路,以及耳熟能詳的FinFET鰭式場效電晶體結構,通過增加絕緣層表面積來增加電容值,以此降低漏電流大小的問題。同時為了製造出7nm線寬,行業共識是採用EUV極紫外作為光刻光源,具有曝光次數少、不要進行克服衍射效應產生的光學鄰近修正特點,不過目前依然有大量問題,因此EUV光刻技術尚未完全成熟。

![]()

Intel 22nm FinFET結構

當工藝進步到7nm的時候,半導體企業更加不淡定了,因為在矽基半導體上,電晶體的線寬下降到7nm,一個不可避免的問題發生了,那就著名的量子隧穿效應。

在經典物理中,巨集觀粒子的能量小於勢壘高度時,這個粒子是不可能穿過這個勢壘,但是對於微觀粒子,此時具有波粒二象性,神奇的量子效應就出現了,即便是能量低於勢壘高度,仍有一定的概率可以突破勢壘。

這要就造成一個大問題,這個電子到底過去了沒有,監測到沒有,邏輯閘該輸出0還是1,答案不知道,那麼CPU就不能正常工作,因此要杜絕這個問題發生。

![]()

微觀粒子穿越過一個位勢壘,粒子的能量在穿越前與穿越後維持不變,但量子幅會降低

Intel、臺積電、三星等半導體制造前沿企業均已經針對這個問題進行了研究,依然有一些措施可以防止量子隧穿效應的出現。對於矽基半導體,Intel是展望的工藝極限是5nm或者3nm;三星的話後續會有8/7/6/5/4nm LPP工藝,並且在4nm會引入Multi Bridge Channel FET結構(簡稱MBCFET,多溝道場效電晶體),獨特GAAFET(邏輯閘環繞場效應電晶體)技術,使用二維納米片晶克服物理擴充套件以及FinFET架構帶來的侷限性。

![]()

anandtech總結的全球半導體企業製程路線圖

而媒體上低於3nm工藝的報道都不是基於矽氧化物,而是石墨烯等新型複合半導體材料,而且全都是實驗室技術突破,無法短時間內量產的。但尋找新材料代替矽製作更低製程的電晶體是一個行之有效的解決方法之一。

![]()

美國勞倫斯伯克利國家實驗室 1nm電晶體就是用納米碳管做的

納米制程工藝背後的虛與實

通讀全文,你就知曉目前半導體制程所謂的10nm 、7nm已經偏離最初的範疇,不再是嚴格意義上線寬,16nm“優化”一下可以叫12nm,10nm“優化”還可以叫8nm。作為摩爾定律擁護者的Intel當然是氣不過,多次點評批評三星、臺積電的“數字美化”行為。實際從電晶體密度引數上看,三星的7nm≈Intel 10nm,如此看來Intel的10nm難產也是情有可原,目標定得太高,卻被友商狡猾地換了個名字所取勝,普羅大眾卻因為不懂工藝製程的虛實而相信廠商的一面之詞。Intel的製造工藝技術其實並沒有那麼不堪,仍然處於世界領先地位。