xdc如何設定輸入延時

阿新 • • 發佈:2018-11-28

常用命令:

Set_input_delay,create_clock,set_output_delay以及用於組合邏輯的set_max_delay.

Input delay:

- 什麼是輸入延時?

- Trace delay(又叫做board delay)板級延時

- 輸入延時:以上游晶片的傳送沿(launch edge)為參考點。傳送資料之後,經過input delay這麼長時間。資料到達fpga的輸入埠的管腳。

- 以上游晶片的傳送沿為參考點,經過四納秒,資料到達fpga的輸入埠。

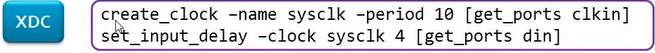

- 完整的例子

- FDRE:第一集觸發器(first D register)

- Input setup timing report summary

- Input Hold timing report

- Summary

- 詳細時許報告

- Summary

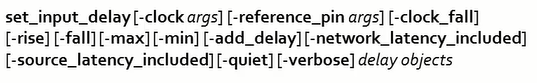

- Set_input_delay基本語法規則

- –clock:設定參考時鐘,通常認為是上升沿為參考點

- –max

- –min

- Eg:

- DDR

- 系統同步:兩片晶片共用時鐘。

- Source synchronise:源同步

- DDR模式:上升沿傳送的資料用下降沿來捕獲,下降沿傳送的資料用上升沿來捕獲。

- –clock_fall(使用下降沿作為參考沿)

- –add_delay同時有效

- 靜態時序路徑

- 一定是從一個觸發器到另一個觸發器,不管這兩個觸發器是否在同一個晶片內,只有在這兩個觸發器之間才能構成一個完整路徑。

- 在預設情況下,輸入埠到達內部第一級觸發器的路徑並不是一個完整的時序路徑。

- 要素

- 時鐘,是外部晶片傳送沿做為參考點

- 然後傳送資料經過Tco再加上board delay到達fpga的輸入埠。

- Summary

- Expr:計算求和