淺談SPI匯流排

序列外圍裝置介面(Serial Peripheral Interface,SPI)是由 Motorola 公司開發的,用來在微控制器和外圍裝置晶片之間提供一個低成本、易使用的介面(SPI 有時候也被稱為4線介面)。這種介面可以用來連線儲存器、AD/DA轉換器、實時時鐘日曆、LCD驅動器、感測器、音訊晶片,甚至其他處理器。目前支援 SPI 的元件很多,並且還在不斷增加。

這裡需要提一下,由於專利在電子行業是很關鍵的,因此部分廠商可能會將 SPI 通訊協議更名以規避高昂的專利費,但其硬體處理方式是一樣的,只是換了一個名稱而已(或者在協議上做了一些修改),例如 TI 的 SSI(Synchronous Serial Interface)通訊協議。

與標準的串列埠不同,SPI 是一個同步協議介面,所有的傳輸都參照一個共同的時鐘,這個同步時鐘訊號由主機(處理器)產生。接收資料的裝置(從裝置)使用時鐘對序列位元流的接收進行同步化。可能會有許多晶片連到主機的同一個 SPI 介面上,這是主機通過觸發從裝置的晶片的片選輸入引腳來選擇接收資料的從裝置,沒有被選中的外設將不會參與 SPI 傳輸。

SPI 主要使用4個訊號:主機輸出/從機輸入(MOSI)、主機輸入/從機輸出(MISO)、序列時鐘(SCLK 或 SCK)和外設片選(nCS)。有些處理器有 SPI 介面專用的片選,稱為從機選擇(nSS)。

MOSI 訊號由主機產生,從機接收。在有些晶片上,MOSI 只被簡單地標為序列輸入(SI),或者序列資料輸入(SDI)。MISO 訊號由從機產生,不過還是在主機的控制下產生的。在一些晶片上,MISO 有時被稱為序列輸出(SO),或者序列資料輸出(SDO)。外設片選訊號通常只是由主機的備用 I/O 引腳產生。

SPI 介面在內部硬體實際上是兩個簡單的移位暫存器,在主器件的移位脈衝下,資料按位傳輸,高位在前,低位在後,為全雙工通訊,資料傳輸速度總體來說比 I2C 匯流排要快,速度可達到 Mbps 級別。

根據時鐘極性和時鐘相位的不同,SPI 有四個工作模式。

時鐘極性有高、低兩極:

1、時鐘低電平時,空閒時時鐘(SCK)處於低電平,傳輸時跳轉到高電平;

2、時鐘極性為高電平時,空閒時時鐘處於高電平,傳輸時跳轉到低電平。

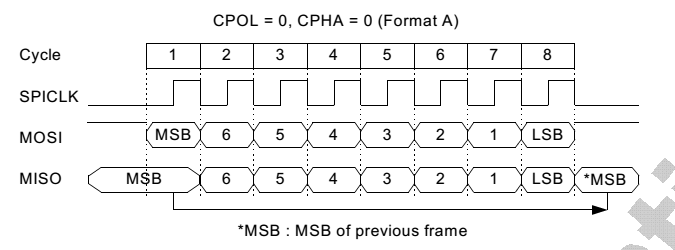

時鐘相位有兩個:相位0 和 相位1。對於時鐘相位0,如果時鐘極性是低電平,MOSI 和 MISO 輸出在時鐘(SCK)的上升沿有效(如圖1所示)。

圖1. 時鐘極性為低電平且時鐘相位0時的SPI時序圖

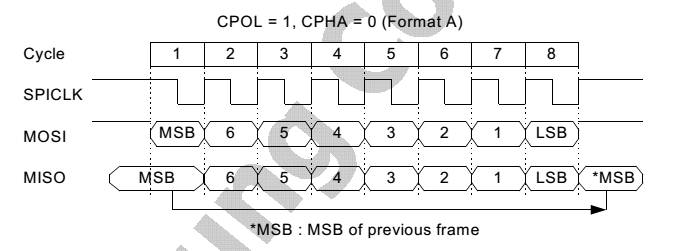

如果時鐘極性為高電平,對於時鐘相位0,這些輸出在 SCK 的下降沿有效(如圖2所示)。

圖2. 時鐘極性為高電平且時鐘相位0時的SPI時序圖

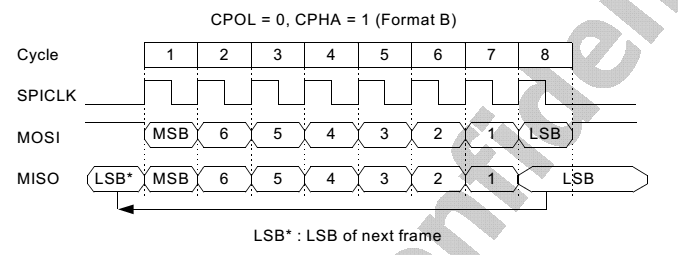

對於時鐘相位1,情況則相反。此時如果時鐘極性是低電平,MOSI 和 MISO 輸出在時鐘(SCK)的下降沿有效(如圖3所示)。

圖3. 時鐘極性為低電平且時鐘相位1時的SPI時序圖

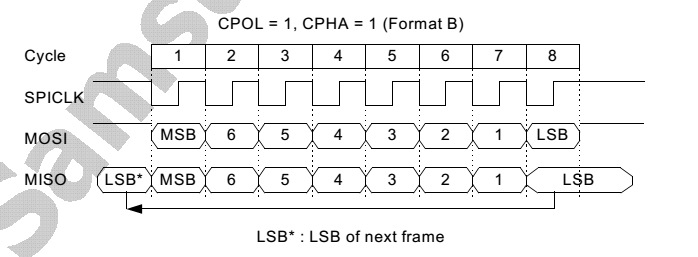

如果時鐘極性是高電平,這些輸出在 SCK 的上升沿有效(如圖4所示)。

圖4. 時鐘極性為高電平且時鐘相位1時的SPI時序圖

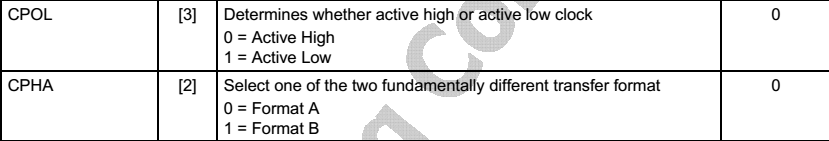

工程中一般會用 CPOL 代表時鐘極性,用 CPHA 代表時鐘相位,在 S5PV210 的 datasheet 中,我們可以看到相應的 SPI 介面配置暫存器(如圖5所示)。

圖5. S5PV210的SPI配置暫存器CH_CFGn

也就是由兩個位(CPOL 和 CPHA)共同決定 SPI 的工作模式,所以有 2 * 2 = 4 種工作模式。其中,時鐘極性(CPOL)決定的是時鐘空閒時電平的高低狀態(0:空閒時低電平,1:空閒時高電平);時鐘相位(CPHA)決定的是資料在時鐘的上升沿或下降沿鎖存/取樣(0:第一個邊沿開始,1:第二個邊沿開始)。

最後,SPI 介面的一個缺點:沒有指定的流控制,沒有應答機制確認是否接收到資料。

原文:https://blog.csdn.net/lu_embedded/article/details/51520056