LPMM閱讀筆記——第五章 電源門控設計part1

第五章 電源門控設計part1

由於第五章內容太多,且這一個章節將的內容都是全書的重點,所以我將其拆分成幾個部分來寫,這是第一部分。

5 電源門控設計

這一章把電源門控的每一個組成部分從前端、RTL的視角進行了介紹,並對驗證和測試這兩個方面做了補充說明。

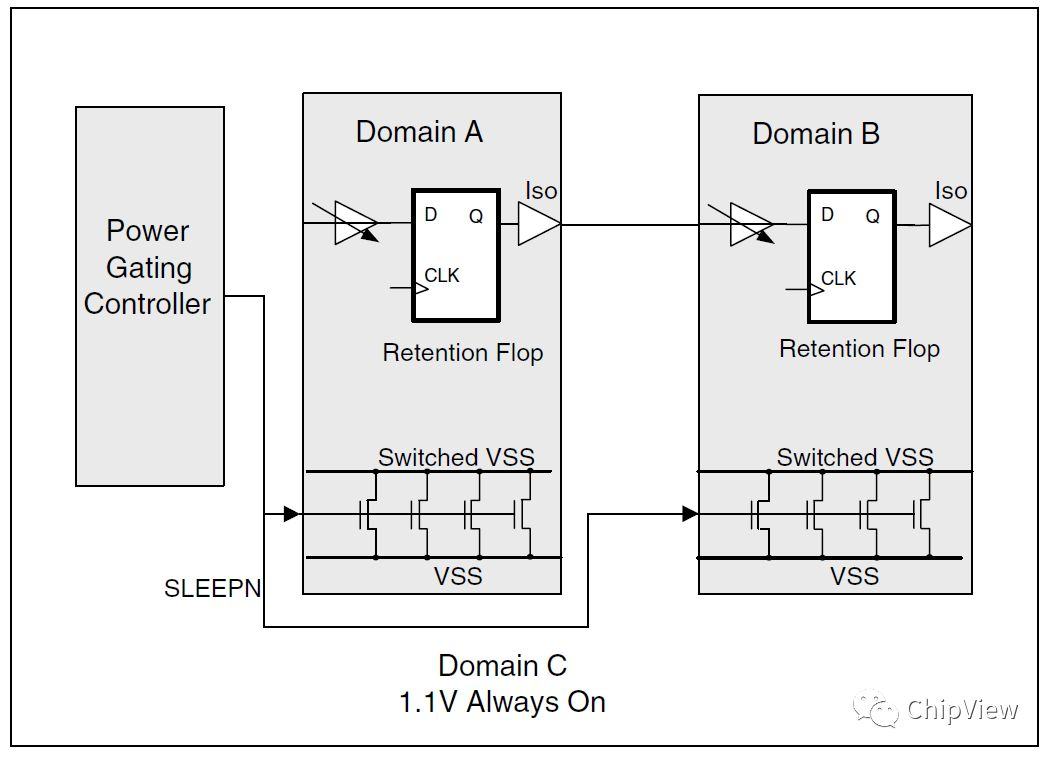

圖 1 所示的帶有電源門控的SoC結構圖中展示了電源門控設計中需要用到的關鍵元件。

圖 1帶電源門控的SoC結構圖

電源門控設計的關鍵問題包括開關網路和電源門控控制器的設計,另外,還需要確定插入保持暫存器和隔離單元的時間和位置。

5.1 開關結構設計

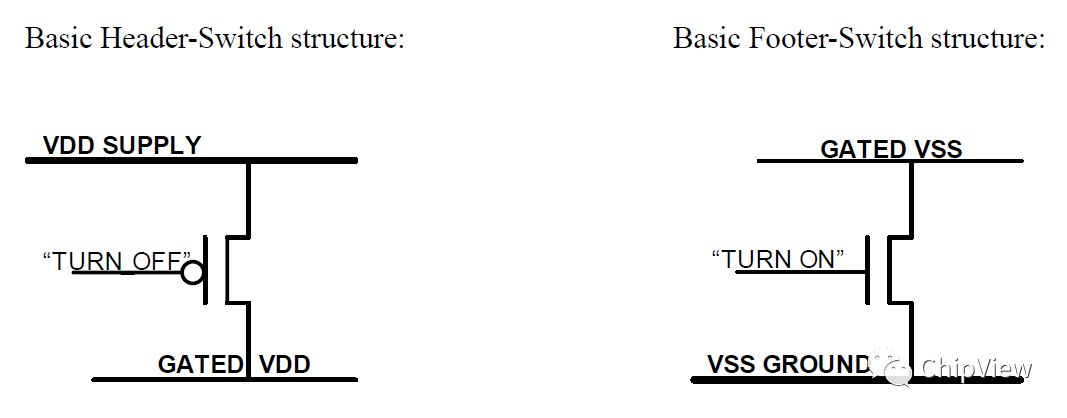

電源門控網路中用到的開關結構有頭開關(Header-Switch)和腳開關(Footer-Switch)兩種型別,其結構分別如圖 2所示:

圖 2基本的開關結構

從功能的角度來看,有以下幾個方面的理由支援使用Header-Switch結構的cell組成電源門控網路:

• 如果使用的是片外電源門控,由於板級通常是共地的,所以只能使用Header-Switch對VDD進行控制;若片外和片內門控都有使用,也建議使用Header-Switch對VDD進行控制,因為這樣做可以使內部門控和外部門控的行為表現一致,從而簡化功能驗證、時序分析和功耗分析。

• 對於使用多電壓域技術的SoC系統而言,其內部不同電壓域間的Level shiffer通常是共地的,不宜對VSS進行門控。

• 使用Header-Switch時,門控關閉意味著內部的訊號節點都被接地,這種情況有利於系統設計工程師進行問題分析。

基於上述理由,本章重點介紹基於Header-Switch的電源門控技術,支援使用Footer-Switch切換VSS是基於開關的電氣特性來分析的,這部分內容會在後面的第14章介紹。

書中對於電源門控設計給出如下建議:

-

僅對VDD或者VSS使用門控,而不是兩者同時使用,以儘量減小開關網路上的壓降。

-

在設計階段儘早的確定使用Header-Switch還是Footer-Switch的開關型別。

-

如果晶片中也有采用外部電源門控設計,則使用Header-Switch最合適。

-

若晶片中有使用多電壓域技術,則使用Header-Switch更合適。

-

不要將Footer-Switch、外部電源門控以及多電壓域設計混用,因為這樣會使得功能、時序、功耗分析變得複雜。

5.1.1 電源門控的控制

電源門控的控制中一個關鍵的問題是避免開關接通時產生浪湧電流,因為過大的浪湧電流可能導致晶片內電源上產生尖峰電壓,尖峰電壓可能會對始終上電模組中的暫存器或門控電源模組中的保持暫存器造成損壞。

避免浪湧電流的方法在第14章中會有介紹,一種具有代表性的方法是將控制訊號以菊花鏈的方式接到電源門控網路的各個開關上(一個電源門控網路通常由成百上千個開關),電源門控控制器的控制訊號接到門控網路的第一個開關上,第一個開關的控制訊號加上適當的buf(主要用以增加延遲)後接到下一個開關的控制端,以此類推。

另一種比較積極的方法是使控制器輸出多個控制訊號,分先後開啟不同的開關組,但這樣會增加電源門控控制器的複雜度。

無論採用何種做法,都會導致電源網路從上電到上電完成需要一段較長的時間,出於這個原因,電源門控網路需要輸出一個反饋訊號給到電源門控控制器,用以確認上電完成。

注意:電源門控網路的控制訊號上在插入buf以增加延遲時,必須插入始終上電的buf,而不是電源門控後的buf。

5.1.2 電源門控控制的建議

-

電源控制器需要針對所使用的電源門控技術中採用的開關型別進行設計,確保控制器和開關匹配。

-

應該為電源門控控制埠增加斷言,以匹配所選的開關型別,便於在RTL階段進行功能驗證。

-

在測試模式下,必須使電源門控控制訊號可控。

-

避免外部門控和內部門控同時使用。

5.2 訊號隔離

前面有提到過,帶電源門控的模組在掉電過程中,其輸出為一箇中間電平,可能導致其他模組出現直通電流,造成功能錯誤,所以需要在電源門控模組的輸出上增加一個隔離單元,在門控單元被下電時,將輸出鉗位到正常的電平,避免引起功能異常。

5.2.1 訊號隔離原理

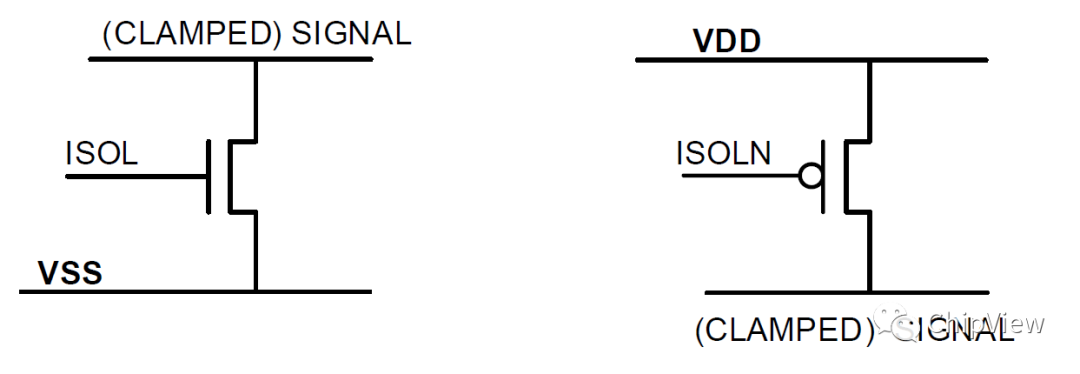

有將訊號鉗位到0、1和最近的值的3種基本型別的隔離單元。大多數情況下,將訊號鉗位到無效狀態就足夠了,即當訊號為高電平時,將訊號鉗位到0,與門可實現該邏輯;當訊號為低電平有效時,將值鉗位為1,或門可實現該邏輯;這兩種基本的門式隔離單元結構如圖 3所示;

圖 3 基本隔離單元

上述隔離單元在實現訊號隔離的同時給訊號帶來了延遲,對於某些關鍵路徑(如cache)而言,增加這些延遲可能是不可接受的。另一種不增加延遲的隔離技術是使用上拉或者下拉電晶體的方式實現,這種方法的原理如圖 4所示:

圖 4 使用上拉和下拉電晶體的隔離單元

對於被門控模組輸出訊號而言,使用上拉和下拉電晶體的隔離單元會有多驅的問題,考慮這樣一種場景,被門控模組下電後重新上電時,由於上電操作先於隔離使能的撤銷時間,所以在上電時會存在競爭問題,反過來,在下電的時候隔離使能操作先於下電操作,所以下電過程中也存在競爭問題;除了上述問題外,多驅還會對可測性帶來影響,因此,儘管上拉和下拉電晶體的隔離單元在時序和麵積成本上很低,但仍然不建議使用該方法;相反,在工程中,建議使用與/或門形式的隔離單元。

5.2.2 隔離位置的選擇

從邏輯上講,將隔離單元放在被門控模組的內部或輸出訊號的目的端是一樣的,但有下面這些重要的因素會影響到該選擇:

• 如果門控模組的輸出訊號會給到多個模組使用且將隔離單元放在接收端,則每個輸出可能需要多個隔離單元,所以,當門控模組的輸出訊號會給到多個模組使用時,將隔離單元放在被門控模組內會更節省面積。

• 隔離單元放在電源被門控模組的內部會使各種分析和檢查變得簡單,否則我們需要檢查每一個輸出訊號,確保每個輸出訊號上都有隔離單元,若電源被門控的模組需要複用,則相應的檢查和分析還要在來一次,將隔離單元放在被門控模組內部則只需做一次這樣的工作。

• 將隔離單元放在被門控模組的內部,會對佈局和佈線有一些約束,由於隔離單元需要始終供電,所以電源被門控模組內部的電源佈線會變得複雜,不過現在的EDA工具已經可以幫助解決這些問題了。

書中建議在做可重用的IP設計時,將隔離單元放在IP中封裝起來,使SoC的整合不受隔離單元的影響。

5.2.3 鉗位值的選擇

在考慮電源門控模組的介面隔離時,有兩個目標,一是最大限度的減小漏電流,另一個是避免不必要/不正確的行為,對於訊號隔離為0/1有如下方面的考慮可供參考:

• 考慮這樣一種情況,當電源門控模組斷電時,始終上電模組接到值為鉗位後的訊號,若該訊號為高電平有效(例如axi的awvaild),且該訊號被鉗位為高電平,則axi_slave可能會將這個鉗位值解析為一個命令,導致錯誤的操作;所以為了避免上述問題,應該將訊號鉗位到無效狀態的電平。

• 復位是一個例外,因為復位通常是低電平有效,但實際上,在模組下電時,我們應該是希望其復位訊號為有效狀態,所以復位訊號通常鉗位為有效狀態0。

• 相鄰模組都可以下電時,輸出訊號鉗位為0更合適,因為當我們把輸出訊號鉗位為1時可能出現該訊號到達的目標模組也被下電,這樣的情況下,該訊號在目標模組內可能產生多餘的直通電流,增加不必要的漏電流。

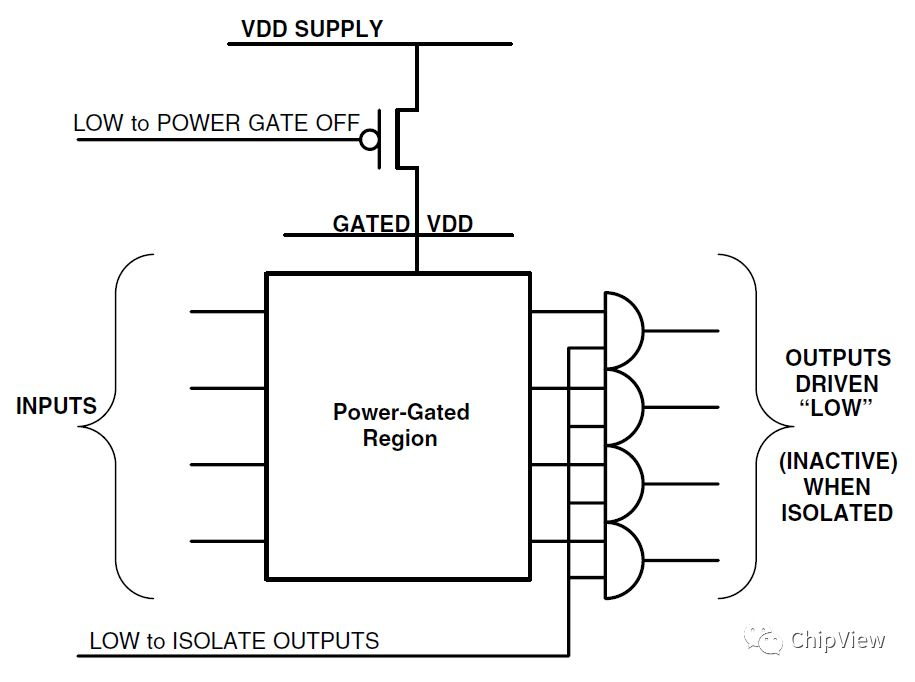

綜上所述,為簡化設計,建議使用Header-Switch型別的電源門控網路,使用高電平有效的訊號和低電平有效的復位,將所有輸出訊號鉗位為0,該設計的簡化原理圖如圖 5所示。

圖 5 簡化後的電源門控設計

5.2.4 訊號隔離的建議

-

對電源門控模組的輸出進行隔離。

-

使用與/或門形式的隔離單元。

-

確保隔離控制訊號在測試期間被鉗位到0/1時可以檢測到隔離是否生效。

-

確保隔離單元始終處於上電狀態。

-

避免出現在電源門控模組中產生時鐘並輸出到外部模組中使用的設計,因為時鐘上的隔離會使時鐘樹綜合和時序收斂變得複雜。

============正文結束===========

掃描下面的二維碼,閱讀其他章節。