LPMM閱讀筆記——第五章 電源門控設 part2

第五章 電源門控設 part2

5.3 狀態保持和恢復方法當模組掉電時,所有的狀態資訊都會丟失,如果想要模組在重新上電後能繼續掉電之前的工作,則需要對一些關鍵的狀態和資訊進行儲存,並在上電後恢復,有三種方法可以儲存和恢復電源門控模組的內部資訊:

• 基於軟體讀寫暫存器的方法;

• 基於掃描的方法,使用掃描鏈將狀態資訊儲存在晶片外;

• 使用保持暫存器;

使用軟體讀寫暫存器的方法是在模組要掉電的時候,使用始終上電的處理器將被門控模組的暫存器讀出來放在memory中,當模組上電後,處理器從memory讀出後寫回到模組中,該方法有以下幾個方面的缺點:

1) 匯流排互動增加了模組下電和上電所需的時間;

2) 匯流排衝突使資訊儲存/恢復所需的時間變得不確定,從而難以確定模組的電源何時可以關閉;

3) 需要在軟體中增加額外的保持和恢復驅動;

鑑於軟體讀寫寄存的方法有上述缺點,下面重點關注另外兩種方法;

5.3.1 使用掃描鏈儲存狀態

使用掃描鏈儲存狀態的方法是利用測試時的掃描鏈,在下電時,將下電模組的暫存器像測試時那樣,通過掃描鏈輸出到片內/片外的RAM中,在上電過程中,在將RAM中的資料通過掃描鏈移回到模組內部的暫存器中,由於操作過程中所使用的掃描鏈是複用測試時的掃描鏈,所以該方法幾乎不會有面積上的額外開銷,此外,一旦要掉電模組的狀態被掃描鏈移到memory中後,整個模組可以完全關閉電源,但這樣對於設計來說有如下挑戰:

1) 從RTL的角度看,掃描鏈是在綜合後才插入的,但是我們希望在RTL階段就能進行低功耗的功能和控制器的驗證;

2) 暫存器的數量以及掃描鏈的長度需要在初步實現後確定,所以在RTL階段進行控制器設計時需要對這些內容進行引數化;

3) 為了快速儲存和恢復,需要使用多條掃描鏈,結合memory位寬,一般使用8或者8n條掃描鏈,要求這些掃描鏈的長度一致,對於短了的掃描鏈而言,應該新增額外的暫存器來補齊;

4) 將狀態暫存器移出/重新移入也需要消耗很多的能量,即使是使用內部的RAM,掃描鏈上的暫存器可能會同時翻轉,產生較大的動態電流,若使用外部RAM,則在IO上還需要消耗部分能量;

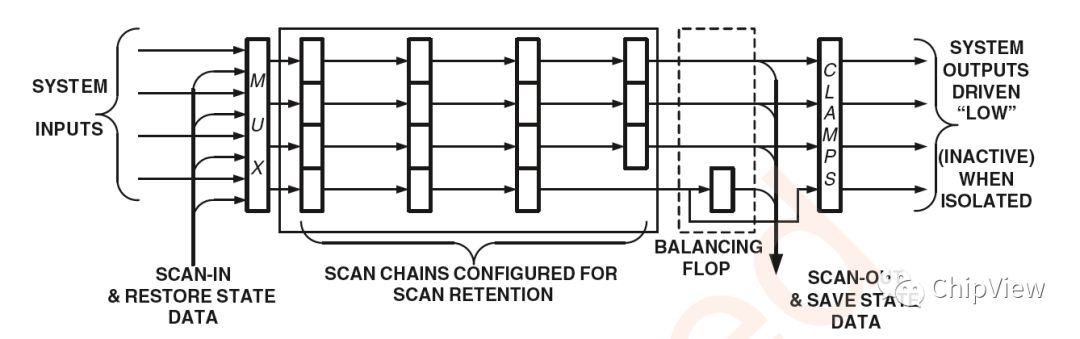

儘管存在上述挑戰,在某些情況下,基於掃描鏈的狀態儲存還是非常有用的,例如對於長期下電的子系統而言,通過掃描鏈可以儲存和恢復狀態,而不需要再上電後從復位狀態開始工作,對於功耗的節省來說更加明顯;圖 1所示是基於4bits掃描鏈的儲存/恢復簡圖,圖中有一條較短的掃描鏈使用了額外的寄存來補齊了。

圖 1 基於掃描鏈的狀態儲存

在RTL階段,可以通過新增一些掃描鏈的功能模型和控制模型在RTL中實現基於掃描鏈的低功耗模擬驗證,書中給出了一個RTL的掃描鏈模型示例,程式碼如下:

`define CPU_SCAN_LEN 257 /* set to implementation length once known */

`ifdef RTL_SLEEP_EMULATE

parameter scan_reg_length = `CPU_SCAN_LEN;

reg [15:0] scanword [0:scan_reg_length-1];

integer i;

/* initialize the scan chain to count pattern, or more draconian X */

initial begin

for (i=0; i < scan_reg_length; i=i+1) begin

scanword[i]<=i; // or 16’hXXXX;

end

end

/* emulate scan shift CPUSI -> CPUSO */

[email protected](posedge CLK) begin

if (CPUSE == 1'b1) /* when SCAN ENABLE is active */

begin

for (i=1; i < scan_reg_length; i=i+1) begin

scanword[i]<=scanword[i-1];

end

scanword[0] <= CPUSI[15:0];

end

end

assign CPUSO [15:0] = scanword[scan_reg_length-1];

`endif

在門級網表release後,就可以使用門級網表進行模擬了,以確保功能、控制、掃描鏈長度和連線的正確性。

5.3.2 保持暫存器

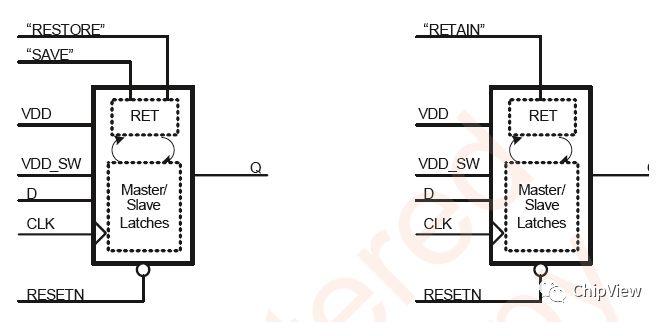

在電源被門控期間,提供狀態儲存的另一種方法是使用保持暫存器替換標準的暫存器,保持暫存器包含一個影子暫存器,可以在掉電期間保持,並在重新上電的時候恢復,影子暫存器時始終上電的,圖 2顯示了兩種型別的保持暫存器,左邊的保持暫存器有兩個控制訊號,當SAVE訊號有效時,狀態從主暫存器載入帶影子暫存器中,當RESTORE訊號有效時,狀態從影子暫存器恢復到主暫存器中,SAVE和RESTORE訊號對電平敏感的訊號;右邊的暫存器只有一個RETAIN控制訊號,該訊號的上升沿時,將主暫存器的值儲存到影子暫存器中,在訊號的下降沿時,將影子暫存器的內容恢復到主暫存器中,RETAIN訊號對邊沿敏感。

圖 2 保持暫存器

實際上保持暫存器都有一些額外的面積上的開銷,通常為20%或更大,一些帶有電壓峰值保護的保持暫存器在面積上的額外開銷甚至大於50%,在具有大量暫存器的設計中這種面積上的增加可能會很大,但這是不可避免的。

5.3.3 帶保持暫存器的電源控制器設計

電源控制器必須管理儲存/恢復狀態的時序,由於影子暫存器比主暫存器慢,所以我們需要確保主暫存器中的值在儲存過程中是穩定的,因此,在狀態儲存時,一般將主暫存器的時鐘停掉,儲存完成後在下電(疑問:儲存暫存器沒有反饋訊號,如何確定狀態儲存已經完成?);在上電時,應該先將狀態從影子暫存器中恢復到主暫存器中以後再恢復時鐘;為避免讀寫衝突,在儲存/恢復時,主暫存器的時鐘和復位應停掉。

5.3.4 全部/部分狀態儲存

對於使用狀態儲存暫存器策略的設計而言,最關鍵的一個決策是在斷電期間,儲存多少狀態資訊?若全部儲存,則可以得到一個最穩健和最易於驗證的設計,但某些設計中,不允許有太多太多額外的面積增加,這樣的情況下,就只能選擇儲存部分暫存器值,這樣會給設計帶來一些挑戰,設計需要保證所有沒有保留的暫存器在重新上電後不會出現X態,且是可以驗證的。

5.4 電源控制器

5.4.1 電源控制序列

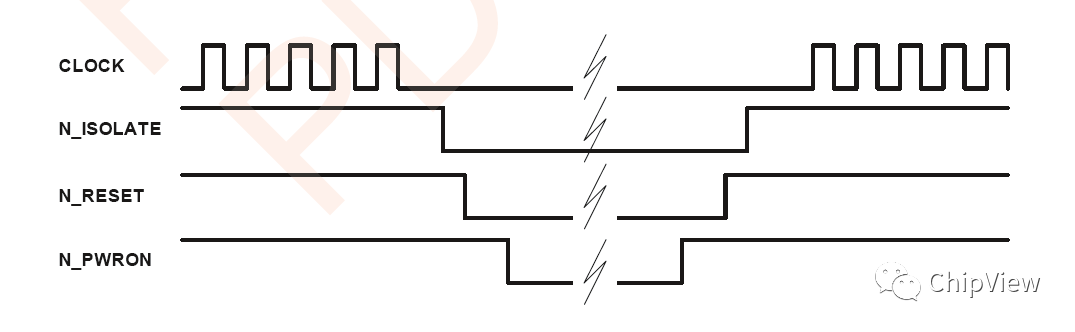

不帶儲存暫存器的下電順序:

1) 結束匯流排和外部操作;

2) 停止時鐘;

3) 隔離輸出訊號;

4) 復位模組;

5) 關閉模組電源;

不帶儲存暫存器的上電順序:

1) 開啟模組電源,使模組重新上電;

2) Release復位;

3) 撤銷隔離;

4) 恢復時鐘;

圖 3所示為不帶儲存暫存器的電源控制序列。

圖 3 不帶保持暫存器的電源控制序列

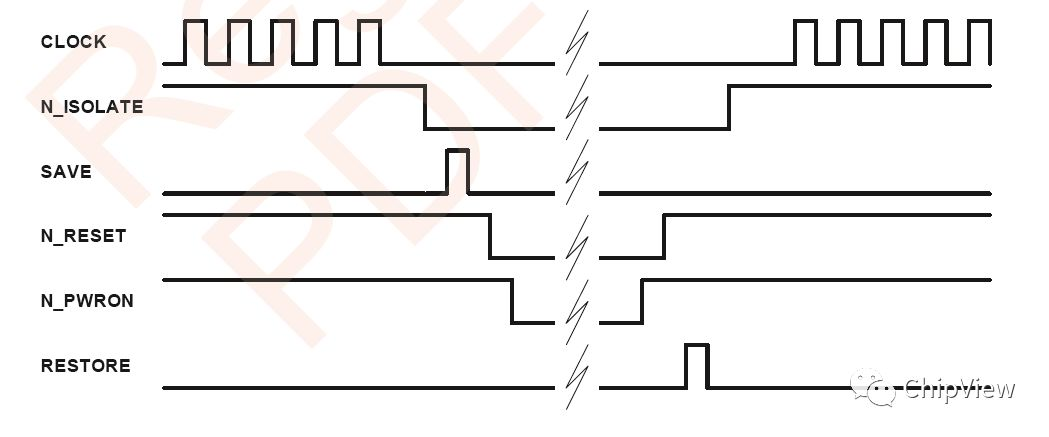

帶儲存暫存器的下電順序:

1) 結束匯流排和外部操作;

2) 停止時鐘;

3) 隔離輸出訊號;

4) 儲存狀態資訊;

5) 復位模組;

6) 關閉模組電源;

不帶儲存暫存器的上電順序:

1) 開啟模組電源,使模組重新上電;

2) Release復位;

3) 恢復儲存的狀態資訊;

4) 撤銷隔離;

5) 恢復時鐘;

圖 4所示為帶儲存暫存器的電源控制序列。

圖 4 帶保持暫存器的電源控制序列

5.4.2 電源開關網路和電源控制器的握手

為避免模組在上/下電時產生尖峰電流,電源門控網路在關斷/開啟過程中都需要一定的延時,控制器需要等到模組上電完成後才能發出下一操作,這樣就要求控制器知道電源門控網路是否完成了上/下電動作,基於此,在電源門控網路中增加一個反饋訊號來實現控制器和電源門控網路間的握手,圖 5所示為電源切換確認序列,在大多數應用中,電源門控網路的ack訊號是非同步的,其延遲取決於電源門控網路的結構設計,控制器在使用之前應先將ack訊號同步到控制器所在的時鐘域下。電源門控控制器設計時還需要考慮一種極端的情況,就是電源下電過程還未完成時又需要對模組上電。

圖 5 電源切換確認序列

書上這一章後面還有兩節分別對電源門控設計的驗證和測試做了介紹,這一部分後續我會單獨整理,所以在此先略過,下一章會從對架構的角度做一些介紹,包括power domain的劃分、層次、多電壓域等。

============正文結束===========

掃描下面的二維碼,閱讀其他章節