使用自由軟體Icarus Verilog Simulator進行模擬

阿新 • • 發佈:2018-12-09

Icarus Verilog Simulator(http://iverilog.icarus.com/home)使用iverilog作為原始碼編譯器,編譯生成vvp程式文字,使用vvp作為執行時引擎,支援vcd波形Dump,支援lxt格式波形,可以使用gtkwave來Debug波形。

各大Linux發行版和Windows系統均可以直接安裝iverilog/gtkwave,iverilog/vvp/gtkwave引數可以通過man *檢視。

一個簡單的Testbench示例:

1 //***********************************************************************************************2 // File : tb_top.sv 3 // Author : Lyu Yang 4 // Date : 2018-12-09 5 // Description : Simple Testbench using iVerilog 6 //*********************************************************************************************** 7 `timescale 1ns/1ns 8 module tb_top; 9 10 logic clk;11 logic [3:0] cnt; 12 13 initial forever #5 clk = ~clk; 14 15 initial begin 16 clk = 0; 17 cnt = 0; 18 repeat(10) 19 begin 20 @(posedge clk); 21 cnt = cnt + 1; 22 $display("@%4t ns: cnt = 0x%-04X", $time, cnt); 23 end 24 #100; 25 $finish; 26 end 2728 initial begin 29 //$dumpfile("tb_top.vcd"); 30 $dumpfile("tb_top.lxt"); 31 $dumpvars(); 32 end 33 34 endmodule

使用上述工具集的Makefile示例:

1 #*********************************************************************************************** 2 # File : Makefile 3 # Author : Lyu Yang 4 # Date : 2018-12-09 5 # Description : Makefile for iVerilog 6 #*********************************************************************************************** 7 8 all: cmp vvp lxt 9 10 cmp: 11 iverilog -g2005-sv tb_top.sv -o tb_top.vvp 12 13 vvp: 14 vvp tb_top.vvp -fst -sdf-verbose -lxt2 15 16 lxt: 17 gtkwave tb_top.lxt & 18 19 clean: 20 @rm -rf tb_top.vvp tb_top.lxt

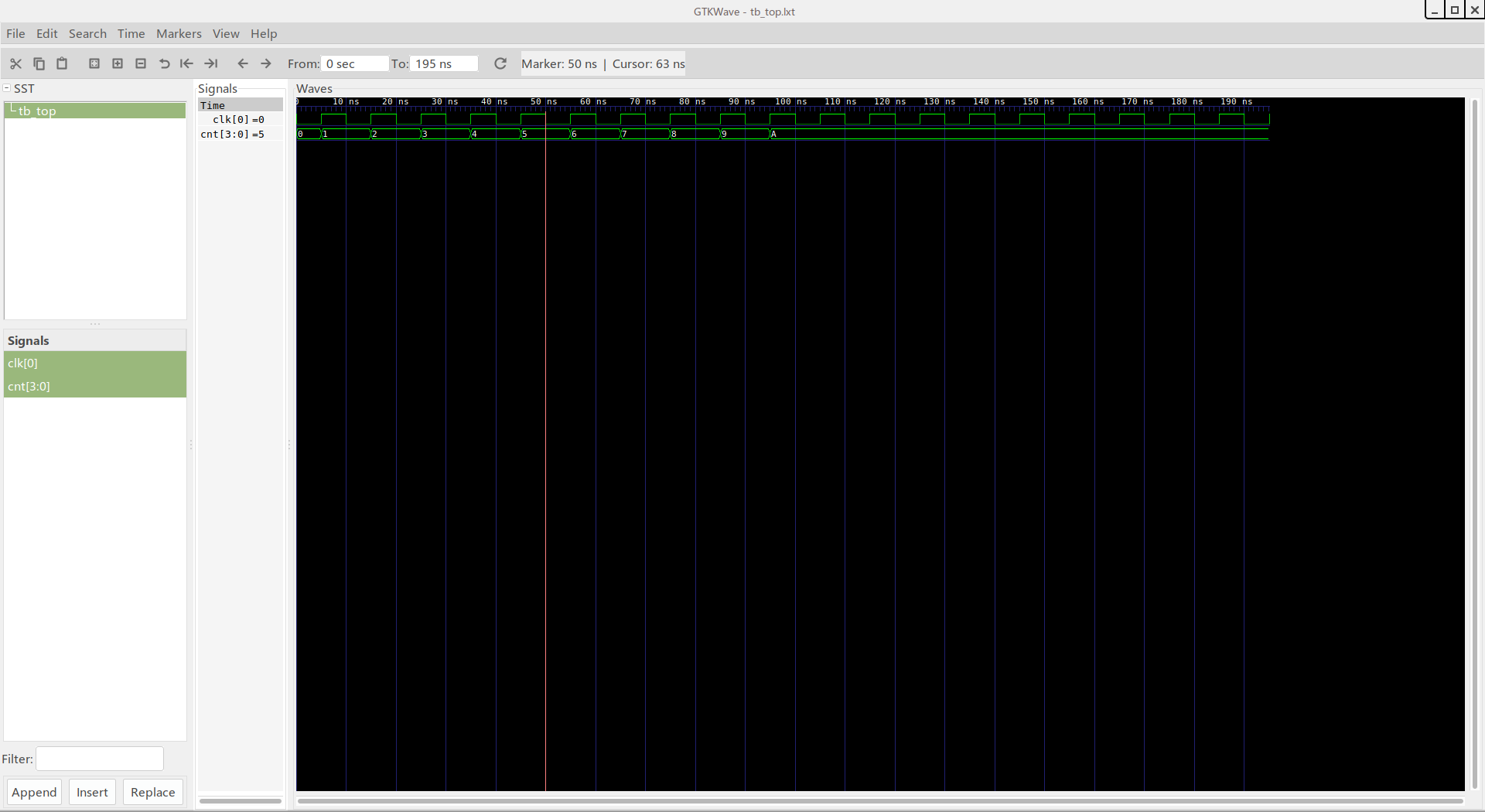

波形視窗: