FPGA基於雙埠RAM的乒乓操作

阿新 • • 發佈:2018-12-11

如果需要重讀,需要用ram,如果不需要重讀的話就用FIFO 雙buffer不太好實現錯誤重傳機制!!!!

雙buffer作用:

1、跨時鐘域

2、完成資料位寬轉換

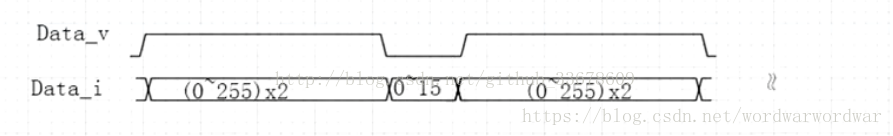

3、完成資料緩衝 雙buffer緩衝操作示意圖,在操作工程中存在兩個clock1 和clock2,但是輸入輸出的傳輸頻寬不能相差太大,會出現資料覆蓋的現象

雙buffer緩衝操作示意圖,在操作工程中存在兩個clock1 和clock2,但是輸入輸出的傳輸頻寬不能相差太大,會出現資料覆蓋的現象 。

1、如上圖所示,輸入端讀資料比寫資料速度要塊,這樣的話,在資料寫完後讓外部來讀,這樣在寫的過程中,空閒的時間,讀端,可以進行資料操作等操作(100MHz * 8bit < 75MHz * 16bit)

2、寫完一次資料就用選擇器選擇另外一個ram寫,在下降沿時切換,讀選擇器類似。

3、快時鐘域向慢時鐘域傳輸訊號時,需要將寫入的片選訊號data|_v延遲兩拍 。

testbeach中產生的資料思路

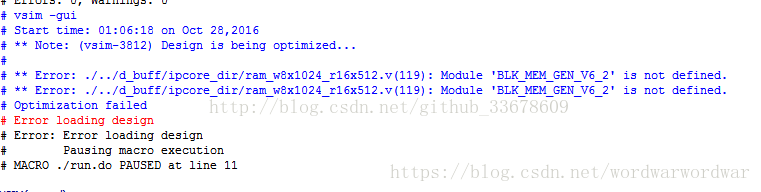

ISE產生的ipcore,不使用ISE自帶的simulation模擬,直接用modulesim模擬時出現加入的ipcore找不到相關檔案,如圖所示

直接到該目錄下搜尋,然後copy出來到你的工程檔案中

原始碼連結:

http://download.csdn.net/detail/github_33678609/9739924