計算機系統結構--複習(Part 4)

本篇是習題專輯

往期回顧:

Part 1(chapter 1 - chapter 5):https://blog.csdn.net/zongza/article/details/83780572

Part 2(chapter 5 - chapter 10):https://blog.csdn.net/zongza/article/details/83933327

Part 3(概念專輯):https://blog.csdn.net/zongza/article/details/84100133

Part 4(習題專輯):https://blog.csdn.net/zongza/article/details/84111578

資料下載:

計算機體系結構-量化研究方法-Hennessy&Patterson著(英文版):https://download.csdn.net/download/zongza/10787837

計算機體系結構-量化研究方法-Hennessy&Patterson著(中文版):https://download.csdn.net/download/zongza/10787840

計算機系統結構教程-第二版-張晨曦著:https://download.csdn.net/download/zongza/10787843

計算機體系結構教程-學習指導與題解:https://download.csdn.net/download/zongza/10793886

流水線

主要知識點:畫出停頓示意圖(縱座標用任務),畫出流水線時空圖(縱座標用流水段或者任務,視情況而定,如果重複執行相同指令就是流水段時空圖,如果執行多條不同指令就是任務時空圖),吞吐率 效率 加速比 的計算,流水線改進(增加硬體,旁路等等)

例1:

假設非流水機單條指令經過相應的5個功能部件的執行時間分別為10ns,8ns,10ns,10ns和7ns,如果實現流水線且每個部件增加了1ns的附加開銷,不考慮其他延遲因素,那麼該流水線的加速比為多少?

例2:

注意這個最大吞吐率的計算! 意思是流水線進入穩定狀態後,一定是每max(...)個時間流出一條指令。

例3:

主要考察流水線停頓

注意:

- 先分析相關(考察的就是相關帶來的stall)

- 任務時空圖是:向下的方向為縱軸 和 向左的方向為橫軸

例4:

主要考察動態流水線的時空圖

例5:

假設非流水線實現的時鐘週期時間為1ns,ALU和分支指令需要4個時鐘週期,訪問儲存器指令需5個時鐘週期,上述指令在程式中出現的相對頻率分別是:40%、20%和40%。在基本的流水線中,假設由於時鐘扭曲和暫存器建立延遲等原因,流水線要在其時鐘週期時間上附加0.2ns的額外開銷。現忽略任何其他延遲因素的影響,請問:相對於非流水實現而言,基本的流水線執行指令的加速比是多少?

例6:

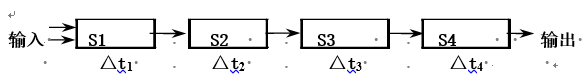

用一條4段浮點加法器流水線求8個浮點數的和: Z=A+B+C+D+E+F+G+H,求流水線的吞吐率、加速比和效率,其中△t1=△t2=△t3=△t4=△t。

答:可對原式作一簡單變化,得到:

Z=[(A+B)+(C+D)]+[(E+F)+(G+H)]

7個加法8個數的流水線時空圖如下:

CPI計算

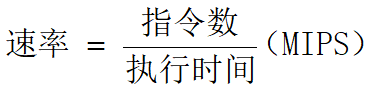

主要知識點:CPI計算,MIPS計算,程式執行時間

例1:

例2:

新CPI的計算 old-

例3:

例4:

新CPI的計算 base+

例5:

例6:

某RISC處理機各類指令使用頻率和理想CPI(指令和資料訪問Cache命中率為100%時的CPI)如下表所示。而實際測得的指令訪問Cache缺失率(miss rate)為5%,資料訪問的Cache缺失率為10%,Cache的缺失損失(miss penalty)為40個時鐘週期。

1)該機器在無Cache缺失(理想情況)時的CPI是多少?(3分)

2)該機器在無Cache缺失(理想情況)時的速度比有Cache缺失時快幾倍?(4分)

| 指令型別 |

ALU操作 |

Loads |

Stores |

Branches |

| 使用頻率 |

43% |

21% |

12% |

24% |

| CPI ideal |

1 |

2 |

2 |

2 |

1)CPI=43%X1+21%X2+12%X2+24%X2=1.57

2)對指令講,指令Cache的訪問佔全部訪問的100%/(100%+21%+12%)=75%

對資料來講,資料Cache的訪問佔全部訪問的(21%+12%)/(100%+21%+12%)=25%

new_cpi=base+失效率X失效開銷

=1.57+(75%X5%+25%X10%)X40=1.57+2.5=4.07

則:4.07/1.57=2.59=2.6 大約快2.6倍

阿姆達爾定律

例1:

例2:

例3:

指令集架構(從多地址的向下擴充套件)

例1:

某計算機的指令字長16位,設有單地址指令和兩地址指令兩類指令,若每個地址子段均為6位,且兩地址指令有A條,問單地址指令最多可以有多少?

答:

雙地址指令結構為:(4位操作碼)(6位地址碼)(6位地址碼)

單地址指令結構為:(10位操作碼)(6位地址碼)

因此,每少一條雙地址指令,則多2^6條單地址指令,

雙地址指令最多是2^(16-6-6)=2^4=16條 ,

所以單地址指令最多有(16-X)*2^6條。

例2:

若某機要求有:三地址指令4條,單地址指令192條,零地址指令16條。設指令字長為12位,每個地址碼長3位。問能否以擴充套件操作碼為其編碼?

答:能,如下:

例3:

若某機要求:三地址指令4條,單地址指令255條,零地址指令16條。設指令字長為12位.每個地址碼長為3位。問能否以擴充套件操作碼為其編碼?如果其中單地址指令為254條呢?說明其理由。

解:

(1)不能用擴充套件碼為其編碼。

指令字長12位,每個地址碼佔3位,三地址指令最多是2^(12-3-3-3)=8條, 現三地址指令需4條,

所以可有4條編碼作為擴充套件碼,而單地址指令最多為4×2^3×2^3=2^8=256條,現要求單地址指令255條,

所以可有一條編碼作擴充套件碼

因此零地址指令最多為1×2^3=8條

不滿足題目要求,故不可能以擴充套件碼為其編碼。

(2)若單地址指令254條,可以用擴充套件碼為其編碼。

依據(1)中推導,單地址指令中可用2條編碼作為擴充套件碼,零地址指令為2×2^3=16條,滿足題目要求

Cache平均訪問時間

例1:

答:

例2:

答:

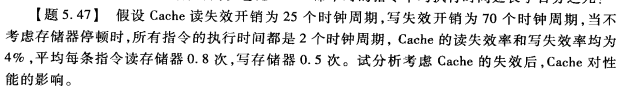

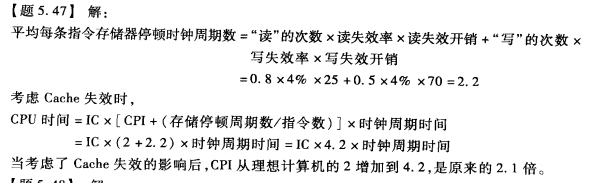

CPU時間(也可以看成CPI的計算)

例1:

答:注意這裡不是求平均訪問時間,而是計算停頓開銷(=miss_rate * miss_pernalty)

頁表計算

例1:

一個有快表和慢表的頁式虛擬儲存器,最多有64個使用者,每個使用者最多要用1024個頁面,每頁4K位元組,主存容量8M位元組。

(1)寫出多使用者虛地址的格式,並標出各欄位的長度。

(2)寫出主存地址的格式,並標出各欄位的長度。

(3)快表的字長為多少位?分幾個欄位?各欄位的長度為多少位?

(4)慢表的容量是多少個儲存字?每個儲存字的長度為多少位?

答:

使用者號:64=26,虛頁號:1024=210,頁內地址:4K=212,主存頁數:8M/4K=211

(1)多使用者虛地址:

使用者號(6位)+虛頁號(10位)+頁內地址(12位) 共28位

(2)主存地址:

主存實頁號(11位)+頁內地址(12位) 共23位

(3)快表字長27位;分3個欄位:使用者號6位,虛頁號10位,實頁號11位

(4)慢表容量為2(6+10),每個儲存字長為:主存頁號+1=12位。

相關分支預測狀態機:

例1:

例2: