AC620FPGA學習筆記——ROM資料顯示

阿新 • • 發佈:2018-12-11

AC620FPGA學習筆記——ROM資料顯示

ROM資料顯示

工程地址:https://github.com/HaHaHaHaHaGe/Planof2019_half/tree/master/Course_Project/FPGA/class05_onchipROM

基於數碼管的專案增添ROM資料輸出

硬體結構

開發板:AC620

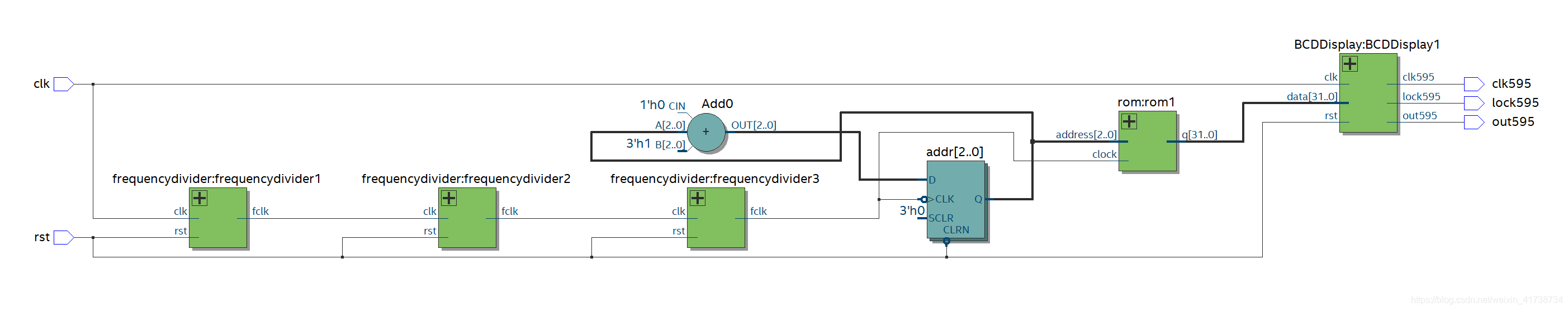

整體框架

注ROM是由IP生成的生成步驟如下:

建立mif/hex檔案

IP核建立

在IP核配置中匯入mif/hex檔案

完成

IP核配置

選擇ip核生成檔案儲存的位置

配置rom大小(位寬與words)以及儲存器選擇

埠控制配置

mif/hex檔案匯入

程式碼部分

程式碼過多更多程式碼在github

頂層程式碼

module top(

rst,

clk,

lock595,

out595,

clk595

);

input rst,clk;

output lock595,out595,clk595;

wire clk1;

wire clk2;

wire clk3;

wire [31:0]data;

reg [2:0]addr;

frequencydivider frequencydivider1