開關電源UVLO的遲滯(Hysteresis)的含義

關心遲滯的目的在於可以考察在開關電源上電和下電兩種情況下的電平門限值。

任何只給出UVLO和Hysteresis的值,不給測試條件的都是耍流氓。

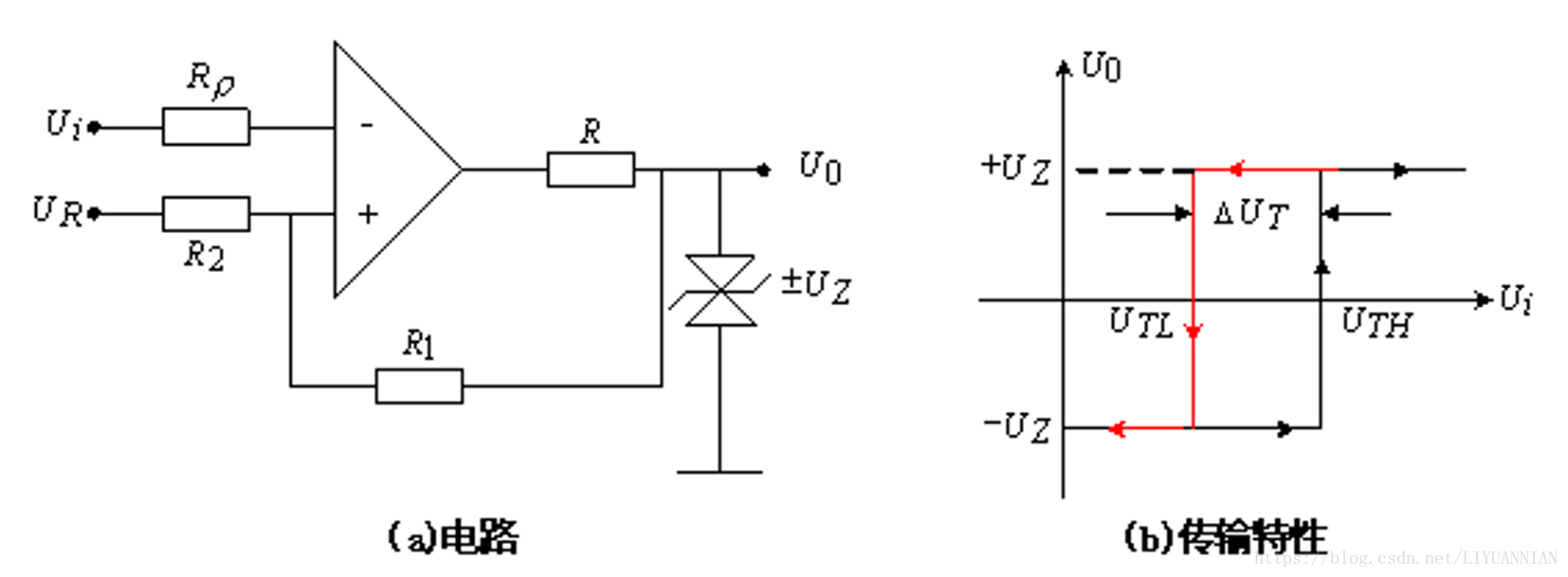

圖1 同相遲滯比較器的電路和傳輸特性

上圖(b)中可以看出,當Ui > UTH,U0 = +Uz;當Ui < UTL,U0 = -Uz。上圖的ΔUT(=UTH-UTL)就是Hysteresis。

下面用例子介紹下開關電源中的這兩個概念。

圖 2 LM27403的輸入電壓UVLO和Hysteresis的值(來自於LM27403手冊)

圖 3 VUVLO2和VUVLO1的含義(來自於LM27403手冊)

圖2中可以看出,在開關電源的上電階段,UVLO/EN引腳電壓上升到VUVLO2後開關電源開始使能輸出;在開關電源的下電階段,UVLO/EN引腳電壓下降到VUVLO1後開關電源禁止輸出。VUVLO2(Logic high threshold,1.150V)和VUVLO1(Logic low threshold,0.985V)的值不同,有一個差值VUVLO-HYS=165mV,這個值就是UVLO的遲滯Hysteresis。

因此,VUVLO2就是圖1中的UTH,VUVLO1就是圖1中的UTL,VUVLO-HYS就是圖1的ΔUT。

以下是TPS54620的VIN UVLO的遲滯。

圖 4 TPS54620 VIN UVLO的遲滯

上圖可以看出,在VIN rising的測試條件下,VIN internal UVLO threshold = 4.0V(典型值),因此此值對應圖1中的UTH,且UTL = UTH - hysteresis = 4.0V - 0.15V = 3.85V。

若上圖的測試條件不是VIN rising,而是VIN falling,則上圖的4.0V對應圖1中的UTL,且UTH = UTL + hysteresis = 4.0V + 0.15V = 4.15V。

因此重點是要關注測試條件。

下面給出LM83的例子。

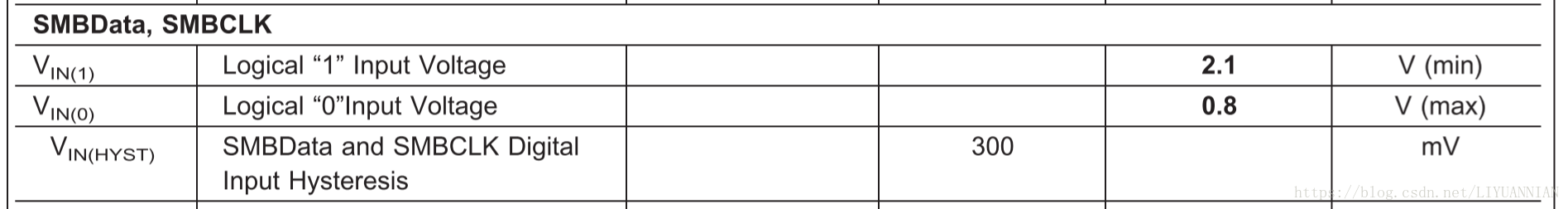

圖5 LM83的SMBData和SMBCLK VIN的Hysteresis引數

上圖沒有明確給出測試條件,但是Logical "1"的測試條件是VIN rising,因此VIN(1) = 2.1V對應圖1中的UTH,UTL = 2.1V - 0.3V = 1.8V;Logical "0"的測試條件是VIN falling,因此VIN(0) = 0.8V對應圖1中的UTL,UTH = 0.8V + 0.3V = 1.1V。