51微控制器學習筆記——STC15W201S系列

阿新 • • 發佈:2018-12-13

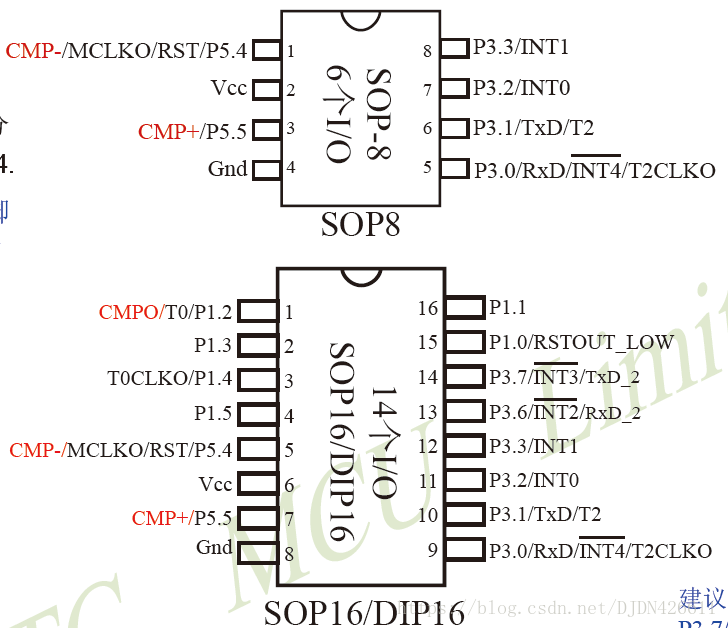

下圖為STC15W201S系列微控制器引腳圖:

主要使用SOP16封裝的STC15W204S。

下表為管腳說明:

| 管腳 | 封裝/SOP16 | 說明 | |

| P1.0/RSTOUT_LOW | 15 | P1.0 | 標準I/O口 PORT1[0] |

| RSTOUT_LOW | 上電後,輸出低電平,在復位期間也是輸出低電平,使用者可用軟體將其設定為高電平或低電平,如果要讀外部狀態,可將該口先置高後再讀。 | ||

| P1.1 | 16 | 標準I/O口 PORT1[1] | |

| P1.2/T0/CMPO | 1 | P1.2 | 標準I/O口 PORT1[2] |

| T0 | 定時器/計數器0的外部輸入 | ||

| CMPO | 比較器的比較結果輸出管腳 | ||

| P1.3 | 2 | 標準I/O口 PORT1[3] | |

| P1.4/T0CLKO | 3 | P1.4 | 標準I/O口 PORT1[4] |

| T0CLKO |

定時器/計數器0的時鐘輸出 可通過設定INT_CLKO[0]位/T0CLKO將該管腳配置為T0CLKO,也可對T0腳的外部時鐘輸入進行分頻輸出 |

||

| P1.5 | 4 | 標準I/O口 PORT1[5] | |

| P3.0/RxD/INT4/T2CLKO | 9 | P3.0 | 標準I/O口 PORT3[0] |

| RxD | 串列埠資料接收端 | ||

| INT4 | 外部中斷4,只能下降沿中斷,INT4支援掉電喚醒 | ||

| T2CLKO |

T2的時鐘輸出 可通過設定INT_CLKO[2]位/T2CLKO將該管腳配置為T2CLKO |

||

| P3.1/TxD/T2 | 10 | P3.1 | 標準I/O口 PORT3[1] |

| TxD | 串列埠資料傳送端 | ||

| T2 | 定時器/計數器2的外部輸入 | ||

| P3.2/INT0 | 11 | P3.2 | 標準I/O口 PORT3[2] |

| INT0 |

外部中斷0,既可上升沿中斷也可下降沿中斷。 如果IT0(TCON.0)被值為1,INT0管腳僅為下降沿中斷。如果IT0(TCON.0)被清0,INT0管腳既可上升沿中斷也可下降沿中斷。 INT0支援掉電喚醒。 |

||

| P3.3/INT1 | 12 | P3.3 | 標準I/O口 PORT3[3] |

| INT1 |

外部中斷1,既可上升沿中斷也可下降沿中斷。 如果IT1(TCON.2)被值為1,INT1管腳僅為下降沿中斷。如果IT1(TCON.2)被清0,INT1管腳既可上升沿中斷也可下降沿中斷。 INT1支援掉電喚醒。 |

||

| P3.6/INT2/RxD_2 | 13 | P3.6 | 標準I/O口 PORT3[6] |

| INT2 |

外部中斷2,只能下降沿中斷 INT2支援掉電喚醒 |

||

| RxD_2 | 串列埠資料接收端 | ||

| P3.7/INT3/TxD_2 | 14 | P3.7 | 標準I/O口 PORT3[7] |

| INT3 |

外部中斷3,只能下降沿中斷 INT3支援掉電喚醒 |

||

| TxD_2 | 串列埠資料傳送端 | ||

| P5.4/RST/MCLKO/CMP- | 5 | P5.4 | 標準I/O口 PORT5[4] |

| RST | 復位腳(高電平復位) | ||

| MCLKO | 主時鐘輸出;輸出的頻率可為MCLK/1,MCLK/2,MCLK/4(MCLK是指主時鐘頻率)。 | ||

| CMP- |

比較器負極輸入端 (若該口被用作比較器負極,該口需被設定為高阻輸入) |

||

| P5.5/CMP+ | 7 |

P5.5 |

標準I/O口 PORT5[5] |

| CMP+ |

比較器正極輸入端 (若該口被用作比較器正極,該口需被設定為高阻輸入) |

||

| Vcc | 6 | 電源正極 | |

| Gnd | 8 | 電源負極,接地 | |