51微控制器學習筆記——SH88F4051A

阿新 • • 發佈:2018-12-13

一、概述

SH88F2051A/4051A是一種高速高效率8051可相容微控制器。在同樣振盪頻率下,較之傳統的8051晶片它有著執行更快速的優越特性。

SH88F2051A/4051A保留了標準2051晶片的大部分特性。這些特性包括內建256位元組RAM和2個16位定時器/計數器,1個UART和外接中斷INT0,INT1,INT2。此外,SH88F2051A/4051A還集成了256位元組外部RAM,可相容8052晶片的16位定時器/計數器(Timer2)。該微控制器還包括適合於程式和資料的4K/8K位元組Flash塊。

SH88F2051A/4051A不僅集成了EUART標準通訊模組,此外還集成了具有內建比較功能的ADC,PWM定時器等模組。

為了達到高可靠性和低功耗,SH88F2051A/4051A內建看門狗定時器,低電壓復位功能和低電壓檢測功能。此外SH88F2051A/4051A還提供了2種低功耗省電模式。

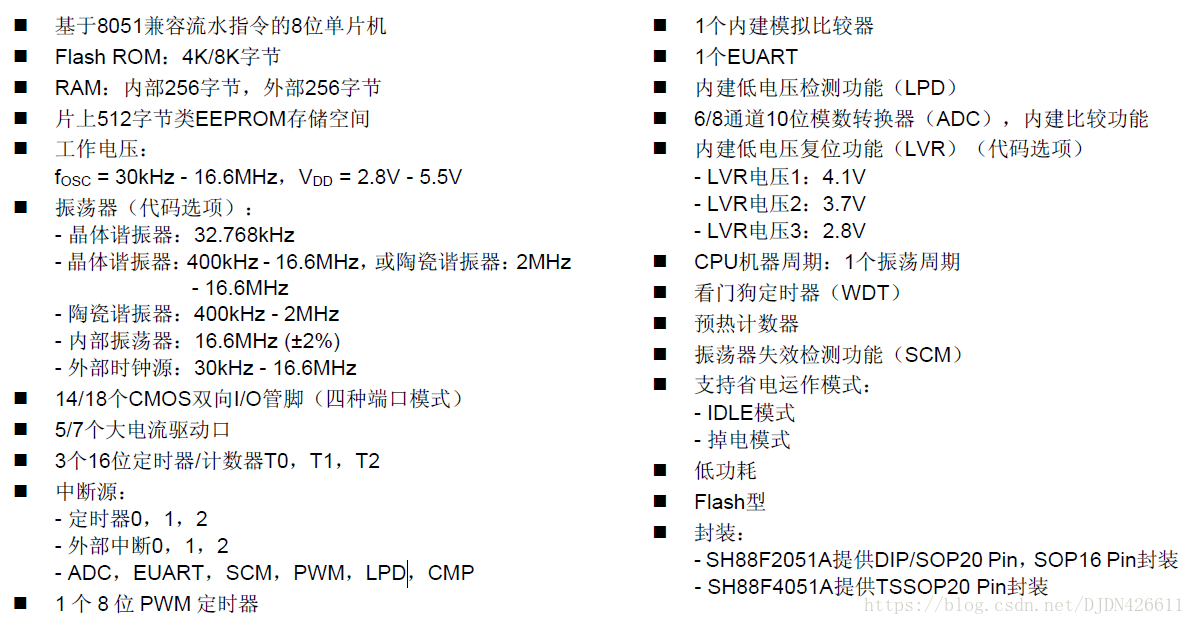

二、特性

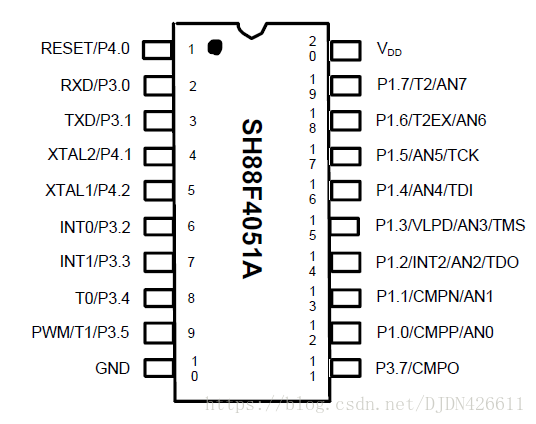

三、TSSOP 20腳封裝

注意:引腳命名中,寫在最外側的引腳功能具有最高優先順序,最內側的引腳功能具有最低優先順序(參見引腳配置圖)。當一個引腳被高優先順序的功能佔用時,即使低優先順序功能被允許,也不能作為低優先順序功能的引腳。只有當軟體禁止引腳的高優先順序功能,相應引腳才能被釋放作為低優先順序埠使用。

四、引腳功能

| 引腳編號 | 引腳命名 | 預設功能 |

| TSSOP | ||

| 1 | P4.0/RESET | RESET |

| 2 | RXD/P3.0 | P3.0 |

| 3 | TXD/P3.1 | P3.1 |

| 4 | P4.1/XTAL2 | P4.1或振盪器輸出引腳,程式碼選項控制 |

| 5 | P4.2/XTAL1 | P4.2或振盪器輸入引腳,程式碼選項控制 |

| 6 | INT0/P3.2 | P3.2 |

| 7 | INT1/P3.3 | P3.3 |

| 8 | T0/P3.4 | P3.4 |

| 9 | PWM/T1/P3.5 | P3.5 |

| 10 | GND | --- |

| 11 | CMPO/P3.7 | P3.7 |

| 12 | AN0/CMPP/P1.0 | P1.0 |

| 13 | AN1/CMPN/P1.1 | P1.1 |

| 14 | TDO/AN2/INT2/P1.2 | P1.2 |

| 15 | TMS/AN3/VLPD/P1.3 | P1.3 |

| 16 | TDI/AN4/P1.4 | P1.4 |

| 17 | TCK/AN5/P1.5 | P1.5 |

| 18 | AN6/T2EX/P1.6 | P1.6 |

| 19 | AN7/T2/P1.7 | P1.7 |

| 20 | VDD | --- |

五、引腳描述

| 引腳編號 | 型別 | 說明 |

| PORT | ||

| P4.0 - P4.2 | I/O | 3位雙向I/O口 |

| P3.0 - P3.7 | I/O | 7位雙向I/O口 |

| P1.0 - P1.7 | I/O | 8位雙向I/O口 |

| Timer | ||

| T0 | I/O | Timer0外部輸入或比較輸出 |

| T1 | I/O | Timer1外部輸入或比較輸出 |

| T2 | I/O | Timer2外部輸入或比較輸出 |

| T2Ex | I | Timer2過載/捕捉/方向控制 |

| PWM控制器 | ||

| PWM | O | 8位PWM定時器輸出引腳 |

| EUART | ||

| RXD | I | EUART資料輸入引腳 |

| TXD | O | EUART資料輸出引腳 |

| ADC | ||

| AN0 - AN7 | I | ADC輸入通道 |

| CMP | ||

| CMPN | I | CMP負向輸入通道 |

| CMPP | I | CMP正向輸入通道 |

| CMPO | O | CMP輸出通道 |

| 中斷&復位&時鐘&電源 | ||

| INT0 - INT2 | I | 外部中斷0-2 |

| RESET | I | 復位引腳(高電平復位) |

| XTAL1 | I | 諧振器輸入 |

| XTAL2 | O | 諧振器輸出 |

| VDD | P | 電源(2.8 - 5.5V) |

| GND | P | 接地 |

| VLPD | ||

| VLPD | I | 電源電壓輸入檢測 |

| 程式設計器 | ||

| TDO | O | 除錯介面:測試資料輸出 |

| TMS | I | 除錯介面:測試模式選擇 |

| TDI | I | 除錯介面:測試資料輸入 |

| TCK | I | 除錯介面:測試時鐘輸入 |

| 注意: 當P1.2-1.5作為除錯介面時,P1.2-1.5的原有功能被禁止 | ||