DRAM 原理 1 :DRAM Storage Cell

1. Storage Capacitor

DRAM Storage Cell 使用 Storage Capacitor 來儲存 Bit 資訊。

從原理層面上看,一個最簡單的,儲存一個 Bit 資訊的 DRAM Storage Cell 的結構如下圖所示:

由以下 4 個部分組成:

- Storage Capacitor,即儲存電容,它通過儲存在其中的電荷的多和少,或者說電容兩端電壓差的高和低,來表示邏輯上的 1 和 0。

- Access Transistor,即訪問電晶體,它的導通和截止,決定了允許或禁止對 Storage Capacitor 所儲存的資訊的讀取和改寫。

- Wordline,即字線,它決定了 Access Transistor 的導通或者截止。

- Bitline,即位線,它是外界訪問 Storage Capacitor 的唯一通道,當 Access Transistor 導通後,外界可以通過 Bitline 對 Storage Capacitor 進行讀取或者寫入操作。

Storage Capacitor 的 Common 端接在 Vcc/2。 當 Storage Capacitor 儲存的資訊為 1 時,另一端電壓為 Vcc,此時其所儲存的電荷

Q = +Vcc/2 / C

當 Storage Capacitor 儲存的資訊為 0 時,另一端電壓為 0,此時其所儲存的電荷

Q = -Vcc/2 / C

1.1 資料讀寫原理

從上面的結構圖上分析,我們可以很容易的推測出 DRAM Storage Cell 的資料讀寫流程:

- 讀資料時,Wordline 設為邏輯高電平,開啟 Access Transistor,然後讀取 Bitline 上的狀態

- 寫資料時,先把要寫入的電平狀態設定到 Bitline 上,然後開啟 Access Transistor,通過 Bitline 改變 Storage Capacitor 內部的狀態。

然而,在具體實現上,如果按照上面的流程對 DRAM Storage Cell 進行讀寫,會遇到以下的問題:

-

外界的邏輯電平與 Storage Capacitor 的電平不匹配 由於 Bitline 的電容值比 Storage Capacitor 要大的多(通常為 10 倍以上),當 Access Transistor 導通後,如果 Storage Capacitor 儲存的資訊為 1 時,Bitline 電壓變化非常小。外界電路無法直接通過 Bitline 來讀取 Storage Capacitor 所儲存的資訊。

-

進行一次讀取操作後,Storage Capacitor 儲存的電荷會變化 在進行一次讀取操作的過程中,Access Transistor 導通後,由於 Bitline 和 Storage Capacitor 端的電壓不一致,會導致 Storage Capacitor 中儲存的電荷量被改變。最終可能會導致在下一次讀取操作過程中,無法正確的判斷 Storage Capacitor 記憶體儲的資訊。

-

由於 Capacitor 的物理特性,即使不進行讀寫操作,其所儲存的電荷都會慢慢變少 這個特性要求 DRAM 在沒有讀寫操作時,也要主動對 Storage Capacitor 進行電荷恢復的操作。

為解決上述的問題,DRAM 在設計上,引入了 Differential Sense Amplifier。

2. Differential Sense Amplifier

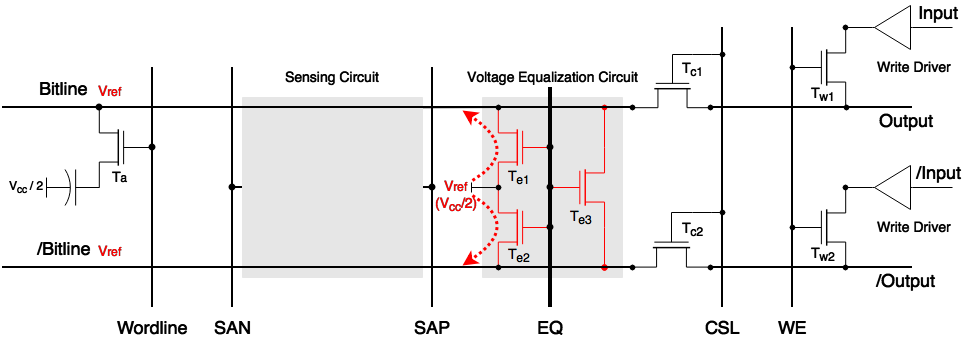

Differential Sense Amplifier 包含 Sensing Circuit 和 Voltage Equalization Circuit 兩個主要部分。它主要的功能就是將 Storage Capacitor 儲存的資訊轉換為邏輯 1 或者 0 所對應的電壓,並且呈現到 Bitline 上。同時,在完成一次讀取操作後,通過 Bitline 將 Storage Capacitor 中的電荷恢復到讀取之前的狀態。

在後面的小節中,我們通過完整的資料讀取和寫入過程,來了解 Differential Sense Amplifier 工作原理。

2.1 Read Operation

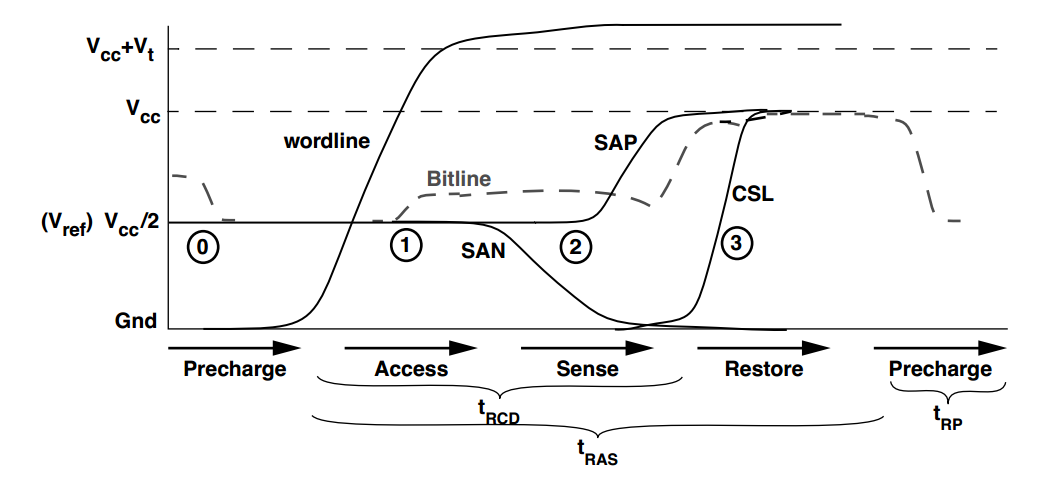

一個完整的 Read Operation 包含了,Precharge、Access、Sense、Restore 四個階段。後續的小節中,將描述從 Storage Capacitor 讀取 Bit 1 的完整過程。

2.1.1 Precharge

在這個階段,首先會通過控制 EQ 訊號,讓 Te1、Te2、Te3 電晶體處於導通狀態,將 Bitline 和 /Bitline 線上的電壓穩定在 Vref 上, Vref = Vcc/2。然後進入到下一個階段。

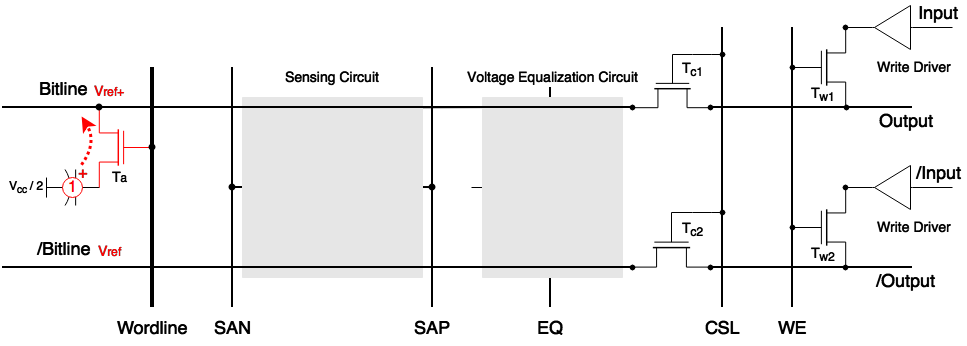

2.1.2 Access

經過 Precharge 階段, Bitline 和 /Bitline 線上的電壓已經穩定在 Vref 上了,此時,通過控制 Wordline 訊號,將 Ta 電晶體導通。Storage Capacitor 中儲存正電荷會流向 Bitline,繼而將 Bitline 的電壓拉昇到 Vref+。然後進入到下一個階段。

2.1.3 Sense

由於在 Access 階段,Bitline 的電壓被拉昇到 Vref+,Tn2 會比 Tn1 更具導通性,Tp1 則會比 Tp2 更具導通性。 此時,SAN (Sense-Amplifier N-Fet Control) 會被設定為邏輯 0 的電壓,SAP (Sense-Amplifier P-Fet Control) 則會被設定為邏輯 1 的電壓,即 Vcc。由於 Tn2 會比 Tn1 更具導通性,/Bitline 上的電壓會更快被 SAN 拉到邏輯 0 電壓,同理,Bitline 上的電壓也會更快被 SAP 拉到邏輯 1 電壓。接著 Tp1 和 Tn2 進入導通狀態,Tp2 和 Tn1 進入截止狀態。 最後,Bitline 和 /Bitline 的電壓都進入穩定狀態,正確的呈現了 Storage Capacitor 所儲存的資訊 Bit。

2.1.4 Restore

在完成 Sense 階段的操作後,Bitline 線處於穩定的邏輯 1 電壓 Vcc,此時 Bitline 會對 Storage Capacitor 進行充電。經過特定的時間後,Storage Capacitor 的電荷就可以恢復到讀取操作前的狀態。

最後,通過 CSL 訊號,讓 Tc1 和 Tc2 進入導通狀態,外界就可以從 Bitline 上讀取到具體的資訊。

2.1.5 Timing

整個 Read Operation 的時序如下圖所示,其中的 Vcc 即為邏輯 1 所對應的電壓,Gnd 為邏輯 0。

3. Write Operation

Write Operation 的前期流程和 Read Operation 是一樣的,執行 Precharge、Access、Sense 和 Restore 操作。差異在於,在 Restore 階段後,還會進行 Write Recovery 操作。

3.1 Write Recovery

在 Write Recovery 階段時,通過控制 WE (Write Enable) 訊號,讓 Tw1 和 Tw2 進入導通狀態。此時,Bitline 會被 input 拉到邏輯 0 電平,/Bitline 則會被 /input 拉到邏輯 1 電平。 經過特定的時間後,當 Storage Capacitor 的電荷被 Discharge 到 0 狀態時,就可以通過控制 Wordline,將 Storage Capacitor 的 Access Transistor 截止,寫入 0 的操作就完成了。

4. 參考資料

- Memory Systems - Cache Dram and Disk

原創文章,轉發請註明出處。蝸窩科技