三叔學FPGA系列之1:Cyclone V中的時鐘資源

之前的專案中更多的是有師兄提供經驗和幫助,追求的是快速上手,所以不管對於硬體電路設計,還是verilog電路程式設計,甚至是FPGA內部的資源,都沒來得及系統地學習,最近在做演算法到電路的實現,正好系統學習,將感悟記於此,如有錯誤,歡迎指出、討論。

一、關於時鐘引腳

FPGA晶片一般有好幾組時鐘引腳 CLK [0..N] [p,n],我的理解是:首先,時鐘必須由外部晶振通過CLK引腳輸入到FPGA的時鐘網路,至於選用哪一組CLK,主要看FPGA哪個bank對時鐘要求最為苛刻;其次,一般用p端,n端由quartus置位三態;再次,對於簡單的系統,只有一組CLK輸入作為系統主時鐘,其他時鐘引腳空置,或者作為某些高帶載能力的時鐘的輸出口(是否可作為輸出口,要看晶片手冊);然後

,複雜系統,可以有不同源的時鐘分別從不同CLK引腳輸入,只是猜想,沒實踐過,個人認為這樣不好,因為FPGA的核心就是同步;另外,不要把CLK引腳和全域性時鐘、區域時鐘什麼的混為一談,一個是時鐘輸入引腳,一個是內部時鐘走線;最後,CLK引腳進去的走線肯定進過優化的(H型銅皮,專用的、直達每個觸發器的佈線資源),所以能做到小的抖動和偏斜,帶載能力也強。

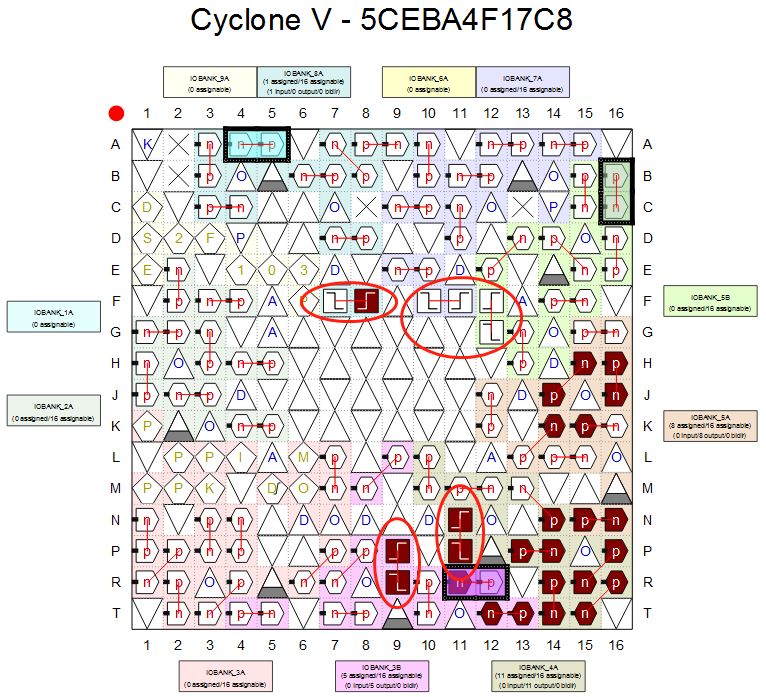

圖1 圖2

圖1所示:紅圈為時鐘輸入引腳,當然,從時鐘引腳輸入的時鐘必定首先進入全域性時鐘網路,再進一步驅動區域時鐘,或者由PLL進行分/倍頻==;三個黑色方框內PLL輸出引腳,我的理解是:這幾組引腳的佈線也經過了優化,可以使PLL分/倍頻後輸出的時鐘訊號質量較好。

圖2所示:CLK9p作為系統唯一的外部輸入時鐘源,需要注意,單端輸入時,只有p端是與內部PLL相連的;CLK1[p,n]作為差分時鐘輸出引腳,由內部PLL驅動,輸出作為AD時鐘。

二、內部時鐘資源

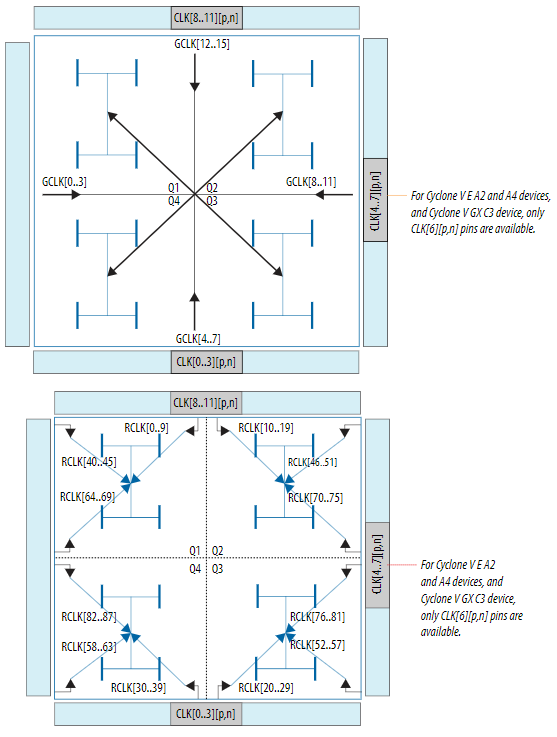

全域性時鐘(GCLK)網路、區域時鐘(RCLK)網路、外設時鐘(PCLK)(一般出現在集成了某些外設的FPGA中,個人理解)網路

- 全域性時鐘:FPGA內部的專用全域性時鐘佈線資源(圖4上),具有直達每一個觸發器的能力,且佈線資源經過優化,時鐘經過它傳輸後具有高扇出、最小的偏斜和抖動等。但也因為是全域性佈線相較於區域時鐘,會有較大的插入延時(手冊也這麼說),而且資源較少(且用且珍惜)。全域性時鐘網路:

1)可由CLK引腳、內部PLL、高速串列埠(HSSI)、普通邏輯電路產生的時鐘(一般不這麼幹)驅動;2)可驅動所有輸出引腳(尤其是CLK引腳,輸出作為其他晶片的基礎時鐘)、內部PLL、區域時鐘。- 區域時鐘:只在他們自己所在的區域有效(圖4下),相當於區域內的全域性時鐘,在區域內,具有全域性時鐘的優點,且插入延時比全域性時鐘小,佈線資源也比較多。區域時鐘網路:1)可由CLK引腳(注意區域)、內部PLL、高速串列埠(HSSI)、普通邏輯電路產生的時鐘(一般不這麼幹)驅動;2)可驅動所有輸出引腳(尤其是CLK引腳,輸出作為其他晶片的基礎時鐘)、內部PLL。

- 外設時鐘:沒用到,查手冊。

圖3 圖4

******注意******

- 常規操作:外部晶振—>時鐘引腳—>PLL—>區域時鐘、各個模組、輸出(待驗證和完善,我也迷)。

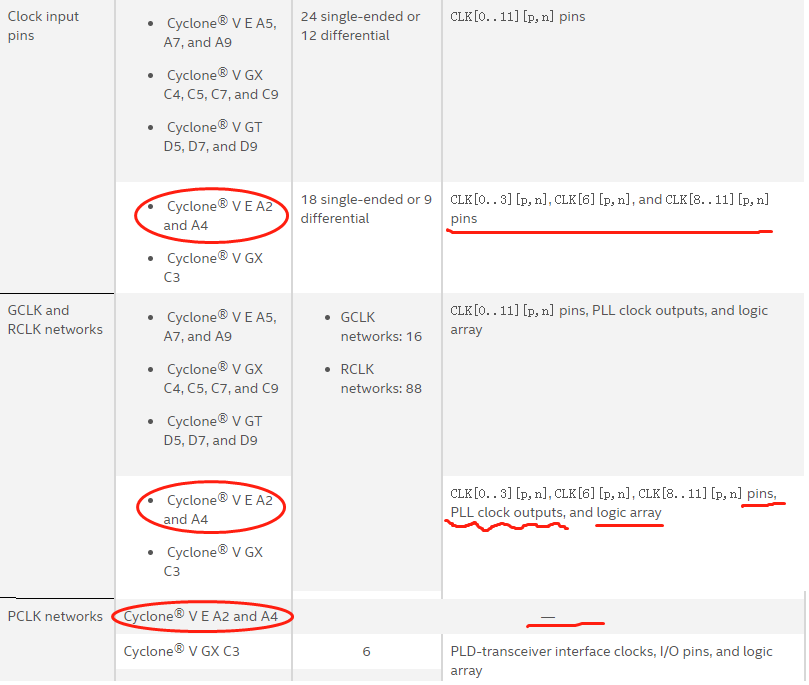

- 關於CLK引腳選擇:不是所有的CLK引腳都可以連線到所有的全域性/區域時鐘網路,見圖5。

- 關於PLL:不是所有始終都可以驅動PLL,詳見手冊,如圖6所示。

圖5

圖6

三、時鐘資源的使用、分配

疑問:編寫邏輯電路,或者佈局佈線時,我怎麼知道某個時鐘具體使用了哪種、哪個網路?以及怎麼人為地控制使用具體某個網路?

未完待續.....

微信 Alasica,歡迎討論學習。