UltraFast設計法實踐(1) -- Report_Failfast

目錄

平臺:Vivado16.4

專案:EADCH_2.3.0_Beta

根據《UltraFast Design Methodology Timing Closure Quick Reference Guide 》(UG1292)中的設計流程,第一個階段是"初始化設計流程檢查",該階段主要要讀懂三個操作生成的報告,這三個操作是:

- report_failfast

- report_timing_summary

- report_methodology

1. 初體驗report_failfast

有的平臺一開始並不能直接使用report_failfast命令,需要安裝Xilinx Tcl Store,安裝方法見:幹掉Vivado么蛾子(1)-- Xilinx Tcl Store。

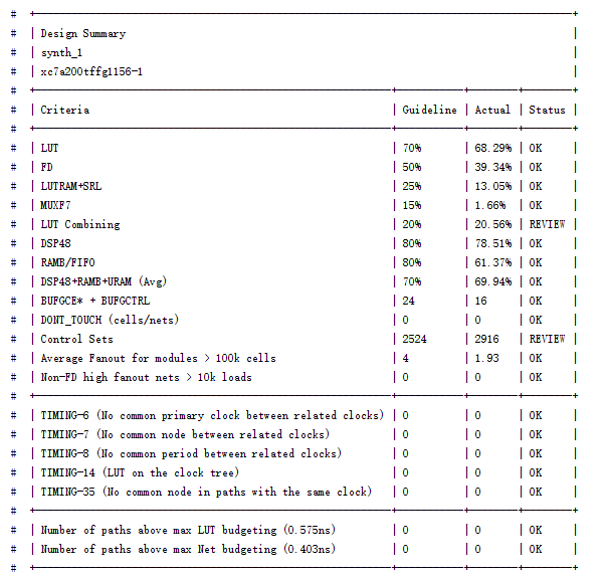

在工程綜合完成之後,需要開啟synthesized design(open synthesized design),使用Tcl命令:xilinx::designutils::report_failfast ,會在Tcl Console視窗得到一張圖表,如下圖所示:

這張表反映的是工程對資源的使用情況,包括參考(推薦)比例、實際比例和狀態。當各項實際使用率都符合參考的話,工程進行後續的過程才會相對可靠。我們尤其要關注狀態為“REVIEW”的項,它表示超過的參考推薦值,可能存在風險。

我的報告中狀態為“review”的有兩項:LUT Combining和Control Sets。

2.優化

2.1 LUT Combining

先看LUT Combining,查閱《UltraFast Design Methodology Guide for the Vivado Design Suite》(UG949)中關於它的含義。文中對其的描述如下:

LUT combining reduces logic utilization by combining LUT pairs with shared inputs into single dual-output LUTs that use both O5 and O6 outputs. However, LUT combining can potentially increase congestion because it tends to increase the input/output connectivity for the slices. If LUT combining is high in the congested area (> 40%), you can try using a synthesis strategy that eliminates LUT combining to help alleviate congestion. The Flow_AlternateRoutability synthesis strategy and directive instructs the synthesis tool to not generate any additional LUT combining.

大意是有的LUT pairs共用一些LUT的輸入,從而把O5和O6都用上,然後導致線路擁堵。

隨後看到這樣一個tip:

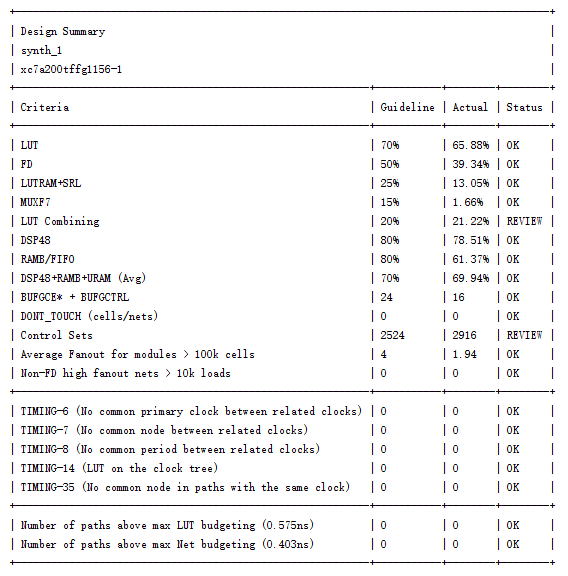

意思是讓我執行report_qor_suggestions,試試看,反饋了一些結果,建議opt_design -remap,完成之後再report_failfast,結果反而惡化,但LUT使用減少,如下圖

隨後,UG949中建議嘗試方法:

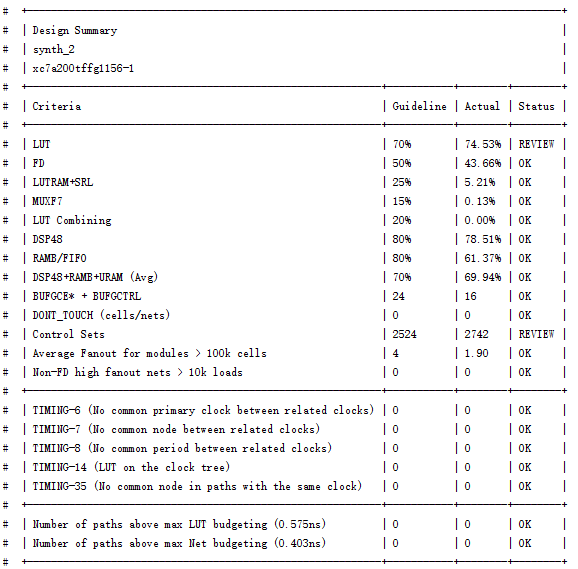

- synthesis setting -- strategy -- Flow_AlternateRoutability

說可以採取修改綜合策略的方式來優化,將策略改為Flow_AlternateRoutability可以減少LUT combining,從而可以優化擁堵的情況。改後綜合,report_failfast報告如下,LUT combining確實減少了,但LUT增加了,這是可以理解的,因為LUT Combining就是複用一些LUT的結果,現在不復用了,所以LUT的使用率增加了。

2.2 control_sets

先不管LUT,因為這個可以後期優化掉或者精簡程式碼實現。現在只剩control_sets了,查UG949中對control_sets的描述,如下:

Often not much consideration is given to control signals such as resets or clock enables. Many designers start HDL coding with "if reset" statements without deciding whether the reset is needed or not. While all registers support resets and clock enables, their use can significantly affect the end implementation in terms of performance, utilization, and power.

大致理解是跟一些使能或者復位訊號的不合理使用相關。使用report_control_sets -verbose 獲取control_sets的詳細情況,貌似是導致control_sets的一些設計,然後發現我的模組中大量的跟以下這樣一個訊號有關,而這個訊號大量的作為使能訊號。

assign w_divisor_valid = (mult_cnt == 6'd39); // control set 過高可能有這個原因這樣設計是有問題的,故改為時序設計:

[email protected](posedge clk or negedge rst_n) begin

if(rst_n == 1'b0) begin

w_divisor_valid <= 1'b0;

end

else if(mult_cnt == 6'd38) begin

w_divisor_valid <= 1'b1;

end

else begin

w_divisor_valid <= 1'b0;

end

end

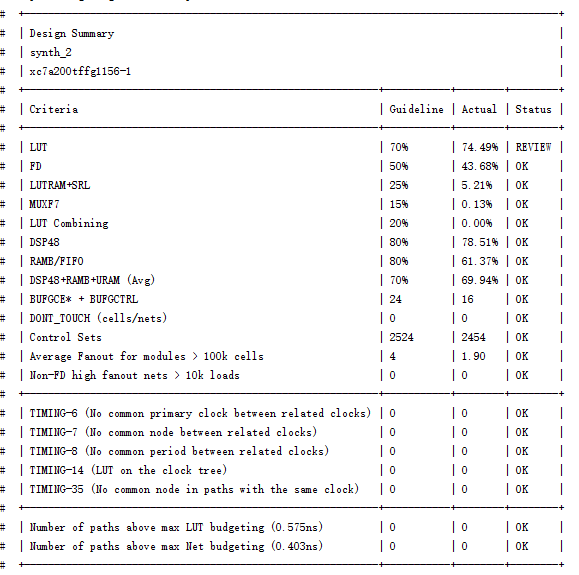

之後,再綜合--report_failfast,滿足要求了!!

3.總結

report_failfast生成的專案報告,檢視哪些項是REVIEW,然後針對每項內容是什麼含義,導致的可能原因,建議的優化方法等都可以從UG949中檢視,不斷反覆嘗試,直至可以接受的結果為止。

參考文獻:

- UG949

- UG1292

- 深度解析ug1292(1)