Vivado2017.4建立工程流程(使用Nexys4開發板)

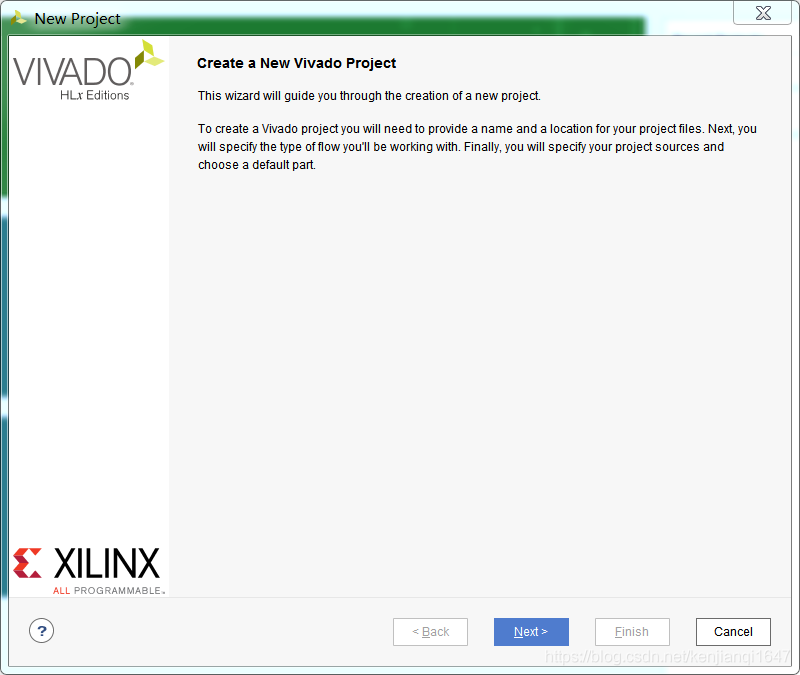

一、建立工程

1、Create Project

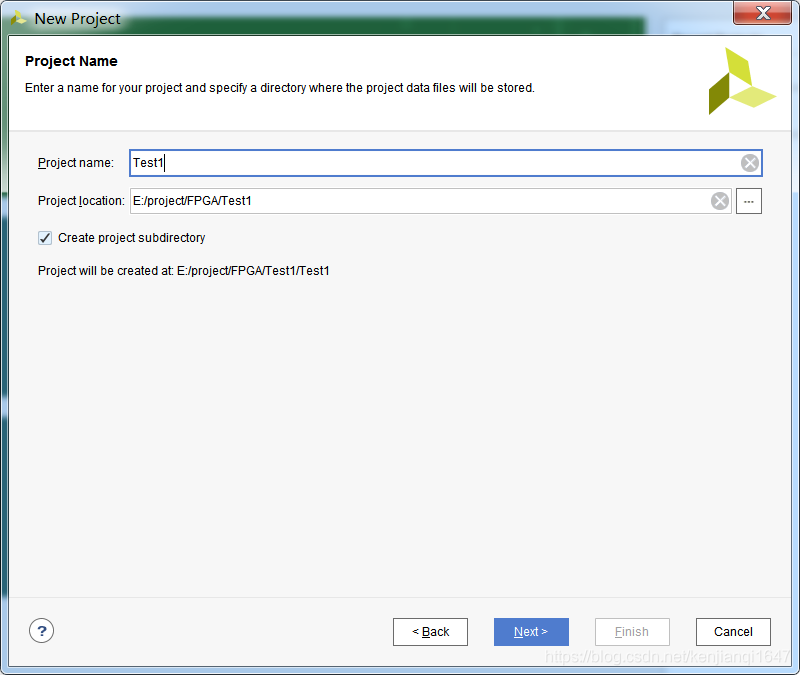

2、填寫工程名和路徑

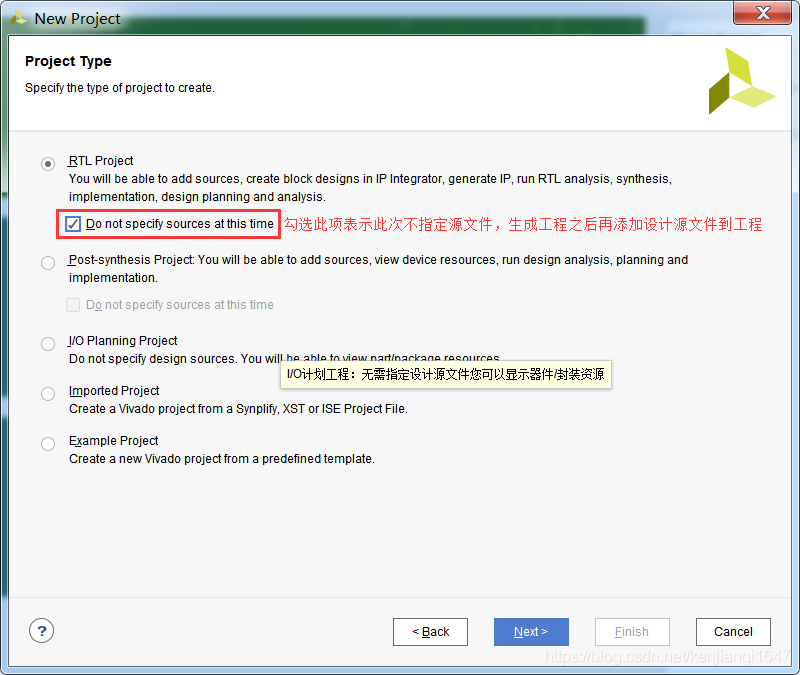

3、選擇建立RTL工程

4、選擇使用的晶片型號或開發板型號

5、完成

二、新增一個設計檔案

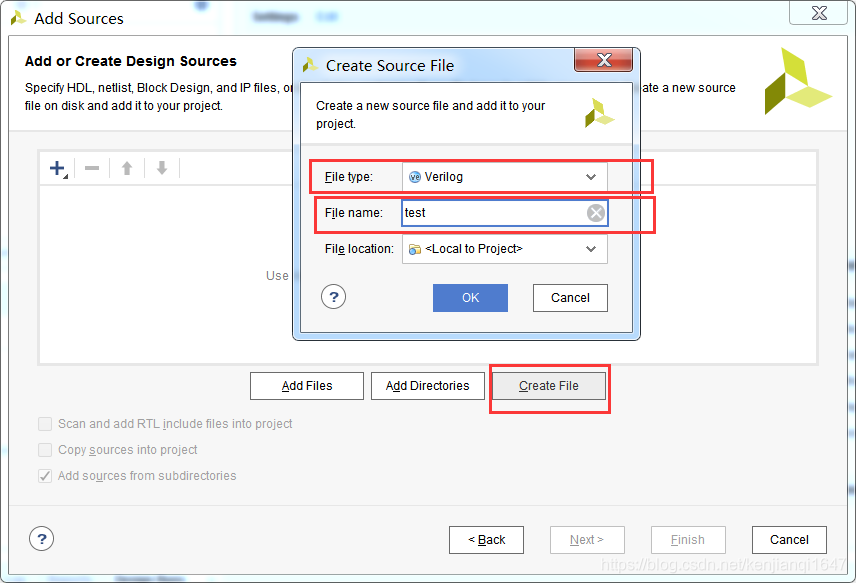

1、Add Source

2、新增設計檔案

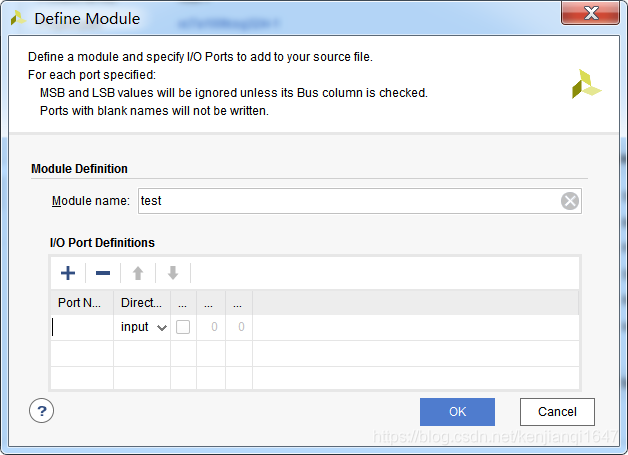

3、完成後,可以新增輸入、輸出引腳,也可以忽略後下一步新增

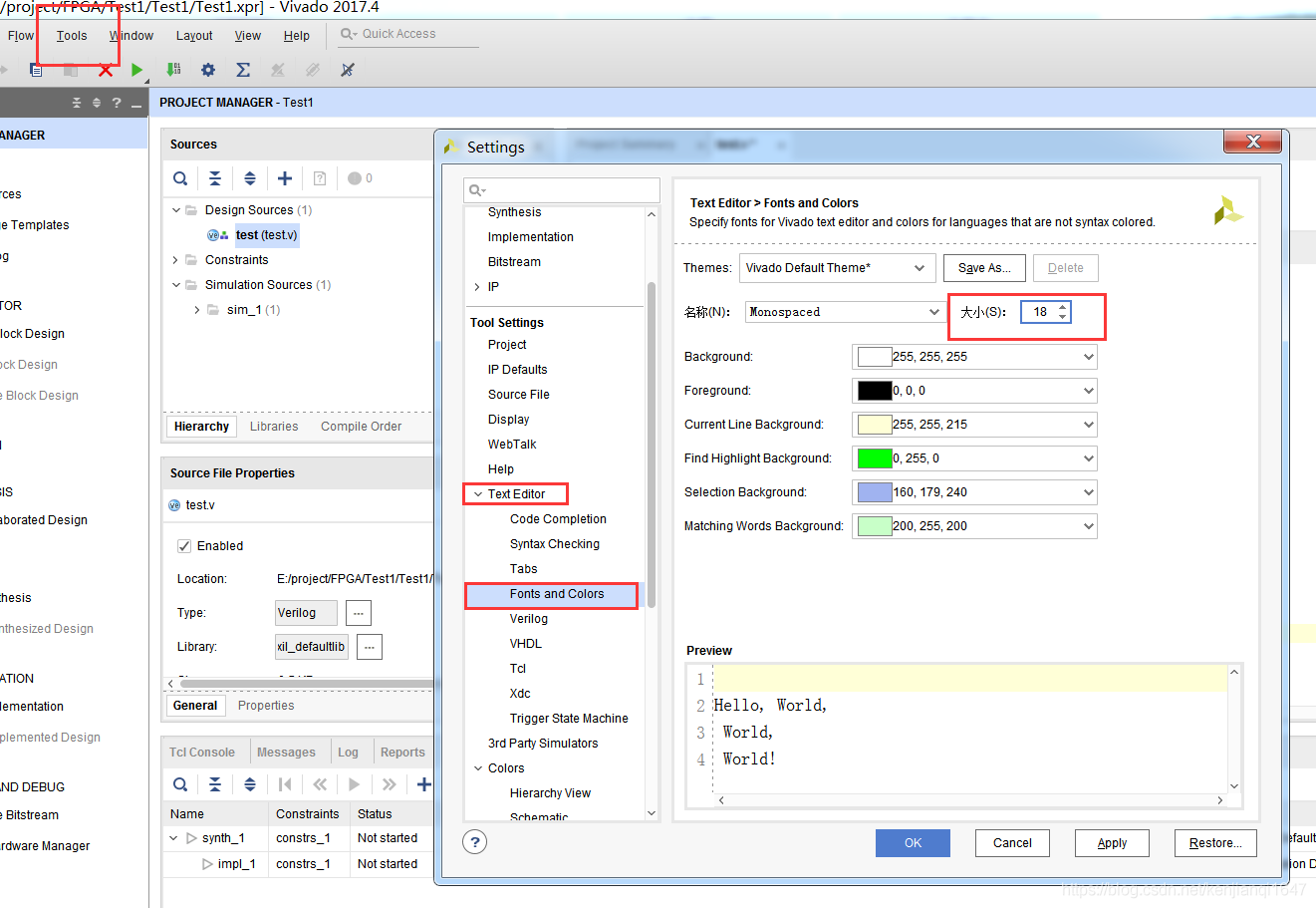

4、開啟.v檔案,編輯

預設的字型比較小,可以通過以下方法進行修改

編寫內容:做一個簡單的測試

module test( input a, input b, output [5:0] z ); assign z[0]=a&b; assign z[1]=~a&b; assign z[2]=a|b; assign z[3]=~(a|b); assign z[4]=a^b; assign z[5]=a~^b; endmodule

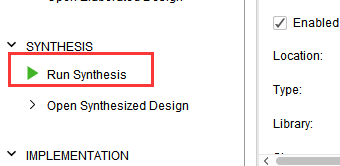

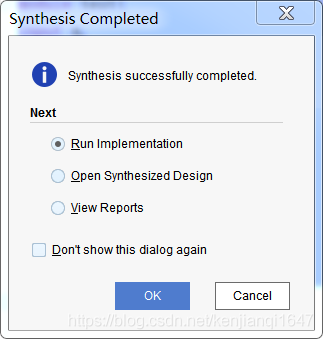

5、綜合

沒有錯誤之後,彈出

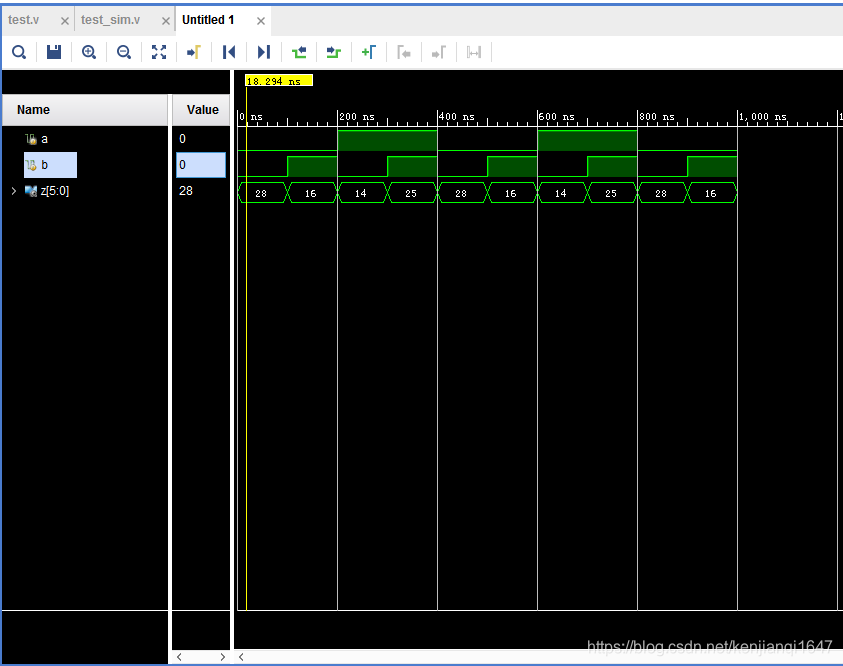

6、行為級模擬

(1)新增模擬檔案 Add Sources

(2)編寫模擬檔案,並儲存

注意test為被模擬的檔名

module test_sim( ); reg a; reg b; wire [5:0] z; test uut( .a(a), .b(b), .z(z) ); initial begin while(1) begin a=0; b=0; #100; a=0; b=1; #100; a=1; b=0; #100; a=1; b=1; #100; end end endmodule

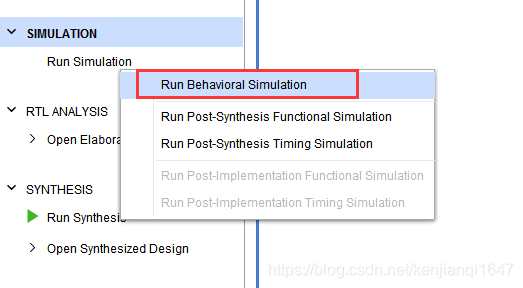

(3)啟動行為模擬

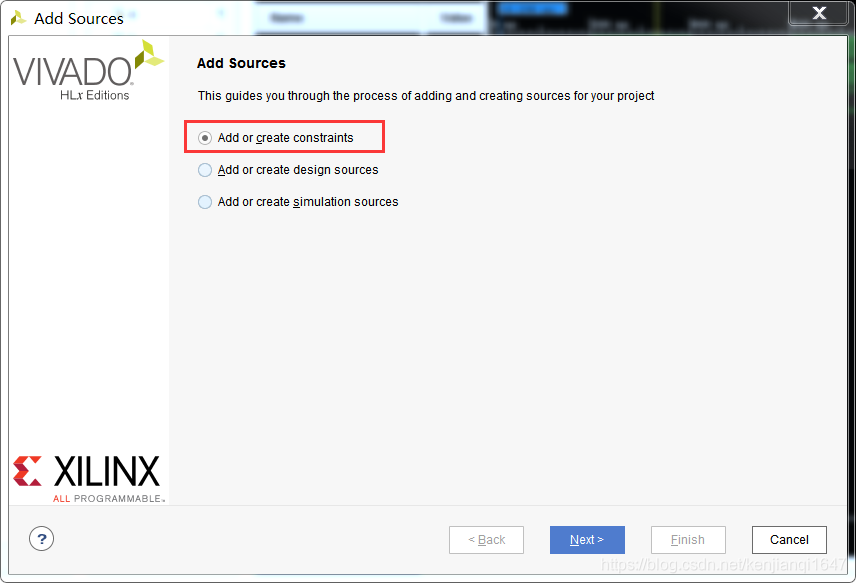

7、建立實現約束

約束的方法有兩種,一種通過GUI設定約束;另一種通過文字編輯的方法實現約束

GUI設定約束:

(1)Add Source

(2) 建立檔案

(3)啟動I/O Planning

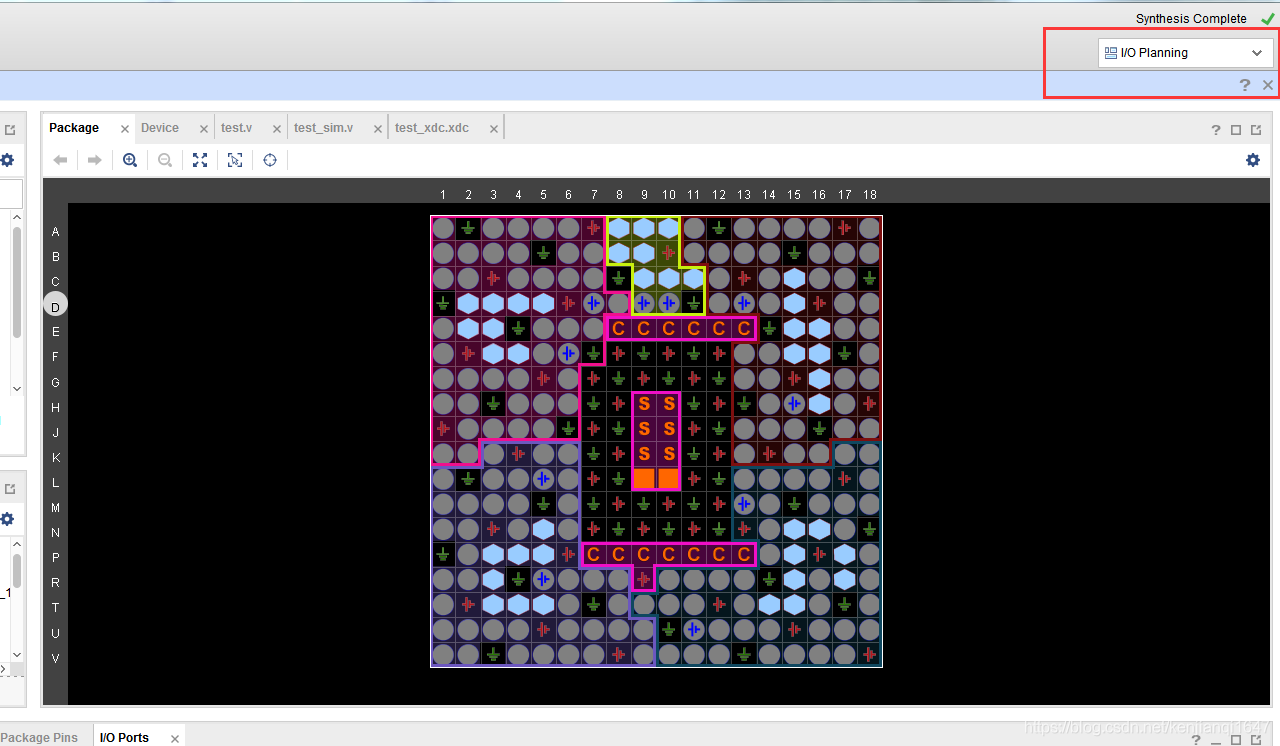

需要綜合後,點選Open Synthesized Design後,右上角選擇I/O Planning

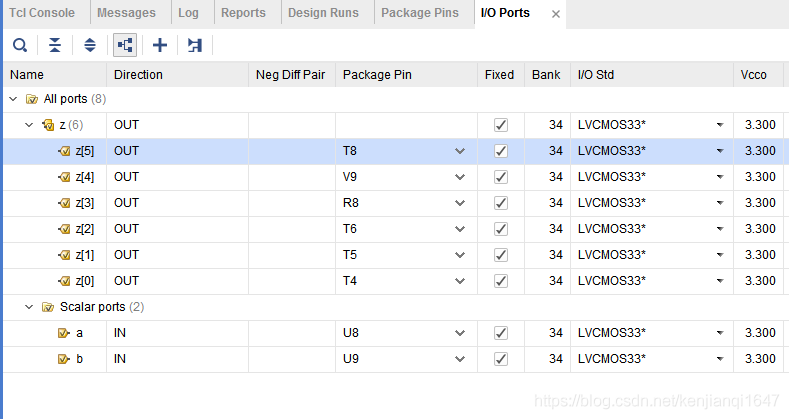

設定埠

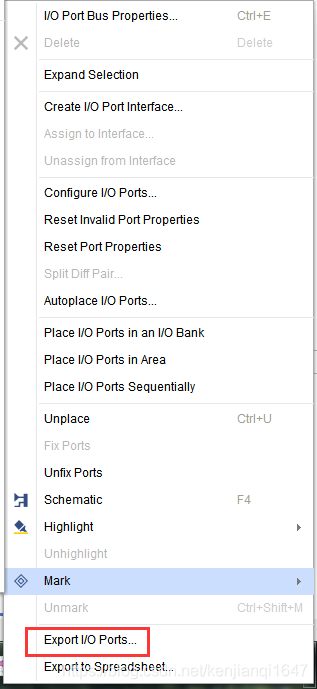

完成之後,右鍵單擊

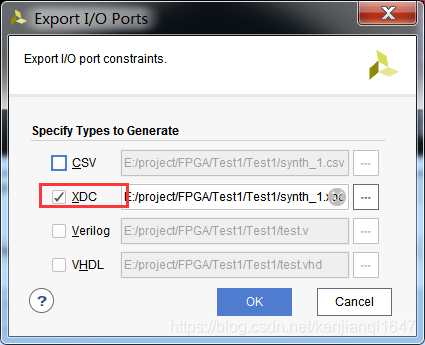

勾選XDC

注意XDC檔案右側的輸出路徑要設定成前面自己新建的XDC檔案的路徑。

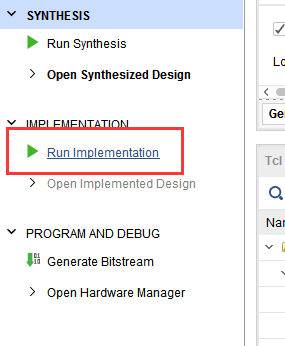

8、實現

選中.V檔案

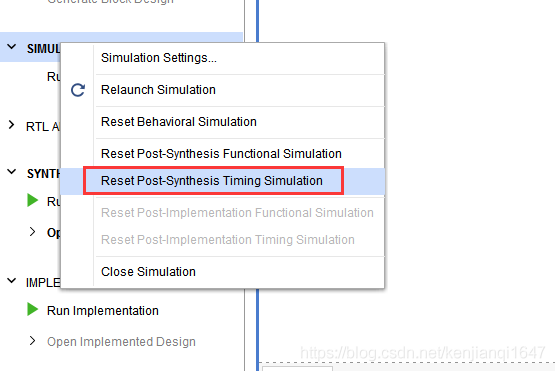

9、設計時序模擬

時序模擬和行為級模擬最大的不同點在於時序模擬帶有標準延遲格式,而行為級模擬不帶有時序資訊。毛刺、競爭冒險等時序問題都會表現在設計時序模擬中。

選擇.v檔案,找到“Simulation”,執行實現後時序模擬選項

檢視模擬效果

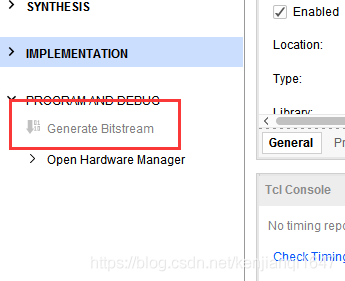

10、生成程式設計檔案

(1)選中.v檔案

(2)點選生成位元流檔案

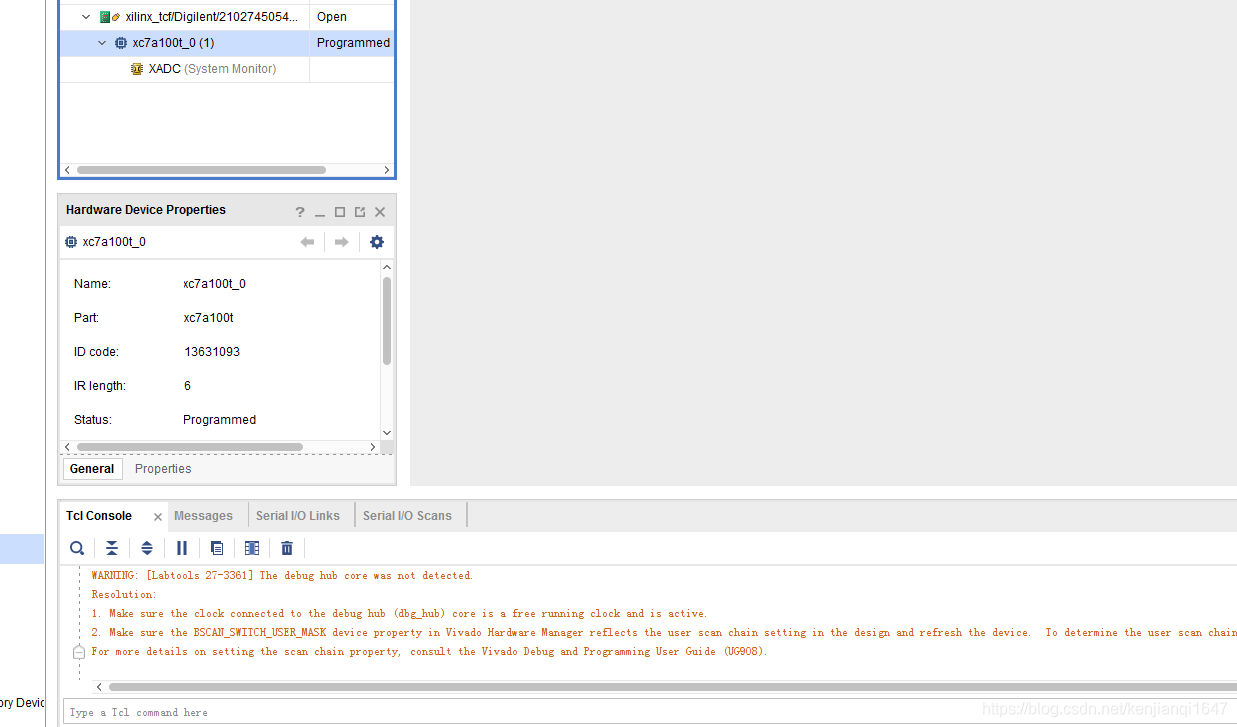

三、下載位元流檔案到FPGA

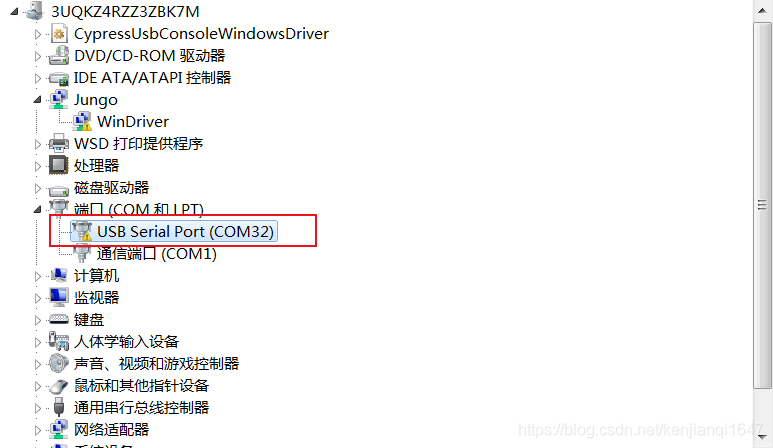

1、Nexys通過USB連線電腦

首次連線需要安裝驅動,才能識別Nexys4,可以使用驅動精靈或驅動人生軟體自動安裝

連線之後,我的是com32埠,雖然帶有警告標誌,不影響後面下載程式

2、連線開發板

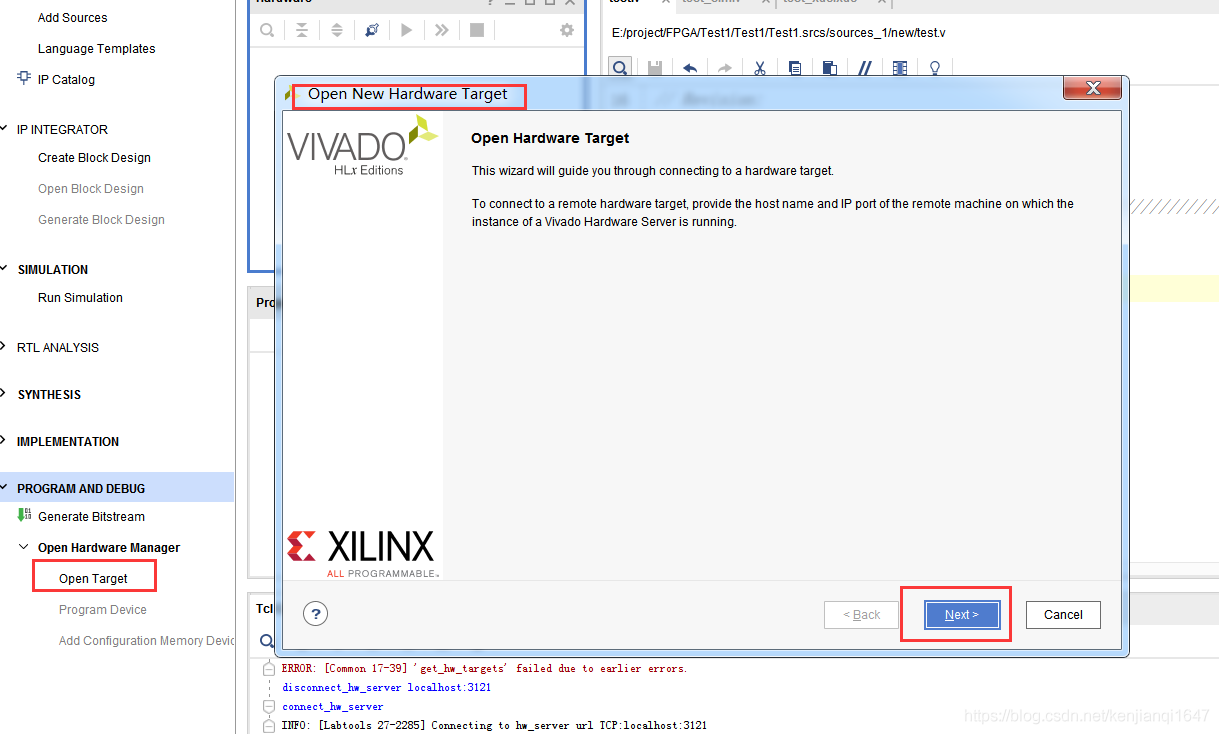

(1)PROGRAM AND DEBUG - Open Hardware Manager - open target - open New Target...

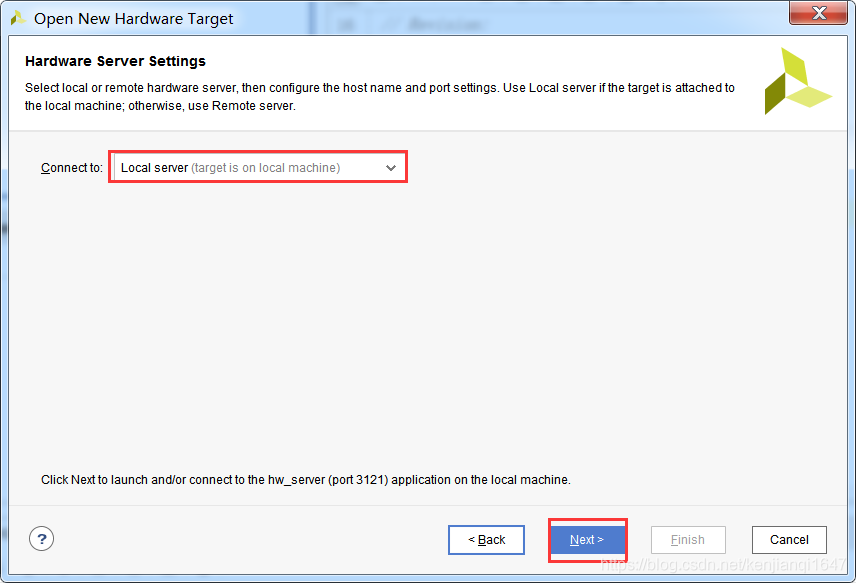

(2)選擇Local server

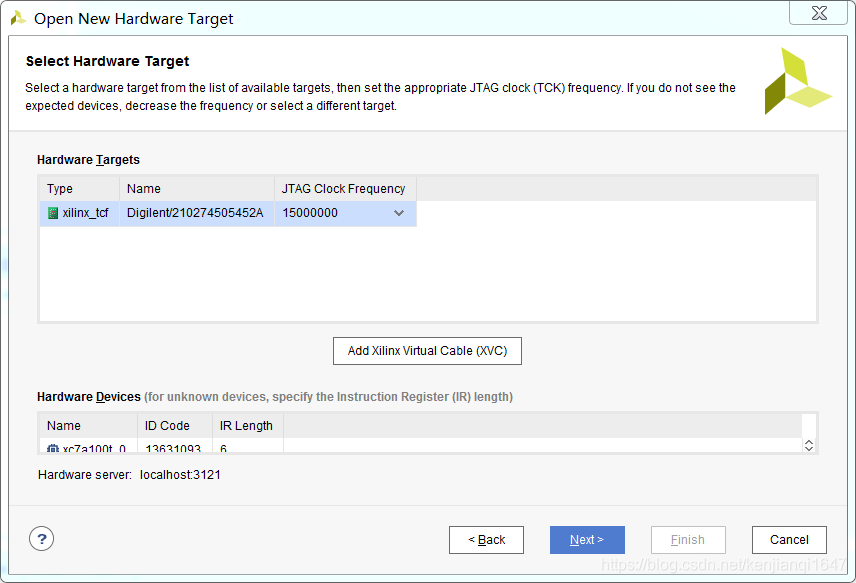

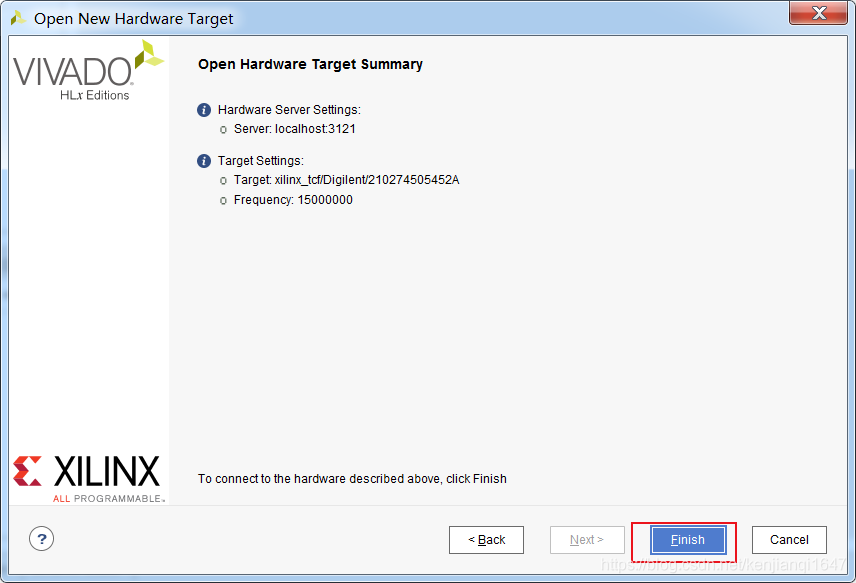

Next後找到裝置

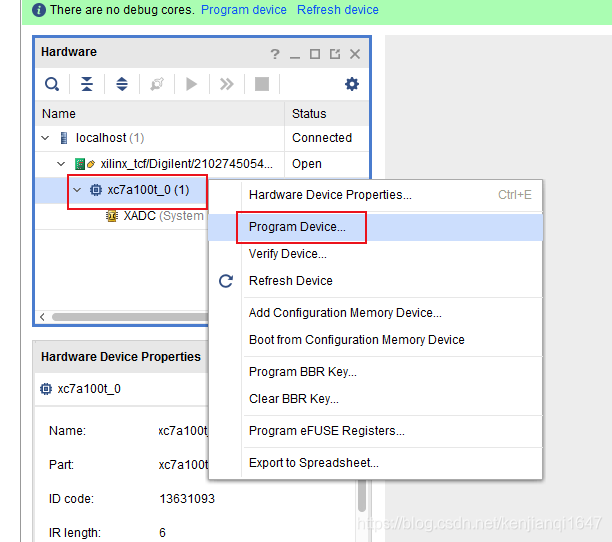

3、下載bit檔案

(1)選中找到的晶片,右鍵單擊,選擇Program Device...

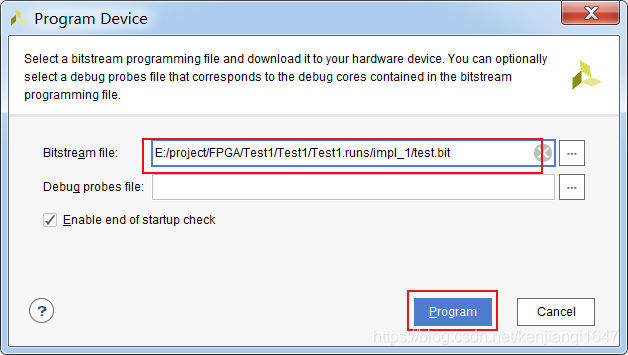

(2)新增bit檔案的路徑,點選Program

(3)下載成功,忽略警告