[EETOP]深入淺出電源完整性

轉發自 EETOP ,侵刪

[EETOP]深入淺出電源完整性

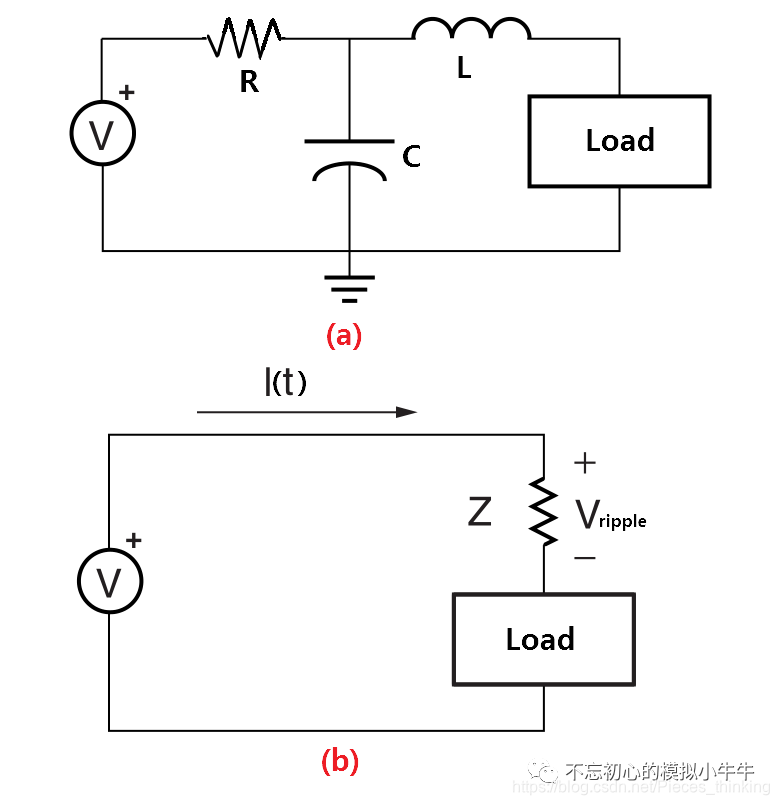

先看對於圖1(a)所示的電源供電系統,等效為理想電壓源,RLC元件,負載組成的電路。也可更簡單的等效為理想電壓源和內阻Z組成的供電迴路,當負載有動態電流需求時,在等效阻抗Z上會有一定的壓降存在,包含了不同頻率分量。

圖1

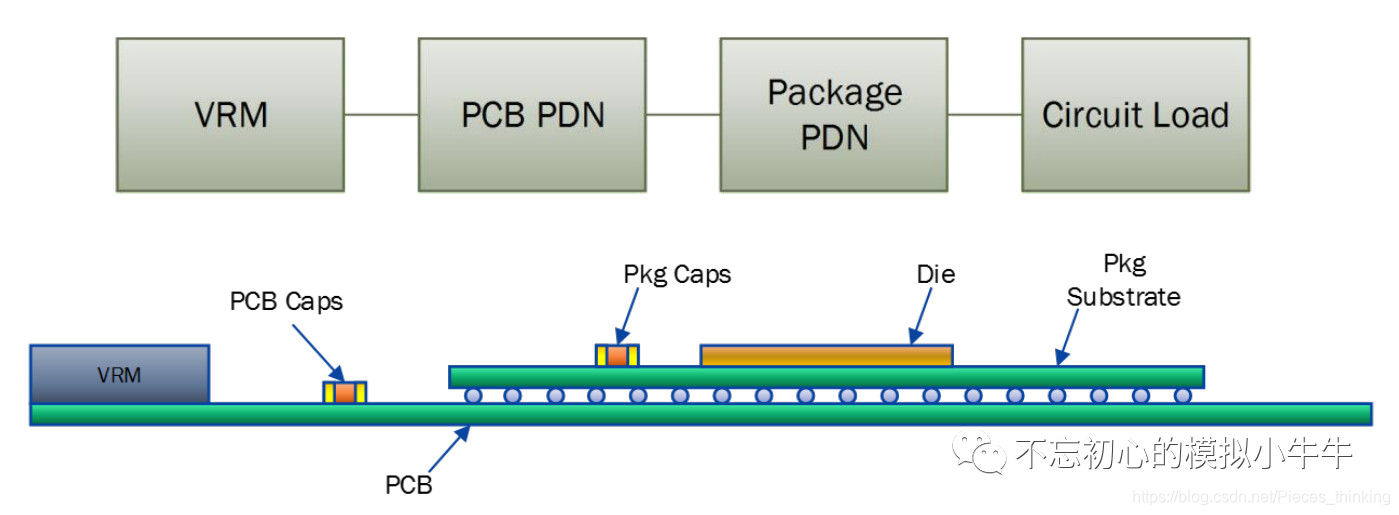

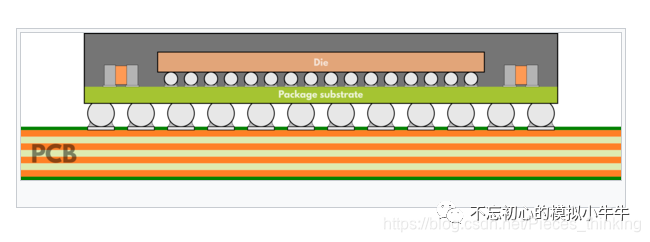

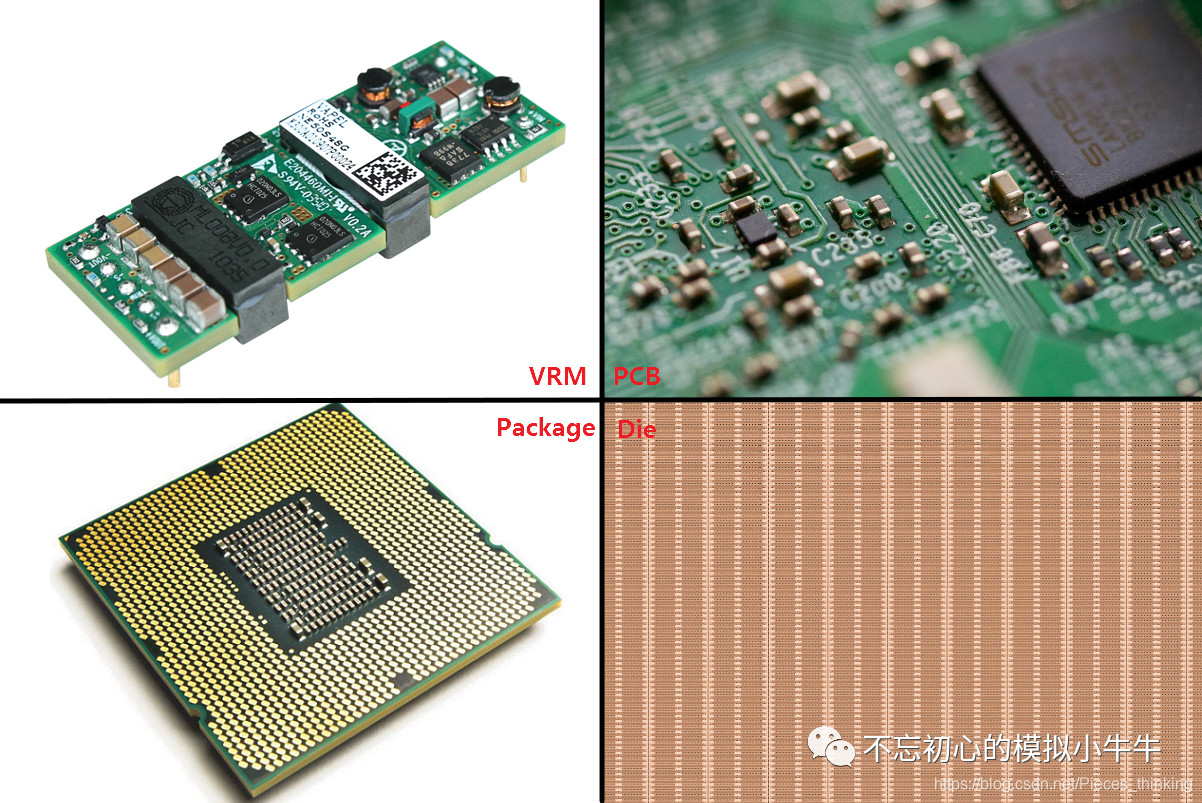

圖1的供電模型的典型板級應用實現形式,如圖2所示。板級電源模組(Voltage regulator module,VRM)通過印製電路板(Print Circuit Board,PCB)對焊接在其上的積體電路(Integrated Circuits,IC)提供電源。這裡需要說明的是電流回路主要怎麼樣的,首先是VRM的電源輸出經過過孔到達PCB的電源平面,通過過孔到達封裝的管腳,再通過封裝到達晶片的電源Pad(封裝形式決定了封裝內部的電源路徑形式),通過晶片內部的電源網路到達器件埠,再通過幾乎相似的地迴路回到VRM地,從而形成完整的供電迴路。

圖2

外部電源要經過供電路徑上的不同元件才能到晶片內部,電晶體級埠得到的電壓總是多多少少總會存在偏差。特別是對於高速電路和其他一些電源要求嚴苛的晶片,如紋波小於±5%或±3%的規格。電源的設計就面臨著越來越大的挑戰。

特別是Die內動態電源比較難以準確測量。實際晶片內部的電源環境可能會比較惡劣。舉個不恰當的例子,就像上邊要發財政補貼每人100塊錢,經過幾級的截留,實際到手可能只剩80塊了。中間經過的多了,保不準就有損耗。

電源完整性(Power Integrity,PI)通俗理解就是給負載準確完整地供電。主要是通過評估和優化設計整個供電網路的阻抗特性,從而滿足晶片內的供電需求,保證晶片的功能和效能。電源完整性其實是個系統工程。

圖2中主要劃分整個電源系統為四個部分,VRM,PCB Board,Package,Die。實際上主要從Board level,Package level和Chip level分別著重處理。

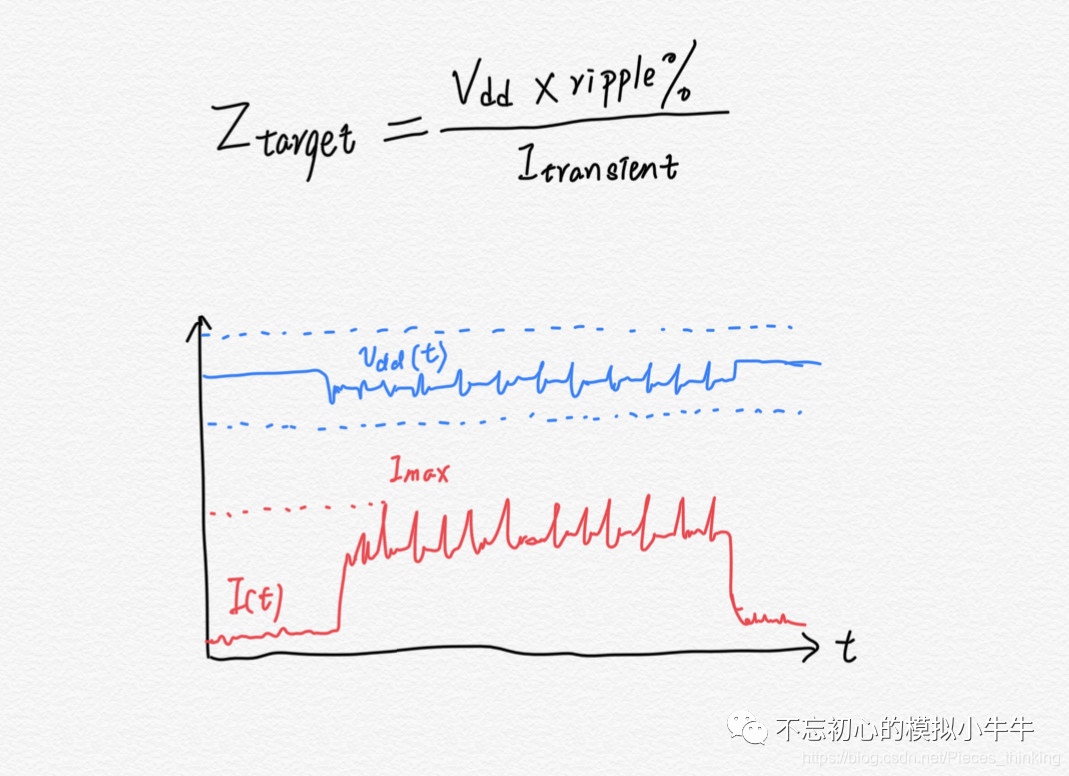

其實我們通俗對電源的要求主要體現在兩方面:IR drop小、紋波小。也就是從DC和AC角度的要求。其實從頻域上可以總結為在一定頻段內需要保持較低的阻抗。這裡就必須提到目前在電源完整性設計方便最基礎最常用的目標阻抗(Target Impedance)法。

圖3

在目標阻抗的計算中,有經驗參考,負載瞬態電流Itransient可以選擇為最大瞬態電流的一半。實際選擇中需要綜合應用環境,合理調整圖3公式中的瞬態電流。

圖4

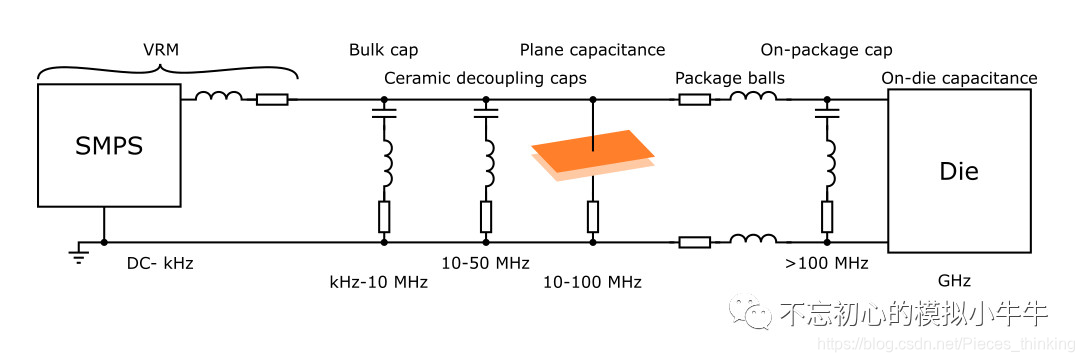

實際上圖2所示電源路徑上的元件,可等效為圖4所示的包含了電阻、電感和電容組成的串並聯諧振的等效PDN網路模型。並且各部分能夠負責“保持低阻抗”的頻率範圍也不相同。

這是因為很難具體知道某一時刻的負載電流的頻率成分,所以無法做到"精準施策",採用“一刀切”的方式也未嘗不是一種偷懶的解決方式。即在比較寬頻率範圍內,使從Die側看向PDN網路阻抗小於預定值Ztarget。

圖5

圖5為焊接在PCB板上的一個FCBGA封裝的例子。在封裝中也使用了多層的PCB板,稱之為封裝基板。在基板上也存在去耦電容。

在整個PDN網路中,電阻和電感分佈位置主要有,PCB走線和過空,電容器ESL和ESR,封裝的鍵合線(bonding wire) ,凸點(bump)和錫珠(solder ball)等。

電容分佈主要包括:分離電容器,電源平面間寄生電容,Die內分佈電容等。如圖6所示。

圖6

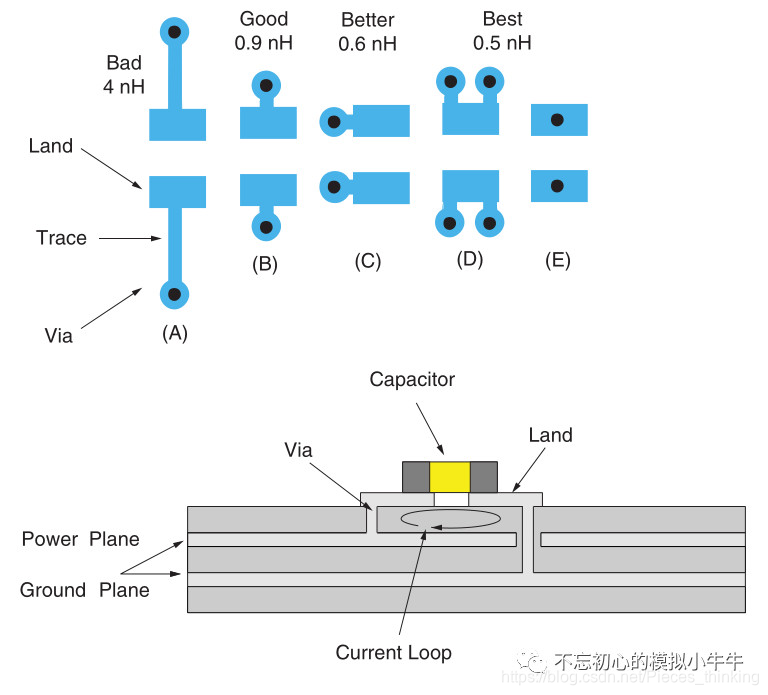

圖7是一個典型的PCB或基板上去耦電容到電源地平面的連線剖面圖。圖中的電流回路,包含了電源地平面,過空,走線和電容器等電感和電阻,電感和電阻的阻抗頻率特性,決定了需要儘可能減小其在供電通路上的影響。,比如通過改進優化電容的焊盤layout設計,電源和地平面的介質厚度等,將安裝電感和擴散電感等控制在比較小的範圍內。

圖7

可是大多數時候優化電阻和電感的成本或代價會比較大。而相對來說,電容的操作空間就比較大了。電容具有和電感具有相反的阻抗頻率特性。因此通過合理選擇電容型別、型號、容值和分佈位置,結合諧振電路的特點可實現比較優化的電源系統。所以才能看到圖6中在不同系統層級上,會有不同的電容設計。

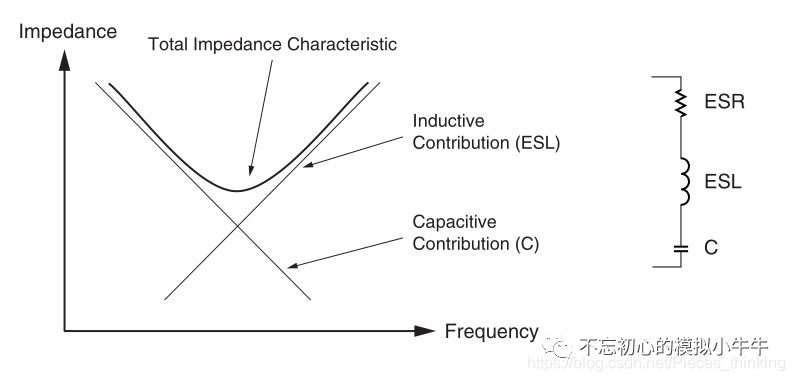

對於實際電容的模型,如圖8。除了代表電容的符號C外,還有等效串聯電阻(ESR)和等效串聯電感(ESL),形成了串聯諧振電路。諧振頻率為fres=1/(2pisqrt(L*C)),其中L和C分別是電容器的ESL值和電容值。在諧振頻率處阻抗最小為ESR電阻值,低於頻率fres呈現容性,高與頻率fres呈感性。

圖8

需要注意的是,儘管ESR電阻不影響諧振頻率,但卻影響品質因子Q,也就是諧振頻率處的頻寬。而在電容的去耦應用中,通常希望電容能夠在一個較寬的頻率範圍內具有較低的阻抗,也就是品質因子Q不能太大。因此在電容選型時,ESR電阻是一個需要著重考慮的因素。

注意像圖7的電容典型安裝方式,實際電容的諧振頻率還需要考慮安裝電感,電阻等因素。會不同程度的小於電容的Datasheet上的標稱值。

除了板級和封裝上,Die內也要儘可能多的分佈去耦電容,主要作用是負責降低高頻阻抗。Die內電容多數是有源器件貢獻的比如,專門做decap電容,器件工作狀態相關的器件電容。另一部分可以看做是寄生電容,比如電源和地的Mesh網狀結構的寄生,MIM、MOM等。

通常Die內電容會和bump、鍵合線、基板走線的寄生電感形成LC諧振。諧振頻率位於中頻位置,也就是在中頻表現為比較大的阻抗,因此也稱之為封裝壁壘(Package barrier),也是為什麼需要在中頻通過基板或PCB來降低中頻阻抗的原因。

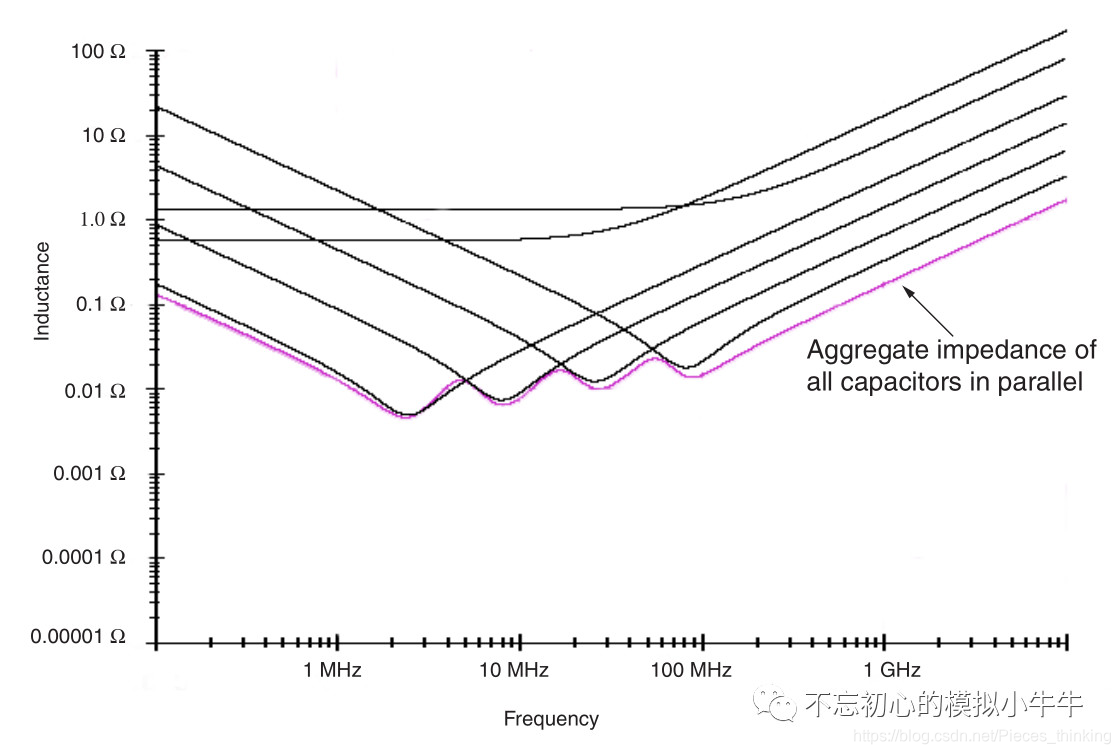

圖9為一個通過不同補償電容的組合將PDN的阻抗在比較寬的頻率範圍內優化的阻抗圖。

圖9

想個問題,為什麼越來越多的先進封裝上,會在空間那麼小的封裝基板上掛很多電容,直接都放在PCB上不就行了嗎? 這裡就涉及到一個去耦半徑的概念。

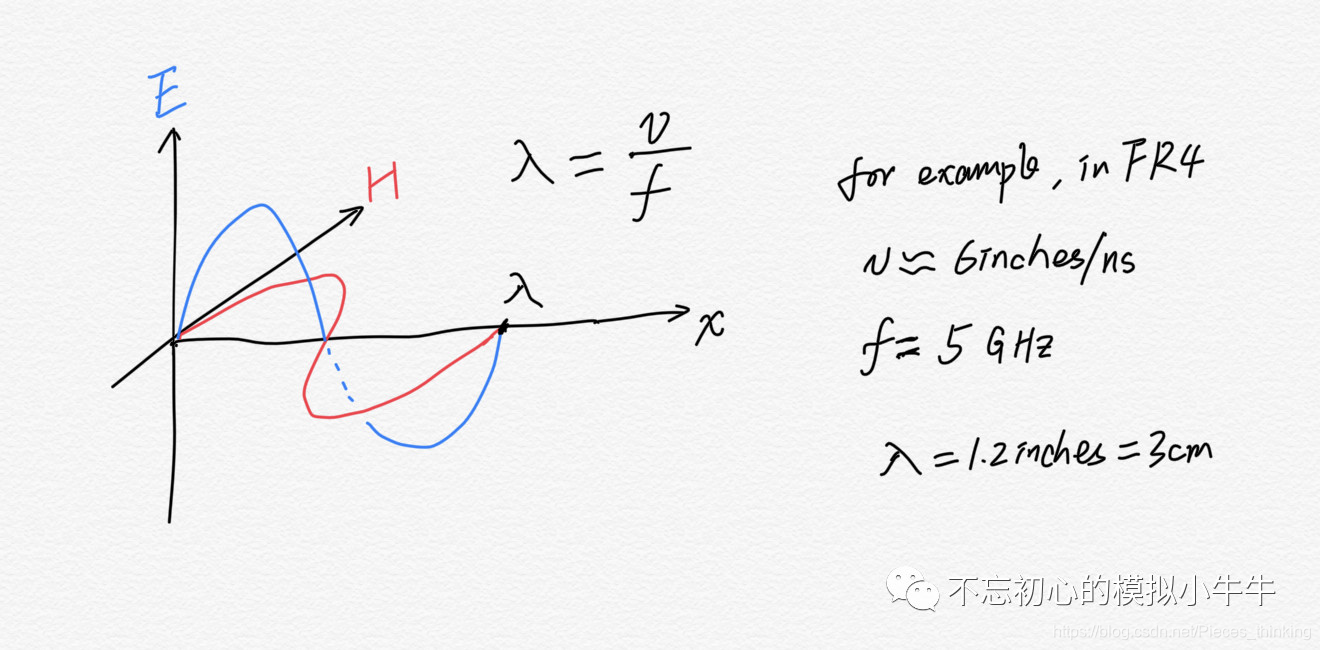

還記得傳輸線中我們講到電訊號在介質中以接近光速的電磁波傳輸,實際傳播速度和主要和PCB材質的相對介電常數有關,如圖10,電磁波波長λ和速度頻率關係。

晶片內部瞬態電流造成的電壓擾動(disturbance)到去耦電容感知到該擾動並響應需要一定的時間。該時間等於訊號的一個“來回(round trip)”時間。當電容距離太遠,超過波長的1/4λ時,電容的去耦效果就消失了。實際應用中電容安裝距離應該越近越好,比如1/40的波長等。

圖10

例如對於FR4材質,5Ghz的頻率對應的波長為3cm。這時候就需要高頻去耦電容距離Die的距離更近一些,特別是對於大尺寸(CPU,GPU,FPGA等)的封裝,基板上的去耦電容是很有必要的。

而對於目標阻抗的模擬驗證,有不同的EDA設計工具可以完成。如Cadence的Sigrity,Keysight的ADS以及其他EDA工具等。而實際板級的測量,在頻域可通過網路分析儀(Network Analyzer)進行阻抗分析。在時域可通過示波器進行板級和封裝上的電源測量。比如是德的高頻寬電源探頭可以協助驗證電源完整性相關的問題,如圖11所示。

圖11

另外在PCB、基板和Die都要考慮電源相關的測試問題。只有比較準確的測試,才能協助分析定位問題。比如基板考慮對一些關鍵電源的測試點,Die內電源和地壓降可通過模擬測試通道進行測試,如果有可能測試到高頻分量更好。

最後,推薦一篇如圖12文章,是德聯合PICOTEST提供了針對Xilinx 32G速率SerDes的電源供電網路的分析和優化思路,看後一定能夠有所收穫。

圖12

最後需要說明的是,電源的問題說小可小,說大可大,和晶片工作速度密切相關。作為晶片驗證的重要條件之一(PVT),其實很多時候對效能的影響很難做到準確的評估。電源完整性對晶片效能的影響的認識不足,可能會誤導設計和測試人員對於測試問題的判斷,所以要未雨綢繆,多瞭解一點點,總沒錯的。

推薦閱讀: