xilinx7系列FPGASelectIO篇(2)_IO邏輯資源簡介

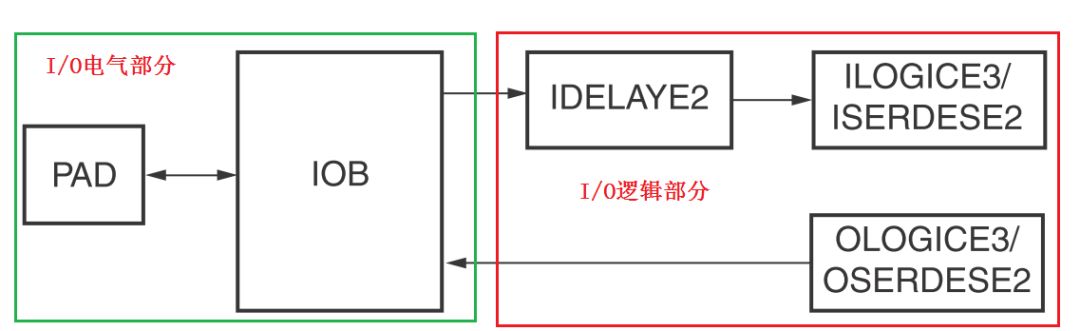

上篇咱們簡單的說了I/O的電氣特性,本篇咱們接著介紹I/O邏輯資源,先貼上兩張圖。圖1為HPBANK的I/O模組,圖2為HRBANK的I/O模組,兩者區別在於後者無ODELAYE模組。

圖1:HP BANK I/O模組

圖2:HR BANK I/O模組

I/O邏輯資源主要包含5部分:

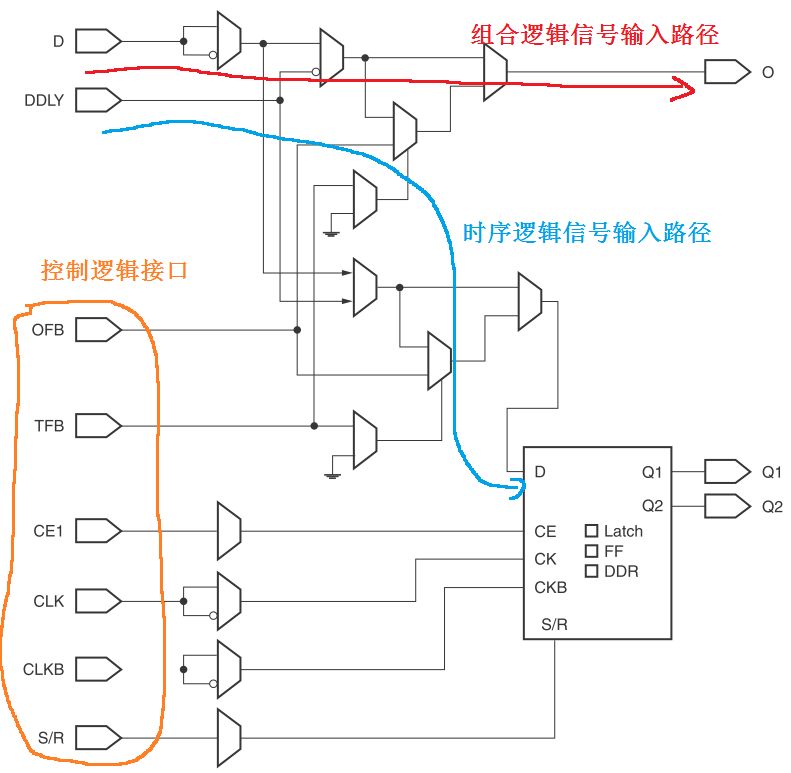

1, ILOGIC

ILOGIC即輸入訊號處理邏輯,緊挨著IOB,外界的輸入訊號最先經過的就是ILOGIC。ILOGIC是由許多的資料選擇器和一個IDDR(input

Double data rate)觸發器構成。該觸發器既可以雙沿捕獲輸入資料也可以拆分成普通單沿觸發器。在HP BANK中,ILOGIC被稱為ILOGICE2,在HR BANK中,ILOGIC被稱為ILOGICE3。圖3給出了ILOGICE3的示意圖:

圖3:ILOGICE3示意圖

2, IDELAY

IDELAY被稱為訊號延遲模組,它的作用就是把訊號延遲一段時間。對於一些需要對齊的輸入訊號來說,這至關重要。在7系列FPGA中,它被稱為IDELAYE2。IDELAYE2可以將訊號延遲0~31節,在這區間任意可調,並且每節的延遲精度約為78ps(1/(32×2×FREF),FREF為IDELAYCTRL的參考時鐘)。圖4為IDELAYE2例化框圖。

圖4:IDELAYE2例化框圖

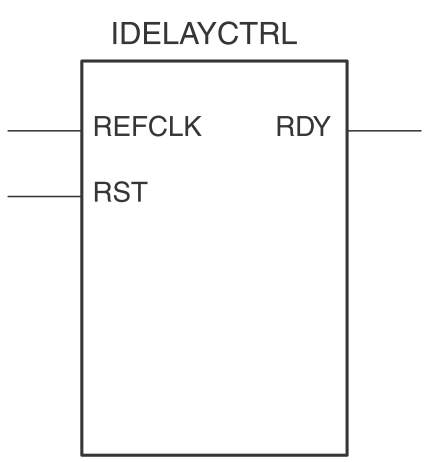

3, IDELAYCTRL

IDELAYCTRL其實是個輔助模組,這麼說吧,只要咱們使用了IDELAY或者ODELAY,IDELAYCTRL必須被使用,要不然就無法正常工作。因為IDELAY或者ODELAY的延遲精度是由IDELAYCTRL的輸入時鐘決定的,一般為200MHz。下圖5為IDELAYCTRL例化框圖。

圖5:IDELAYCTRL例化框圖

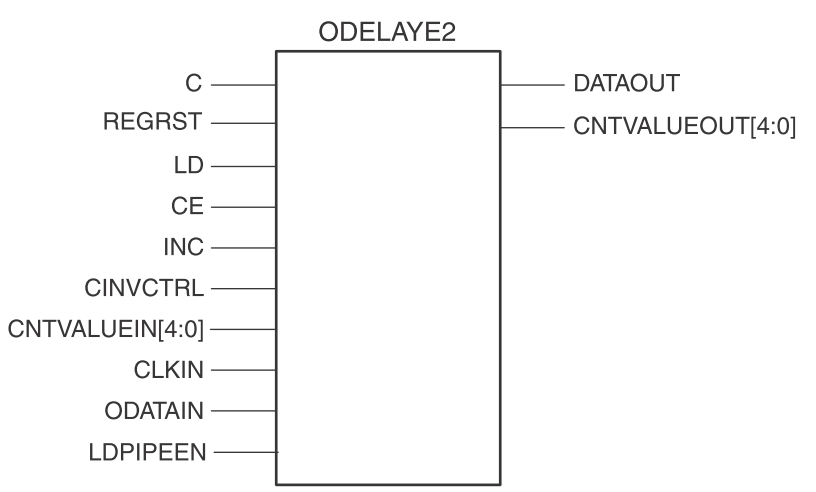

4, ODELAY

ODELAY和IDEALY的使用方式差不多,只不過ODELAY是用作輸出訊號的延遲。另外,HR BANK內沒有ODELAY,HP BANK才有,被稱為ODELAYE2。使用ODELAYE2時同樣需要例化IDELAYCTRL。圖6為ODELAYE2例化框圖:

圖6:ODELAYE2例化框圖

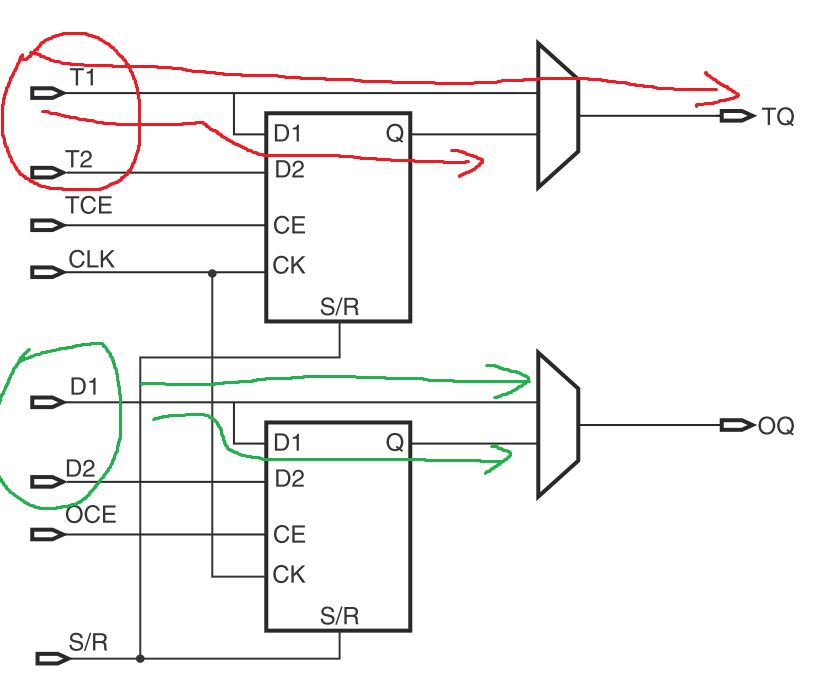

5, OLOGIC

LOGIC包括2個部分:一個用於配置輸出路徑。另外一個用於配置三態控制路徑。輸出路徑和三態控制路徑都可以獨立配置成沿觸發器、ODDR以及組合邏輯輸出。

圖7:OLOGIC示意圖

總得來說,I/O邏輯資源就是用來獲取或者輸出訊號。對面一般的低速訊號而言,I/O邏輯資源體現不出優勢,用不用都不影響最終結果,但是對於高速訊號而言,就必須使用I/O邏輯資源了,不能夠正確使用它,整個FPGA邏輯程式碼完全無用。但是FPGA不就是用來處理高速訊號的麼?所以I/O這一塊應該是整個FPGA的精華之處,當然也是使用最難的部分了。。。。。。

為了方便咱們使用I/O邏輯資源,xilinx公司專門將本篇介紹的幾種模組集中起來,構成了功能強大的源語ISERDESE2和OSERDESE2,咱們只需要呼叫源語,正確使用源語就能夠完成高階的I/O邏輯設計了,下篇咱們就聊聊高階邏輯資源ISERDESE2和OSERDESE2吧!