xilinx 7系列FPGA之SelectIO(3)_高階IO邏輯資源簡介

上一篇咱們介紹了IO邏輯資源,本篇咱們來聊一聊高階的IO邏輯資源,即ISERDESE2模組和OSERDESE2模組。

所謂ISERDESE2模組,即Input serial-to-parallel converters。該模組的作用就是實現高速源同步輸入資料的串並轉換。

所謂OSERDESE2模組,即output parallel-to-serial converters。該模組的作用就是實現高速源同步輸出資料的並串轉換。

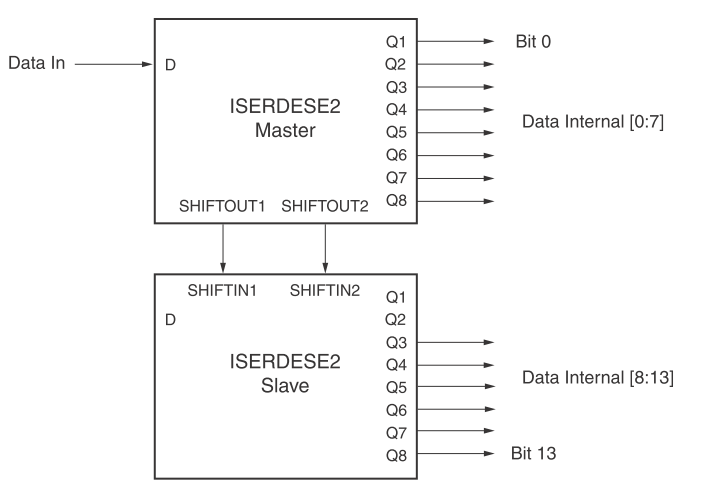

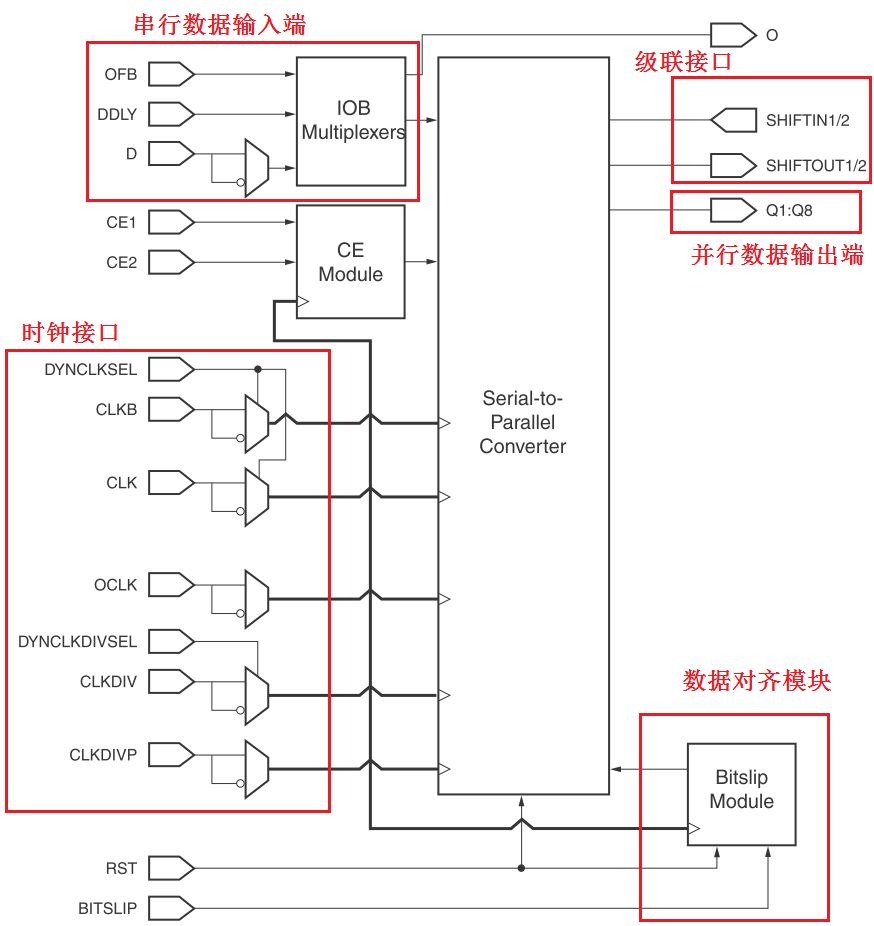

先說ISERDESE2。該模組接收外部輸入FPGA的高速源同步序列訊號,在FPGA內部將其轉換為使用者需要的並行資料訊號。如圖1所示為ISERDESE2的功能框圖,咱們可以將按照功能分成5個部分:

圖1:ISERDESE2的功能框圖

1, 外部序列資料輸入端

該部分接收外部輸入的高速源同步資料,資料可以為SDR或者DDR。在SDR模式時,資料轉換的位寬可以為2、3、4、5、6、7、8bit。在DDR模式時,資料轉換位寬為4、6、8bit,當然如果是2個ISERDESE2級聯使用,DDR模式可以支援10、14bit。

2, 時鐘介面

該部分提供ISERDESE2工作的高速源同步序列時鐘、並行資料獲取時鐘以及控制時鐘。如圖2所示為源同步時鐘接入ISERDESE2的用法。

圖2:時鐘接法

3, 並行資料輸出端

該介面就不用多說了,就是最終咱們需要的並行資料。SDR模式下為2、3、4、5、6、7、8bit,DDR模式下為4、6、8、10、14bit。

4, 級聯介面

該介面是實現DDR模式下10bit、14bit位寬的關鍵介面,通過該介面與另外一個ISERDESE2級聯,兩者共同完成10bit、14bit資料的串並轉換。如圖3即為2個ISERDESE2的級聯使用。

圖3:ISERDESE2級聯

5, 資料對齊模組

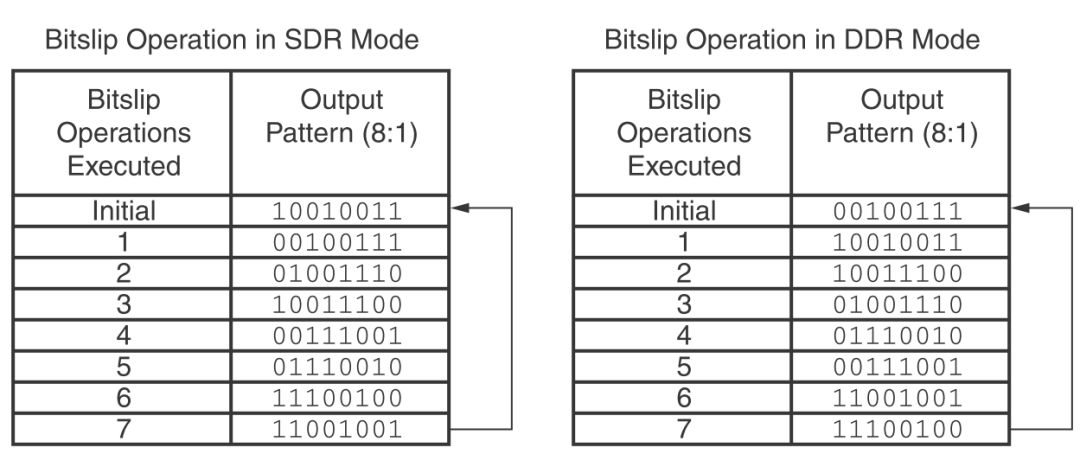

該模組又稱作Bitslip模組,用來實現並行資料的邊界對齊。比如咱們外界序列輸入的8bit的資料,經過串並轉換後,能獲取8bit的並行資料,但這並行資料可能存在前後8bit資料之間的錯位,這是串並轉換無法識別的,因此Bitslip就專門用來找到使用者需要的並行資料邊界。

圖4給出了Bitslip是如何確定並行資料的邊界:對於SDR模式,Bitslip使能1次,則資料會左移1次,對於8bit並行資料,移動8次完成一個迴圈,可以這樣無止境的迴圈,直到找到使用者定義的並行資料。對於DDR模式,Bitslip工作方式不同,Bitslip使能1次,資料會右移1次或者左移3次,兩者交替進行,同樣移動8次完成一個迴圈。

圖4:Bitslip工作原理

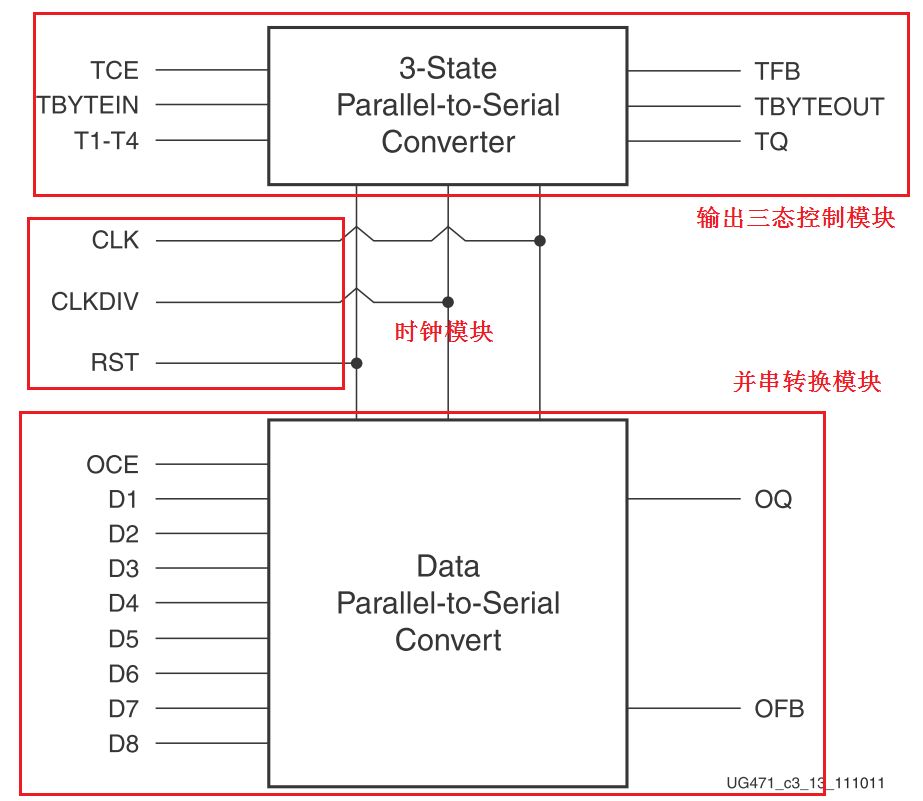

咱們再說OSERDESE2模組。該模組和ISERDESE2模組不同,少了Bitslip模組,多了一個三態控制模組,可以實現三態控制並串轉換功能,資料的位寬和咱們介紹的ISERDESE2規則一樣。如圖5所示為其功能框圖:

圖5:OSERDESE2功能模組

如圖6所示為OSERDESE2的級聯設計,實現10、14bit的並串轉換功能:

圖6:OSERDESE2級聯

OSERDESE2除了多出了一個三態控制模組,其它和ISERDESE2基本一樣,只是資料流反相操作,因此咱們這裡主要看一下三態控制模組,該模組主要功能就是實現序列資料流的三態輸出,圖7給出了三態控制的詳細時序結構,從圖上我們可以看到,三態控制下,序列資料流有選擇性的輸出E、F、H,實現了輸出序列資料的三態控制。

圖7:三態控制序列輸出

本篇咱們很簡要的介紹完了ISERDESE2和OSERDESE2,大家瞭解了嗎?當然如果要實際使用的話,咱們還得看看具體資料手冊啦!在上篇咱們就說過了,IO部分是FPGA內最複雜的部分,也是設計起來最難的部分,要熟悉使用它,咱們還得下功夫鑽研!