FPGA專案——基於AXI4匯流排的RAM讀寫

阿新 • • 發佈:2018-12-28

基於xilinx IP 核 Block Memory Gnerator V 8.3

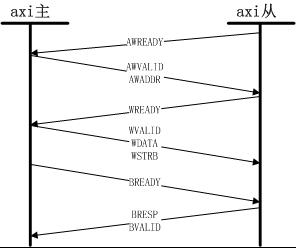

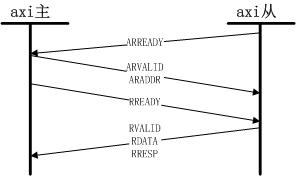

AXI匯流排讀寫協議簡介

在vivado上模擬實現

IP核配置

一共兩種選擇,我們選擇AXI4

testbench

程式碼如下:

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2018/12/17 15:06:05 // Design Name: // Module Name: sim // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module sim; wire rsta_busy; wire rstb_busy; reg s_aclk; reg s_aresetn; reg [3:0]s_axi_awid; reg [31:0]s_axi_awaddr; reg [7:0]s_axi_awlen; reg [2:0]s_axi_awsize; reg [1:0]s_axi_awburst; reg s_axi_awvalid; wire s_axi_awready; reg [31:0]s_axi_wdata; reg [3:0]s_axi_wstrb; reg s_axi_wlast; reg s_axi_wvalid; wire s_axi_wready; wire [3:0]s_axi_bid; wire [1:0]s_axi_bresp; wire s_axi_bvalid; reg s_axi_bready; reg [3:0]s_axi_arid; reg [31:0]s_axi_araddr; reg [7:0]s_axi_arlen; reg [2:0]s_axi_arsize; reg [1:0]s_axi_arburst; reg s_axi_arvalid; wire s_axi_arready; wire [3:0]s_axi_rid; wire [31:0]s_axi_rdata; wire [1:0]s_axi_rresp; wire s_axi_rlast; wire s_axi_rvalid; reg s_axi_rready; reg[31:0] ram_a [9:0]; integer i=0; initial $readmemh("F:/date0.txt",ram_a); initial begin // Initialize Inputs //....初值均賦為0 除 bready 外 s_aclk=0; s_aresetn=0; s_axi_awid=4'b0000; s_axi_awaddr=32'b0; s_axi_awlen=0; s_axi_awsize=0; s_axi_awburst=0; s_axi_awvalid=0; s_axi_wdata=0; s_axi_wstrb=0; s_axi_wlast=0; s_axi_wvalid=0; s_axi_bready=0; s_axi_arid=0; s_axi_araddr=0; s_axi_arlen=0; s_axi_arsize=0; s_axi_arburst=0; s_axi_arvalid=0; s_axi_rready=0; s_axi_bready = 1; // Wait 100 ns for global reset to finish #100; // Add stimulus here s_aresetn = 1; repeat(2) begin #100; //aw channel for(i=0;i<10;i=i+1)begin s_axi_awaddr = i; s_axi_awlen = 0; s_axi_awsize = 3'b010; s_axi_awburst = 0; #20; s_axi_awvalid = 1; #20; //wait(s_axi_awready == 1 && s_aclk == 1); s_axi_awvalid = 0; #100; //w channel s_axi_wdata = ram_a[s_axi_awaddr]; s_axi_wstrb = 4'b1111; s_axi_wlast = 1; s_axi_wvalid = 1; #20; s_axi_wlast = 0; s_axi_wvalid = 0; s_axi_wstrb = 4'b0; // end #100; //ar channel // for(i=0;i<10;i=i+1)begin s_axi_araddr = i; s_axi_arlen = 0; s_axi_arsize = 3'b010; s_axi_arburst = 0; #20; s_axi_arvalid = 1; #20; //wait(s_axi_arready == 1 && s_aclk == 1); s_axi_arvalid = 0; #100; //r channel s_axi_rready = 1; end end end always #10 s_aclk = ~s_aclk; blk_mem_gen_0 uuu(rsta_busy, rstb_busy, s_aclk, s_aresetn, s_axi_awid, s_axi_awaddr, s_axi_awlen, s_axi_awsize, s_axi_awburst, s_axi_awvalid, s_axi_awready, s_axi_wdata, s_axi_wstrb, s_axi_wlast, s_axi_wvalid, s_axi_wready, s_axi_bid, s_axi_bresp, s_axi_bvalid, s_axi_bready, s_axi_arid, s_axi_araddr, s_axi_arlen, s_axi_arsize, s_axi_arburst, s_axi_arvalid, s_axi_arready, s_axi_rid, s_axi_rdata, s_axi_rresp, s_axi_rlast, s_axi_rvalid, s_axi_rready); endmodule