Xilinx ZYNQ 7000+Vivado2015.2系列(三)之HelloWorld實驗(最小系統)(純PS)

前言:

使用的板子是zc702。用Vivado的IP核搭建最小系統,包括ARM核(CPU xc7z020),DDR3(4×256M),一個UART串列埠(Mini USB轉串列埠),純PS,通過串列埠打印出HelloWorld,工程雖小,五臟俱全,算是一種朝聖。配置要和板子對應,大家注意修改。

操作步驟:

硬體部分

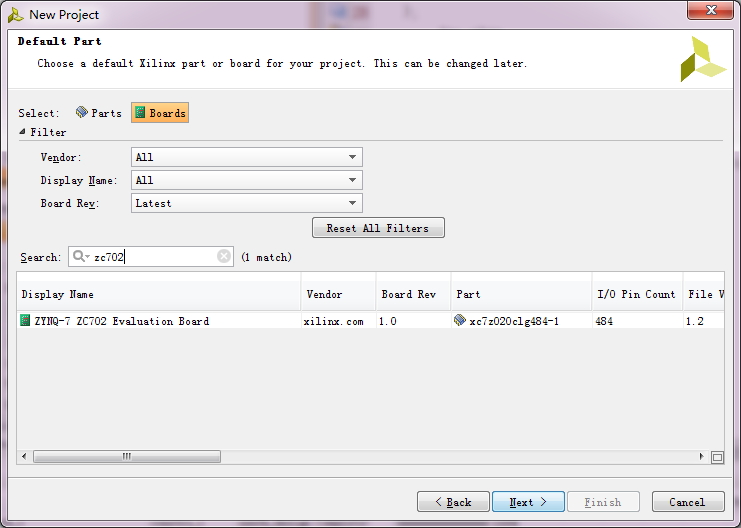

1. 新建Vivado工程。選擇晶片型號xc7z020clg484_1或者點選Boards選擇zc702

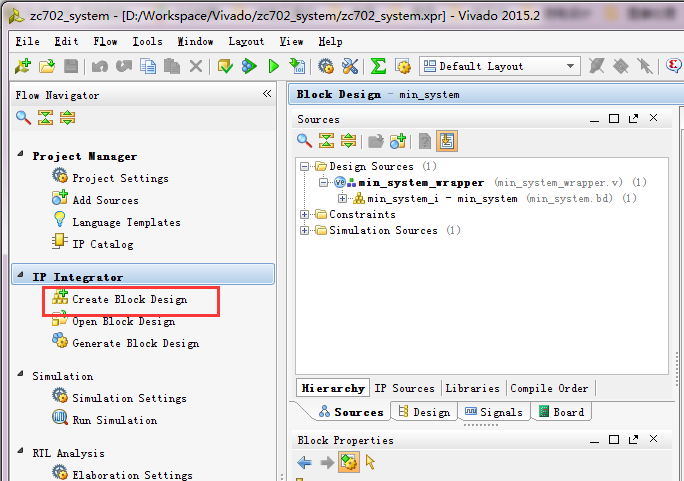

2.單擊Create Block Design, 命名

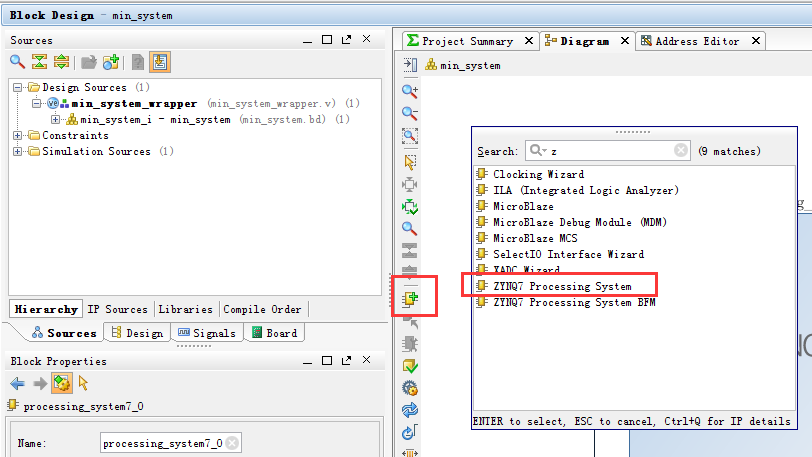

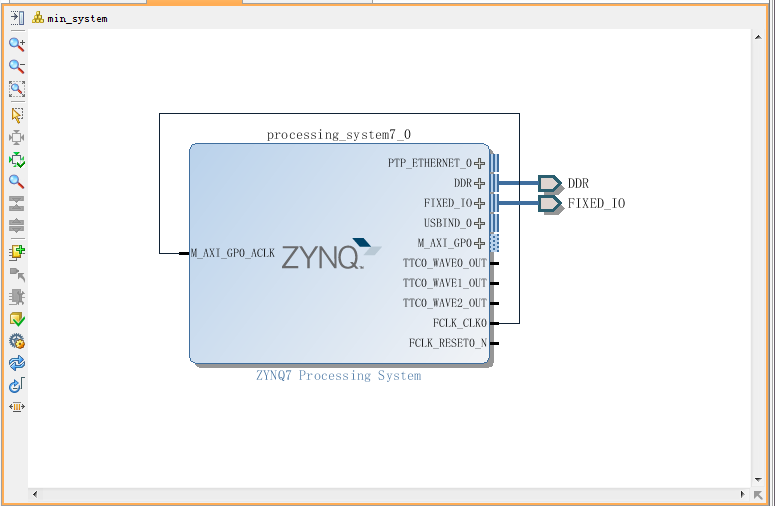

3.新增IP,ZYNQ7 Processing System

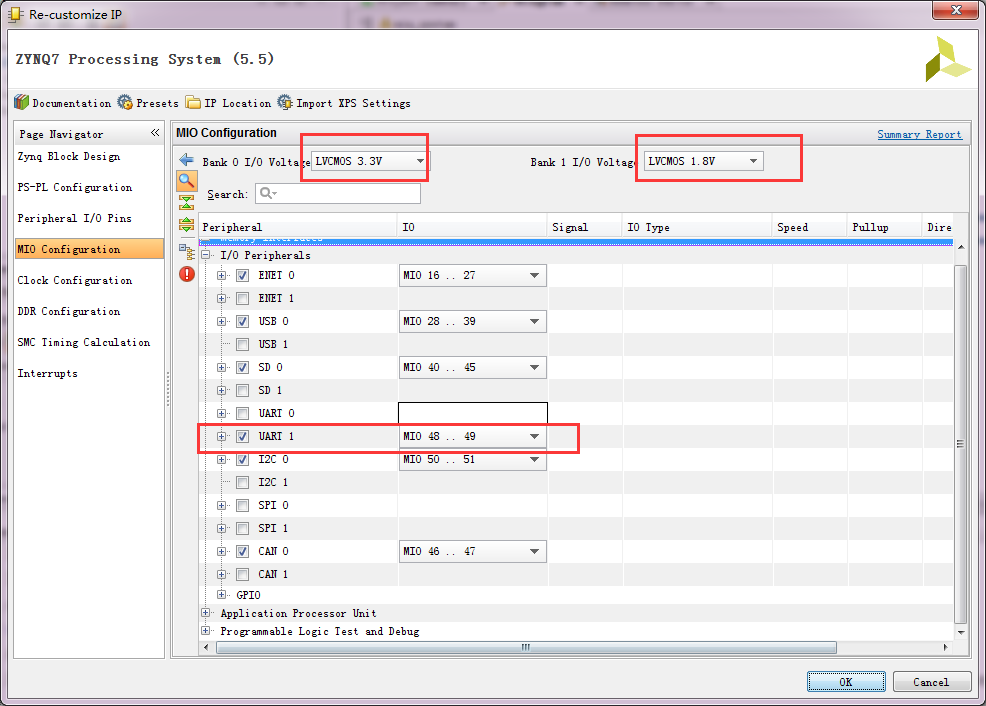

4.雙擊新增的IP,設定如下(主要是設定時鐘,記憶體,輸出,預設設定就省略不介紹了,紅色部分要設定對):

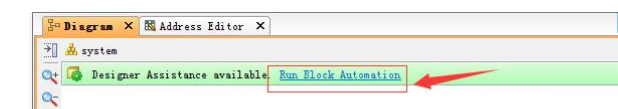

5.單擊上方藍字Run Block Automation ,然後將滑鼠放在引腳處, 滑鼠變成鉛筆後迚行拖拽連線,這是給PL時鐘,完全可以不連,本實驗用不到。

6.右擊 .bd檔案, 單擊Generate Output Products

點選Generate:

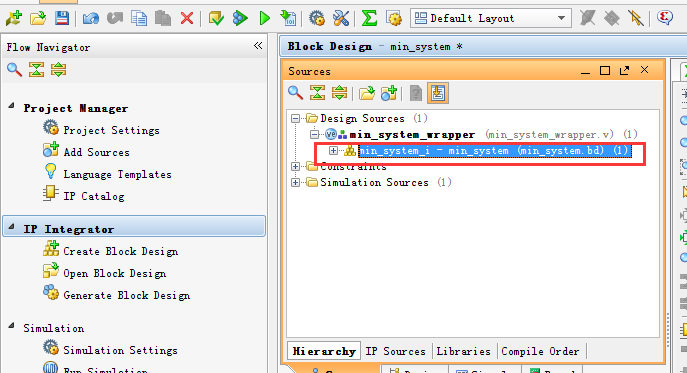

7.右擊 .bd檔案, 選擇Create HDL Wrapper ,產生頂層檔案,選擇 Let Vivado manager wrapper and auto-update

點擊OK

8. 產生Bit檔案

9.File->Export->Export Hardware,勾選 Include bitstream

10.File->Launch SDK

軟體部分

定製的硬體和地址空間分配

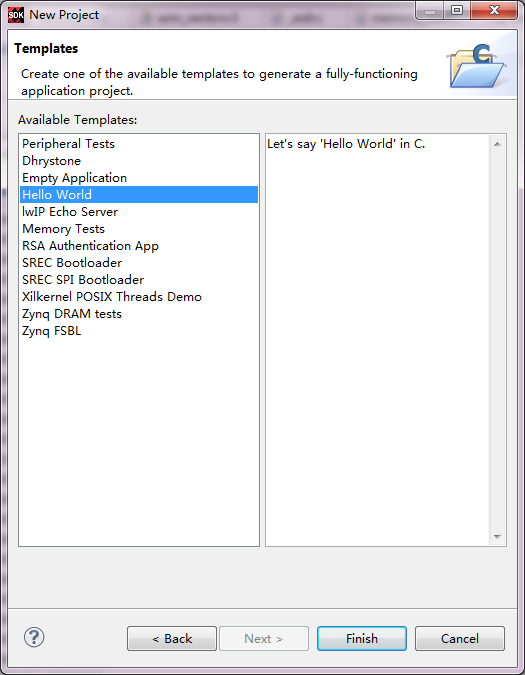

1.File->New->Application Project ,命名,點選next,選擇自帶的模板HelloWorld

檢視一下生成的程式碼

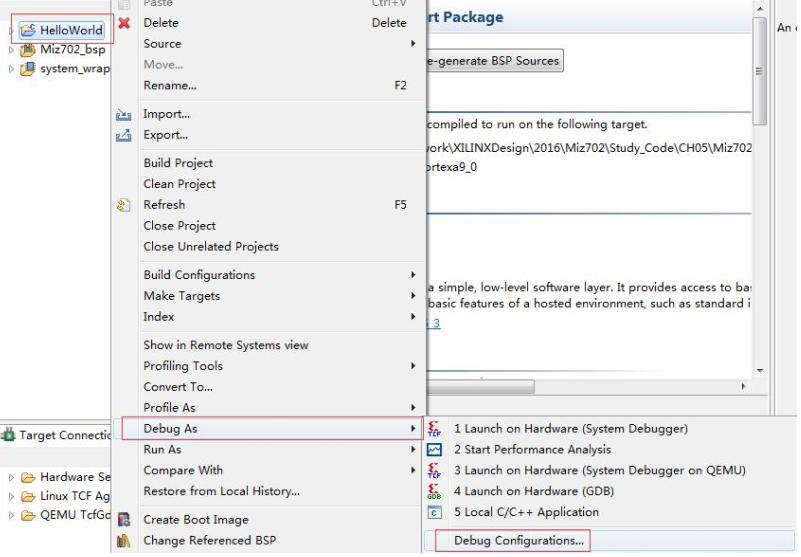

2.右擊專案名,Debug as-->Debufg Configuration

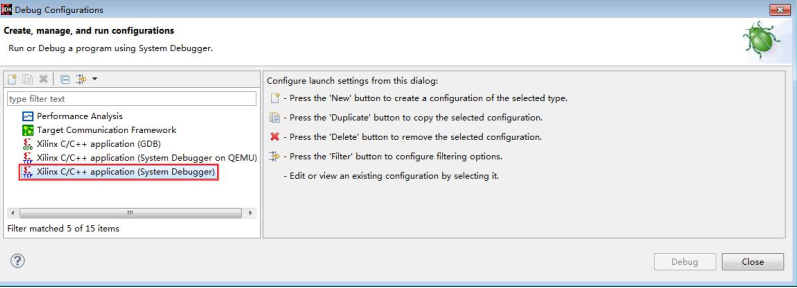

3.雙擊

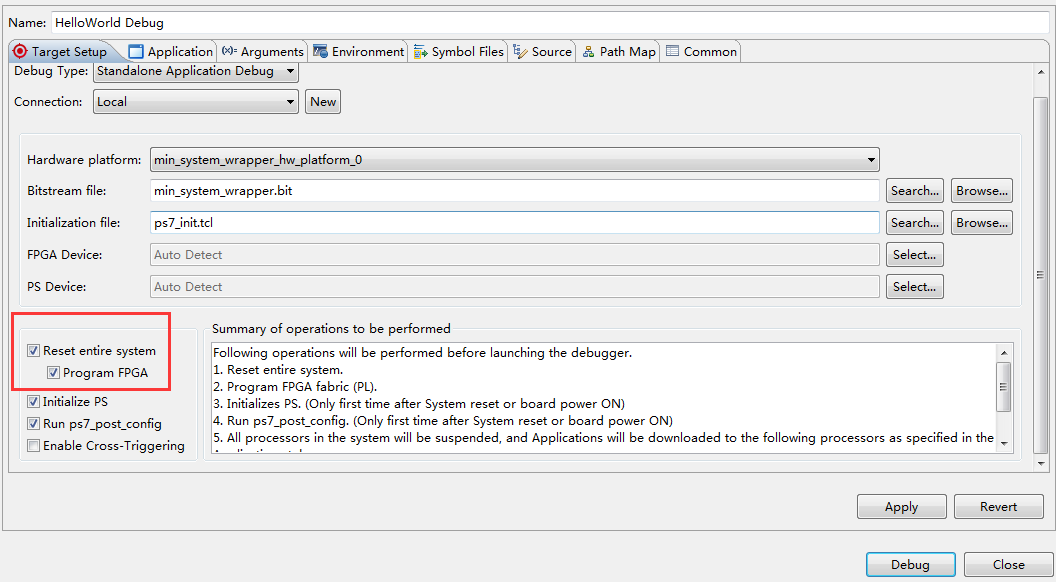

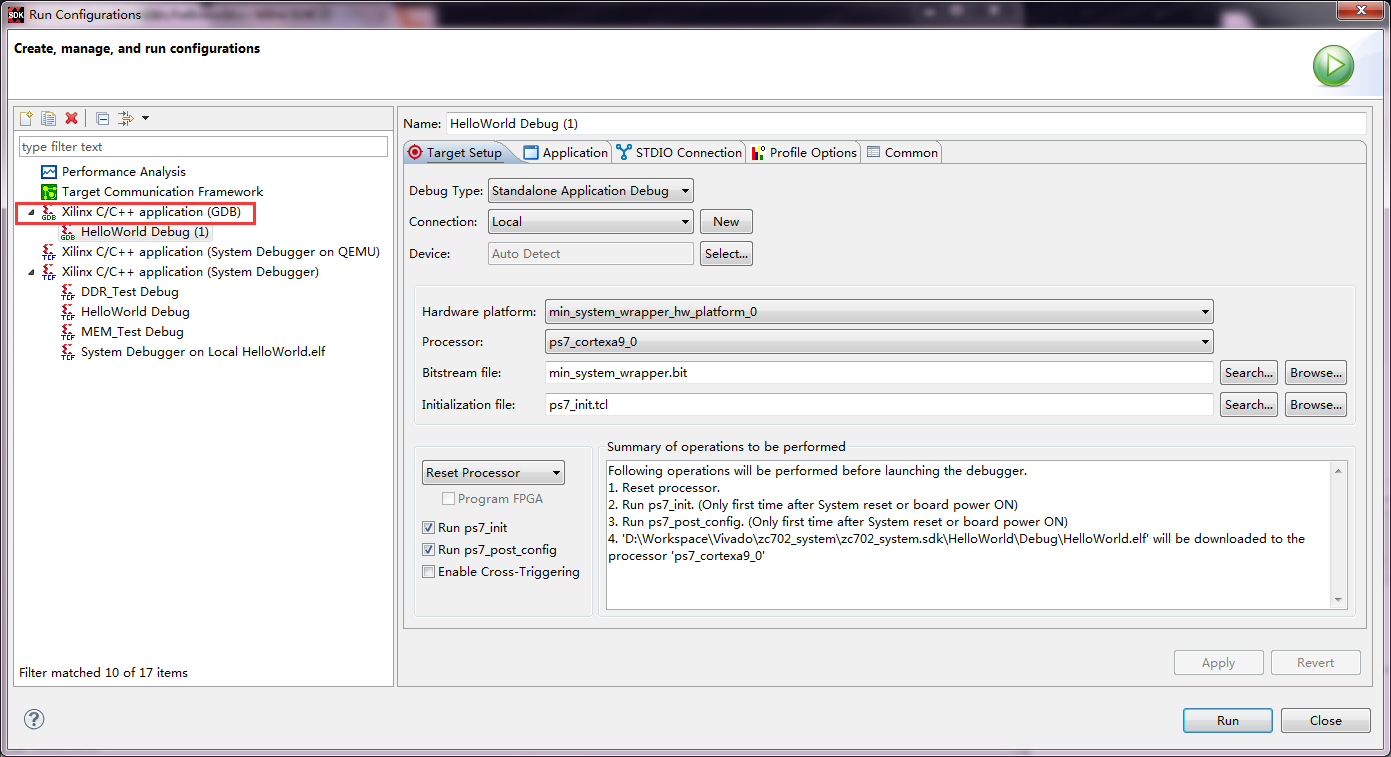

4,勾選,FPGA上電,點選Apply,點選Debug

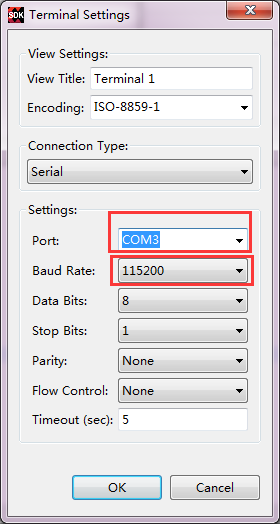

5.Debug介面(右上角可切換)裡的Terminal視窗 設定埠(自動識別),波特率(115200),連線串列埠

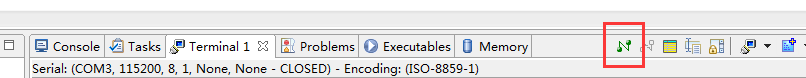

6.Debug介面 點選這個啟動程式

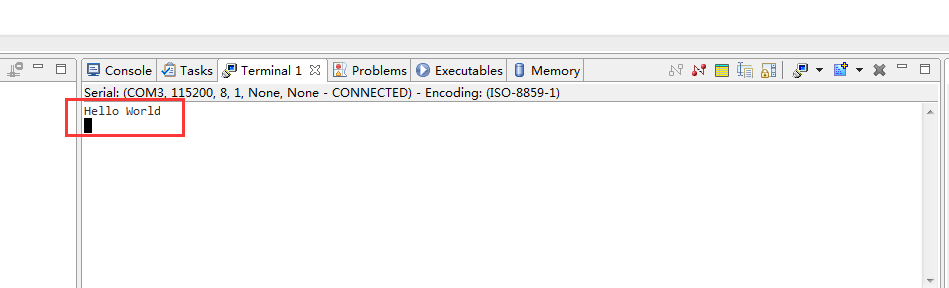

7.在串列埠除錯助手串列埠Terminal裡可見看見列印的資訊

或者直接run:

右擊工程名-->run as -->run configrations

雙擊紅色框選項:

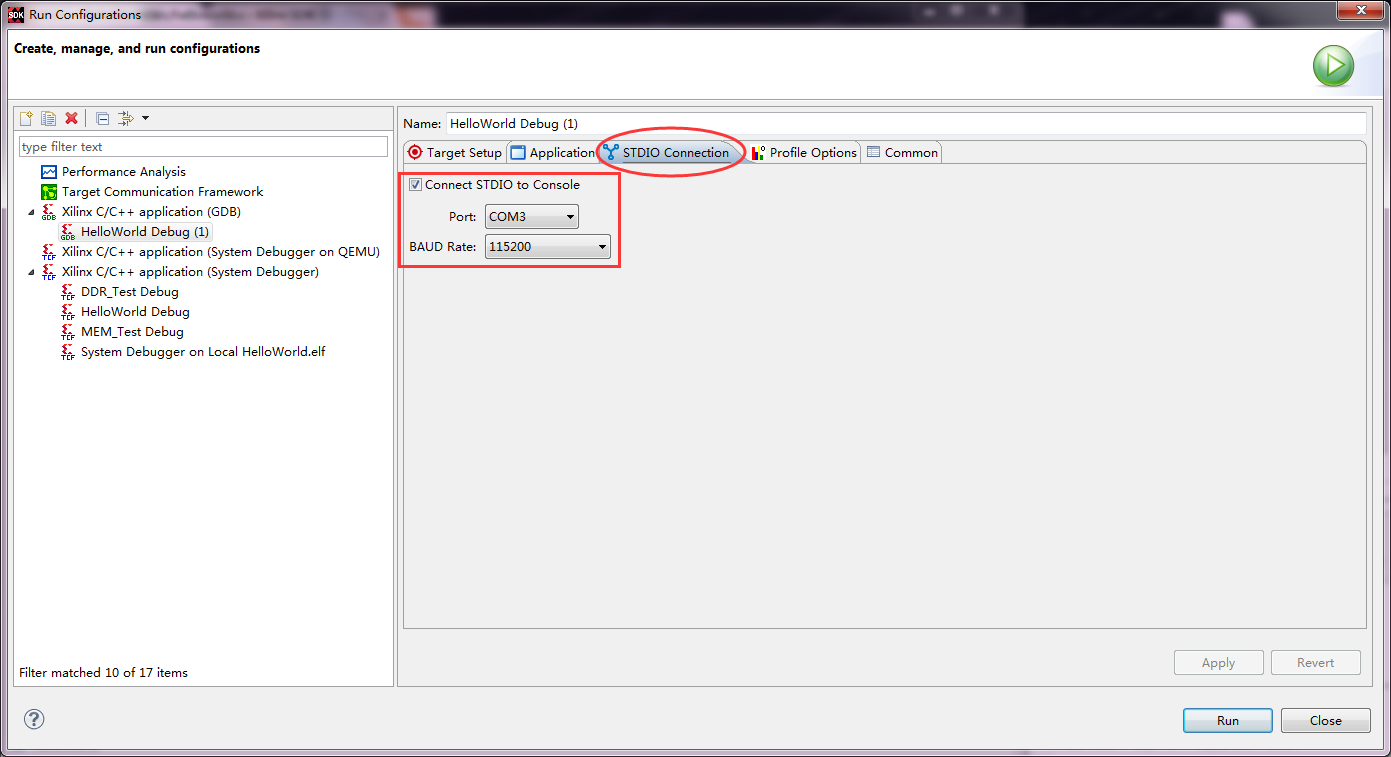

在STDIO Connection視窗設定串列埠資訊:

點選Apply,點選Run,在Console視窗可以看見列印的資訊:

總結:

Vivado+SDK設計流程初識,裡面的每一步要在後續過程中理解是什麼意思,就不會雲裡霧裡了。軟體部分的程式設計也是今後學習的一個要點。