【 Vivado 】時鐘組(Clock Groups)

Vivado會分析所有XDC約束時鐘間的時序路徑。通過set_clock_groups約束不同的時鐘組(clock group),Vivado在時序分析時,當source clock和destination clock屬於同一個時鐘組時,才會分析此時序路徑;而source clock和destination clock屬於不同時鐘組時,則會略過此時序路徑的分析。下面講解一下set_clock_groups約束:

Asynchronous Clock Groups

為了判別劃分時鐘組,將不同的時鐘劃分成以下兩類:

a. Synchronous Clocks

當兩個時鐘間的相位是固定的,則可以稱這兩個時鐘為同步時鐘(synchronous clock)。一般同源,如由同一個MMCM or PLL產生的兩個時鐘可以稱為同步時鐘。因此可以將主時鐘和與之對應的衍生時鐘約束成同一個時鐘組。

b. Asynchronous Clocks

無法判定兩個時鐘間相位時,則可以稱這兩個時鐘為非同步時鐘(asynchronous clocks)。兩個來自不同晶振的時鐘,一定是非同步時鐘。通常情況下設計中不同的主時鐘肯定是非同步時鐘,因此可以將這兩個主時鐘及其衍生時鐘約束成不同的時鐘組。

對於非同步時鐘,由於其兩個時鐘間相位不固定,時序分析的結果定然不確切,因此這部分的分析可以通過設定時鐘組約束忽略,但是這並不意味著這部分的設計能工作正常;對於非同步時鐘間的設計,必須做跨時鐘域處理,避免亞穩態的產生。

非同步時鐘組約束命令如下:

set_clock_groups-asynchronous-group [get_clocks {clk_Aclk_B}]

-group [get_clocks {clk_C}]-group …

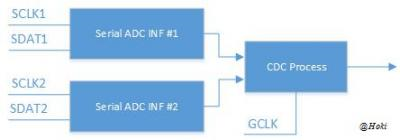

如圖1中結構,序列AD1和序列AD2介面都帶有隨路時鐘SCLK1和SCLK2,SCLK1和SCLK2屬於非同步時鐘;ADC串並轉換後的資料需要經過跨時鐘域處理(CDC),轉到GCLK主時鐘域,GCLK與ADC的時鐘也屬於非同步時鐘,因此約束命令如下:

set_clock_groups-asynchronous -group [get_clocks {SCLK1}]

-group [get_clocks {SCLK2}] -group [get_clocks {GCLK}]

(圖1)

Exclusive Clock Groups

在有些設計中,可能需要不同的工作模式,對應需要不同的時鐘輸入,通過時鐘選擇模組選擇需要的時鐘,如BUFGMUX,BUFGCTRL or A LUT。但是這些輸入的不同時鐘間是互斥的,即一個模式只允許一個時鐘輸入,不同時鐘間是沒有時序關係,因此只需單獨對每個時鐘做時序分析即可,新增互斥時鐘組可使Vivado進行時序分析時忽略互斥時鐘組間的時序路徑,約束命令如下:

set_clock_groups -logically_exclusive -group{clk_A} -group {clk_B}

或

set_clock_groups –physically_exclusive -group{clk_A} -group {clk_B}

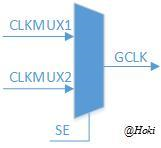

如圖2中結構,可將CLKMUX1,CLKMUX2約束成互斥時鐘組,約束命令如下:

set_clock_groups - physically_exclusive -group [get_clocks {CLKMUX1}]

-group [get_clocks {CLKMUX2}]

(圖2)