基於FPGA的cy7c68013a雙向通訊實驗

基於FPGA的cy7c68013a雙向通訊實驗

本實驗是基於FPGA的cy7c68013a的USB雙向通訊實驗,以前折騰過一段時間cy7c68013a,沒有入門時感覺好難,入門了就會感覺很簡單。本教程主要內容:

1.cy7c68013a的韌體編寫,以及生成iic韌體和下載韌體。

2.cy7c68013a的slave模式,以及他的讀寫時序

3.cy7c68013a的FPGA的上板測試,包括髮送和接受兩部分

一、驅動

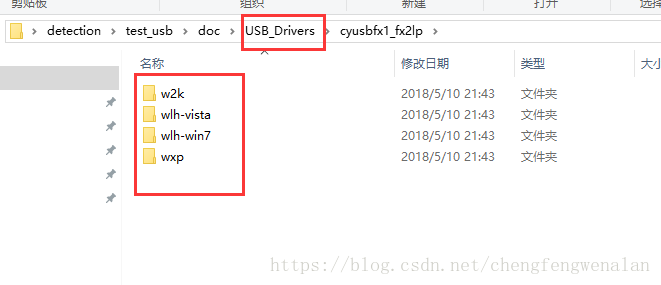

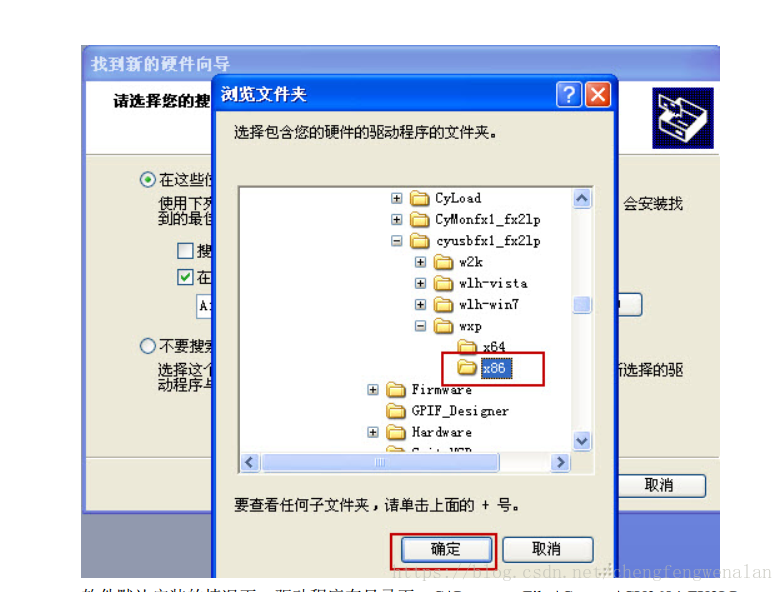

在進行試驗前要先安裝好cypress提供的usb驅動,插上usb後,電腦就會檢測到未識別的裝置,這時開啟裝置管理器,右鍵未識別的usb,然後手動選擇驅動,驅動會在本教程最後的連結中給出

二、韌體

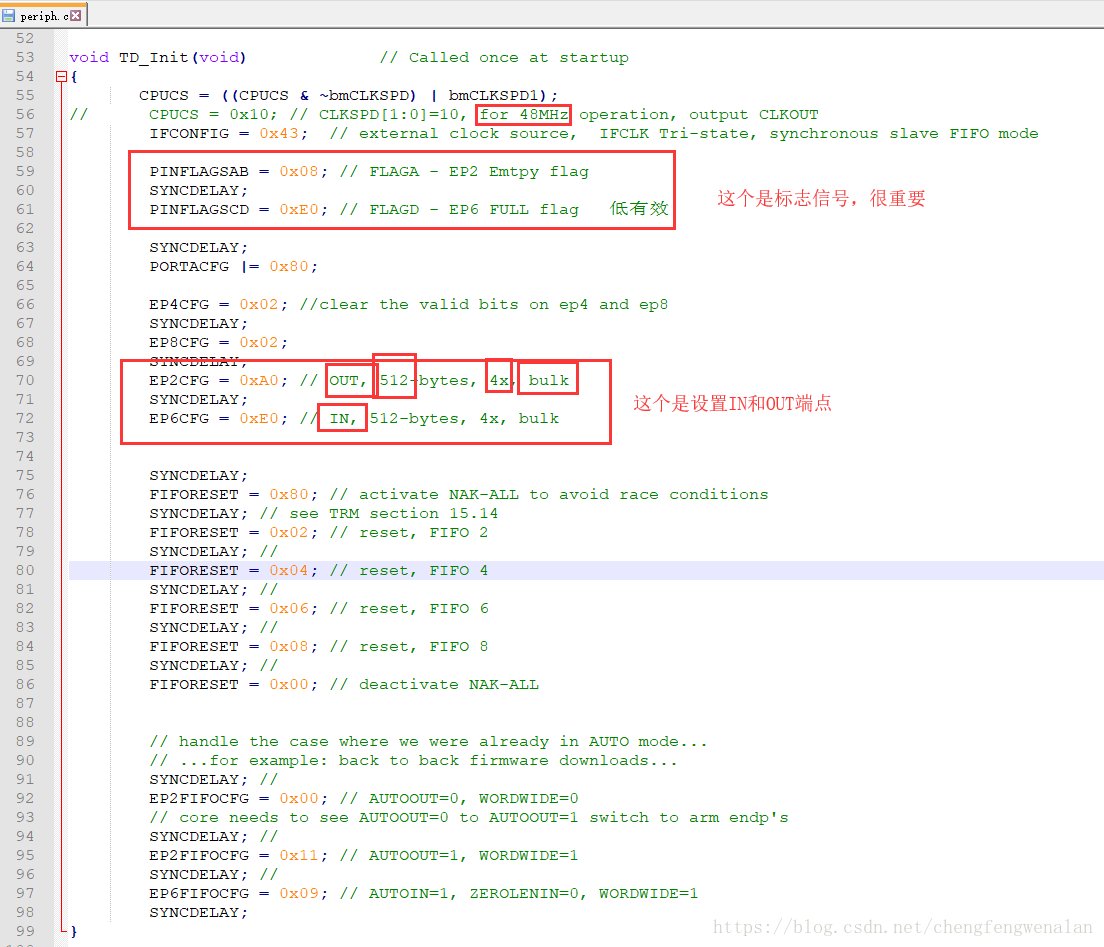

cy7c68013a想要正常工作,就得給他編寫好相應的韌體,然後再固化到其內部,當然PC也是需要安裝相應的驅動的,韌體的編寫主要是確定IN和OUT端點,以及一些標誌訊號。

韌體只需要改這些引數,這裡我都寫好了,大家就不需要再改了,很容易看出我設定的時鐘是48MHz,,然後設定

EP2為OUT端點,512位元組,4緩衝,bulk (注意OUT,IN都是相對PC來說的,OUT表示PC--->cy7c68013a,IN則相反)

EP6為IN端點,512位元組,4緩衝,bulk

flag_a 為EP2的EF,也就是空標誌訊號,為低時表示空,也就是沒有資料過來,為高則表示有資料來了

flag_d 為EP6的FF,也就是滿標誌訊號,為低時表示寫滿了,這時再去寫就是無效寫了,為高則表示沒有寫滿,可以繼續寫。

我寫好的韌體所在資料夾:韌體原始碼什麼的都在Firmware檔案中

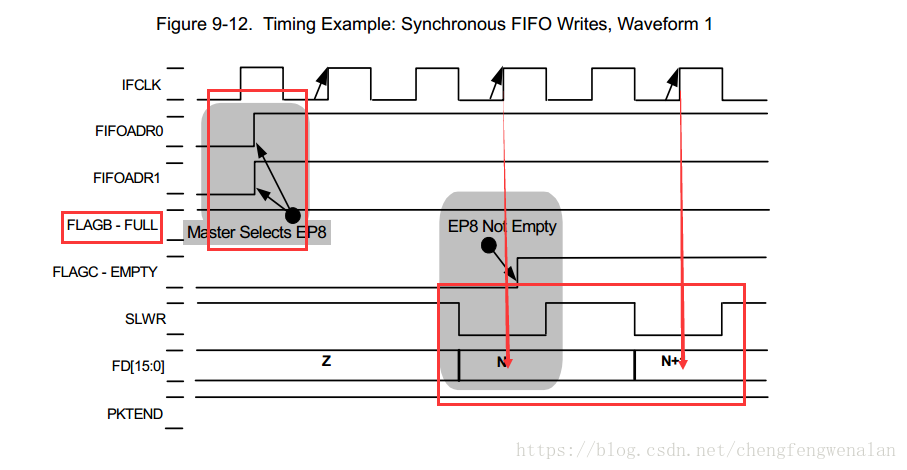

三、slave的寫時序

有圖很容易看出,再寫之前要先把FIFOADR確認好,這個決定了你寫的物件是誰

然後在該fifo非滿時(相應的FF標誌位高),才可以進行寫操作,這個時序很簡單,就是拉低slwr訊號就可以了,注意FD要與slwr對齊。

注意:寫操作時,slwr與FD的資料都是FPGA來控制的,為了讓cy7c68013a更好的取樣,ifclk與clk反向之後再發送給cy7c68013a.

四、slave讀操作

讀時序跟寫也是類似的,再讀之前先確定FIFOADR,然後拉低sloe,這時FD匯流排就會出現第一個資料,然後檢測到slrd為低時,FD就會顯示下一個資料。

五、FPGA與cy7c68013a通訊

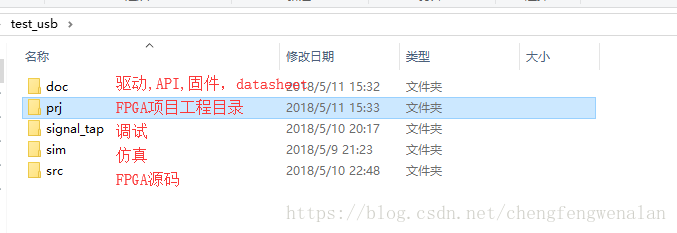

前面主要是一些準備工作,現在開始進入正式的通訊過程,專案工程如下:

具體程式碼都已經有了詳細註釋了,自己去看看程式碼就知道了,這裡就不詳細說了

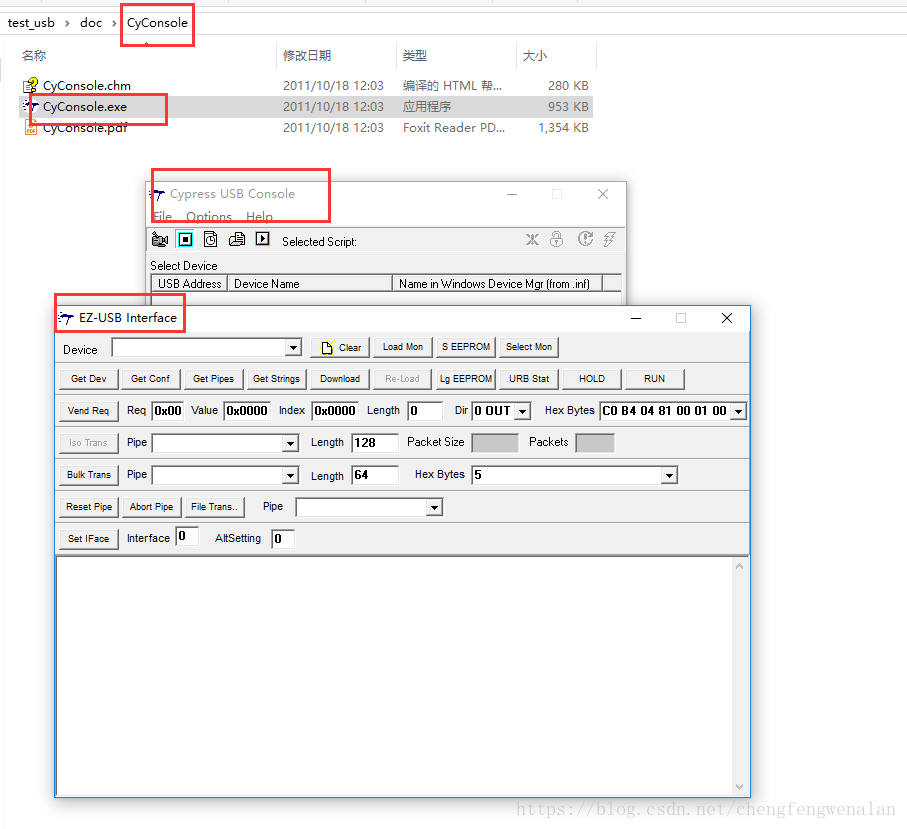

本教程所用的除錯工具是官方的工具

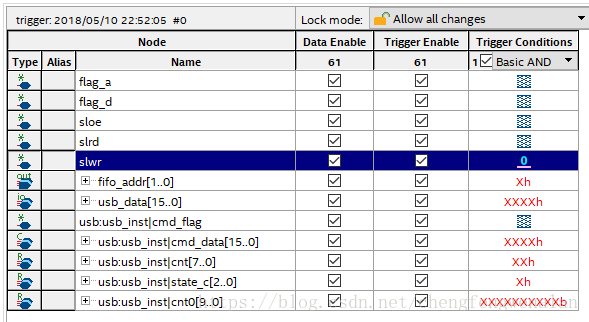

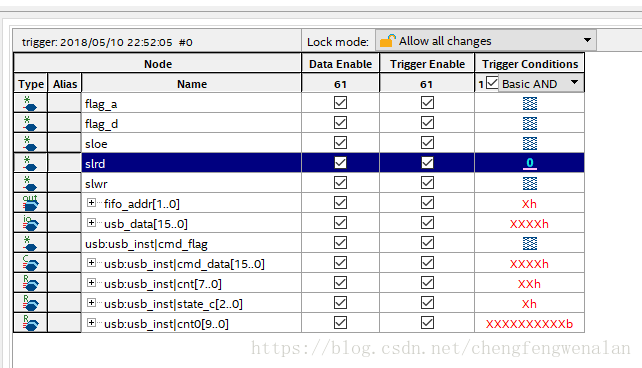

下面給出寫的signal tap 的除錯截圖

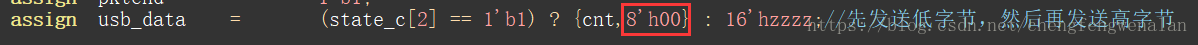

寫是一次寫512個位元組資料,0-255,注意usb的fifo是一次傳送16位的,也就是2個位元組。先發送低位元組,然後再發送高位元組,這我直接把低位元組給賦值為0了

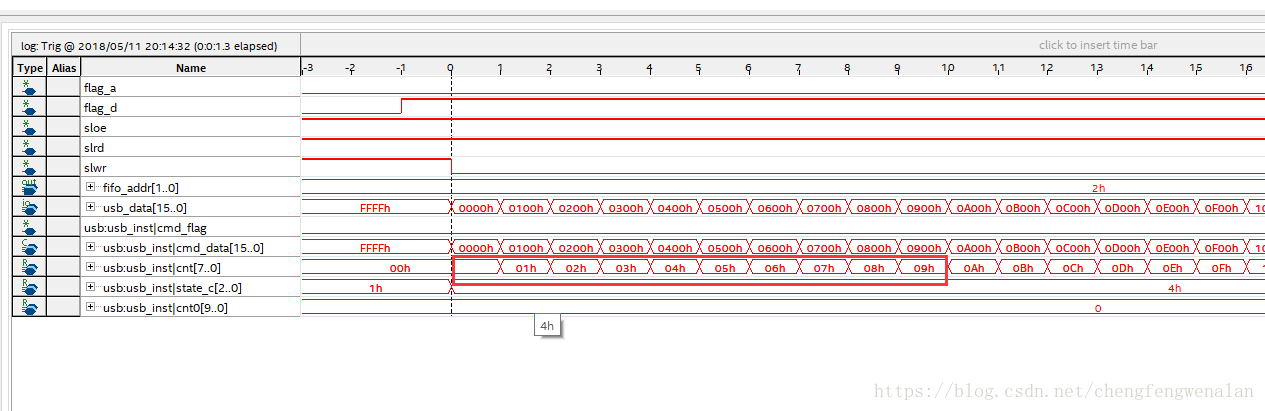

前面區域性放大圖

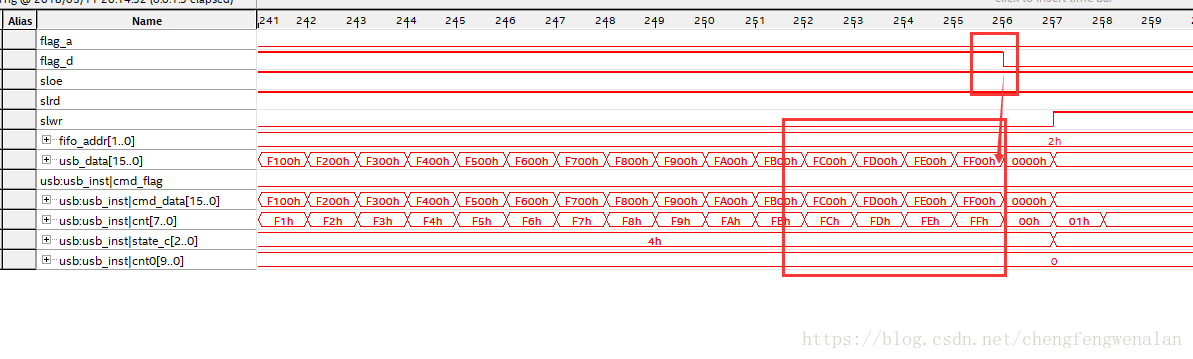

後面區域性放大圖,注意只有在flag_d為高時,slwr為低才是有效寫,否則就是無效寫,因為當flag_d為低時,表示寫滿了,這時fifo就會棄之後的寫資料了(因為已經寫滿了,也裝不下了是吧,總不能硬塞是吧,哈哈~)

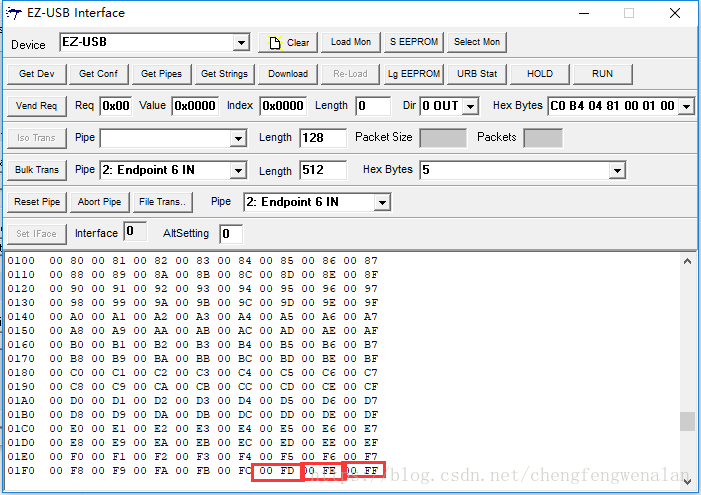

PC端接受到的資料要2個位元組一起讀,因為usb是16位傳送的,可以看出接受到的資料的確是0000-00FF

注意:pc接受資料按我標的編碼順序執行

---------------------------------------------~~~我是分割線~~~---------------------------------------------------------------

下面輪到“讀”出場了

pc傳送資料按1-->2-->3的步驟,可以看出我們傳送了12 34 56 78 這4個位元組

注意這裡我是設定了cmd_flag標誌訊號的,只有cmd_flag為高時的cmd_data的資料才是有效的,也就是pc傳送過來的資料。

這裡順帶插一嘴:

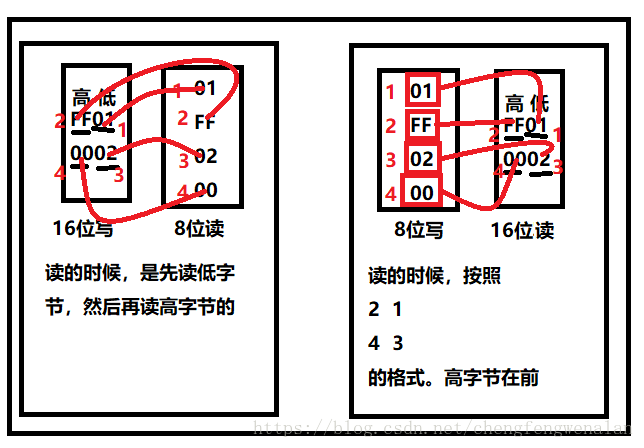

alter 的fifo ip 是可以讀寫位寬不一致的,具體看下面的圖

由上圖可以看出這個和usb是一樣的格式,都是先發低位元組,然後再發高位元組。或者說先接受低位元組,然後再接受高位元組

至此本教程就全部介紹完了,講的雖然有點簡陋,但是基本的流程都已經講到了,比起網上其他的教程還是要好不少的哈(自我陶醉一下),具體的看我的原始碼。可以看出,使用cypress的usb還是比較簡單的,因為usb協議什麼的,他們都已經做好了,我們不需要考慮這些,要不然那一堆協議就看著頭疼,具體的看我給的下載連結,我會把本教程所用到的工具,程式碼全部分享出來,也歡迎大家評論提問,不足之處還望指正~

六、福利

原始碼下載連結:https://download.csdn.net/download/chengfengwenalan/10409008

基於FPGA的cy7c68013a雙向通訊實驗

本實驗是基於FPGA的cy7c68013a的USB雙向通訊實驗,以前折騰過一段時間cy7c68013a,沒有入門時感覺好難,入門了就會感覺很簡單。本教程主要內容:

1.cy7c68013a的韌體編寫,以及生成iic韌體和下載韌體。

2.cy7c68013a的slave模式,以及他的讀寫時序

3.cy7c68013a的FPGA的上板測試,包括髮送和接受兩部分

一、驅動

在進行試驗前要先安裝好cypress提供的usb驅動,插上usb後,電腦就會檢測到未識別的裝置,這時開啟裝置管理器,右鍵未識別的usb,然後手動選擇驅動,驅動會在本教程最後的連結中給出

二、韌體

cy7c68013a想要正常工作,就得給他編寫好相應的韌體,然後再固化到其內部,當然PC也是需要安裝相應的驅動的,韌體的編寫主要是確定IN和OUT端點,以及一些標誌訊號。

韌體只需要改這些引數,這裡我都寫好了,大家就不需要再改了,很容易看出我設定的時鐘是48MHz,,然後設定

EP2為OUT端點,512位元組,4緩衝,bulk (注意OUT,IN都是相對PC來說的,OUT表示PC--->cy7c68013a,IN則相反)

EP6為IN端點,512位元組,4緩衝,bulk

flag_a 為EP2的EF,也就是空標誌訊號,為低時表示空,也就是沒有資料過來,為高則表示有資料來了

flag_d 為EP6的FF,也就是滿標誌訊號,為低時表示寫滿了,這時再去寫就是無效寫了,為高則表示沒有寫滿,可以繼續寫。

我寫好的韌體所在資料夾:韌體原始碼什麼的都在Firmware檔案中

三、slave的寫時序

有圖很容易看出,再寫之前要先把FIFOADR確認好,這個決定了你寫的物件是誰

然後在該fifo非滿時(相應的FF標誌位高),才可以進行寫操作,這個時序很簡單,就是拉低slwr訊號就可以了,注意FD要與slwr對齊。

注意:寫操作時,slwr與FD的資料都是FPGA來控制的,為了讓cy7c68013a更好的取樣,ifclk與clk反向之後再發送給cy7c68013a.

四、slave讀操作

讀時序跟寫也是類似的,再讀之前先確定FIFOADR,然後拉低sloe,這時FD匯流排就會出現第一個資料,然後檢測到slrd為低時,FD就會顯示下一個資料。

五、FPGA與cy7c68013a通訊

前面主要是一些準備工作,現在開始進入正式的通訊過程,專案工程如下:

具體程式碼都已經有了詳細註釋了,自己去看看程式碼就知道了,這裡就不詳細說了

本教程所用的除錯工具是官方的工具

下面給出寫的signal tap 的除錯截圖

寫是一次寫512個位元組資料,0-255,注意usb的fifo是一次傳送16位的,也就是2個位元組。先發送低位元組,然後再發送高位元組,這我直接把低位元組給賦值為0了

前面區域性放大圖

後面區域性放大圖,注意只有在flag_d為高時,slwr為低才是有效寫,否則就是無效寫,因為當flag_d為低時,表示寫滿了,這時fifo就會棄之後的寫資料了(因為已經寫滿了,也裝不下了是吧,總不能硬塞是吧,哈哈~)

PC端接受到的資料要2個位元組一起讀,因為usb是16位傳送的,可以看出接受到的資料的確是0000-00FF

注意:pc接受資料按我標的編碼順序執行

---------------------------------------------~~~我是分割線~~~---------------------------------------------------------------

下面輪到“讀”出場了

pc傳送資料按1-->2-->3的步驟,可以看出我們傳送了12 34 56 78 這4個位元組

注意這裡我是設定了cmd_flag標誌訊號的,只有cmd_flag為高時的cmd_data的資料才是有效的,也就是pc傳送過來的資料。

這裡順帶插一嘴:

alter 的fifo ip 是可以讀寫位寬不一致的,具體看下面的圖

由上圖可以看出這個和usb是一樣的格式,都是先發低位元組,然後再發高位元組。或者說先接受低位元組,然後再接受高位元組

至此本教程就全部介紹完了,講的雖然有點簡陋,但是基本的流程都已經講到了,比起網上其他的教程還是要好不少的哈(自我陶醉一下),具體的看我的原始碼。可以看出,使用cypress的usb還是比較簡單的,因為usb協議什麼的,他們都已經做好了,我們不需要考慮這些,要不然那一堆協議就看著頭疼,具體的看我給的下載連結,我會把本教程所用到的工具,程式碼全部分享出來,也歡迎大家評論提問,不足之處還望指正~

六、福利

原始碼下載連結:https://download.csdn.net/download/chengfengwenalan/10409008