Verilog RTL 程式碼設計新手上路

1. 做一個4選1的mux,並且進行波形模擬 和2選1的mux對比,觀察資源消耗的變化:

實驗分析:4選1的mux實際上就是在2選1的mux上進行拓展,選用2位的控制訊號控制4位輸入訊號的選擇輸出

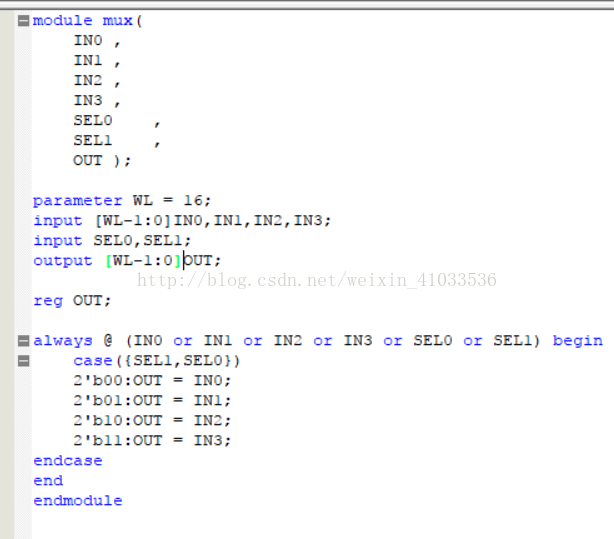

實驗程式碼設計如下:

RTL檢視如下:

波形模擬結果如下:

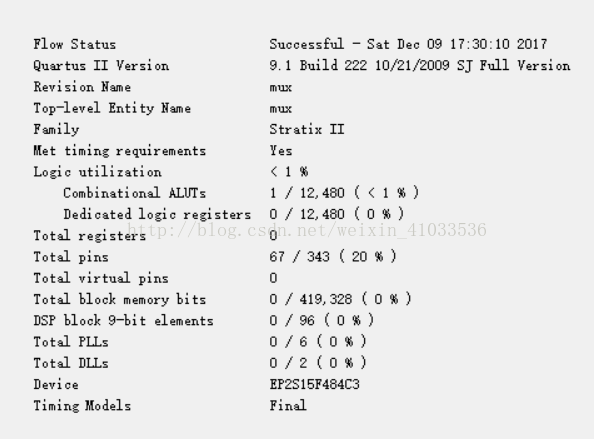

資源消耗變化如下:

4選1的mux

2選1的mux

2. 編寫一個4X4路交叉開關的RTL,然後編譯,看RTL View 比較2x2與4x4之間消耗資源的區別。通過對比資源,你有什麼結論?

實驗分析: 2X2路的交叉開關核心思想就是使用2個輸出分別對應1個1位的控制訊號,選擇該輸出哪一個輸入訊號。根據該思想設計4X4路的交叉開關,則每個輸出對應一個2位的控制訊號,從四個輸入訊號中選擇一個進行輸出,然後並聯輸出。

實驗程式碼設計如下:

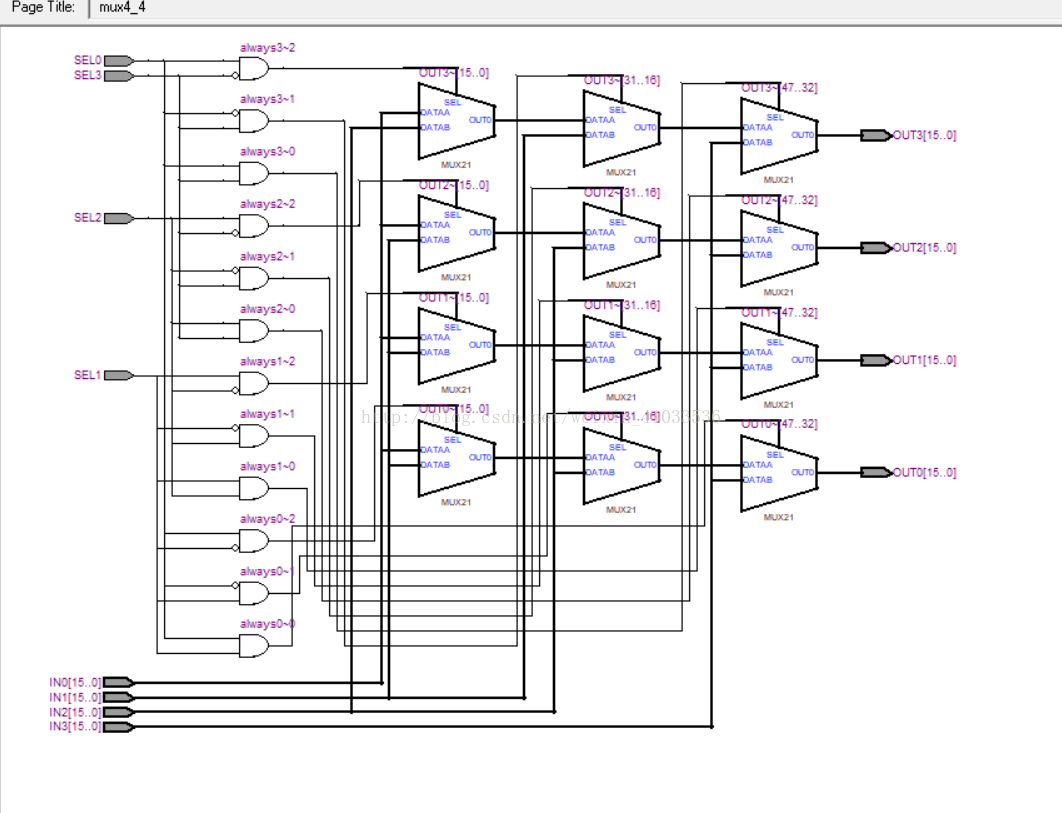

RTL檢視如下:

波形模擬結果如下:

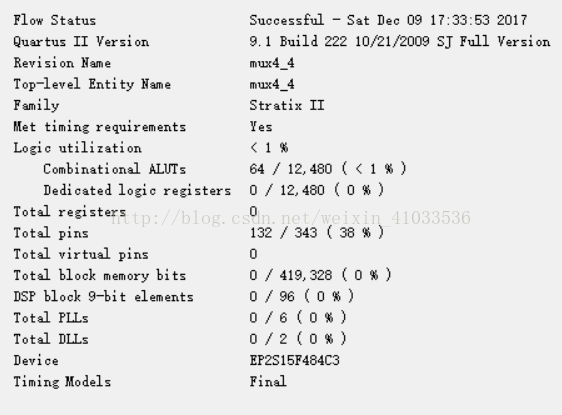

資源消耗對比如下:

4X4的交叉開關

2X2的交叉開關

可見4X4的交叉開關消耗資源成倍的增長了。

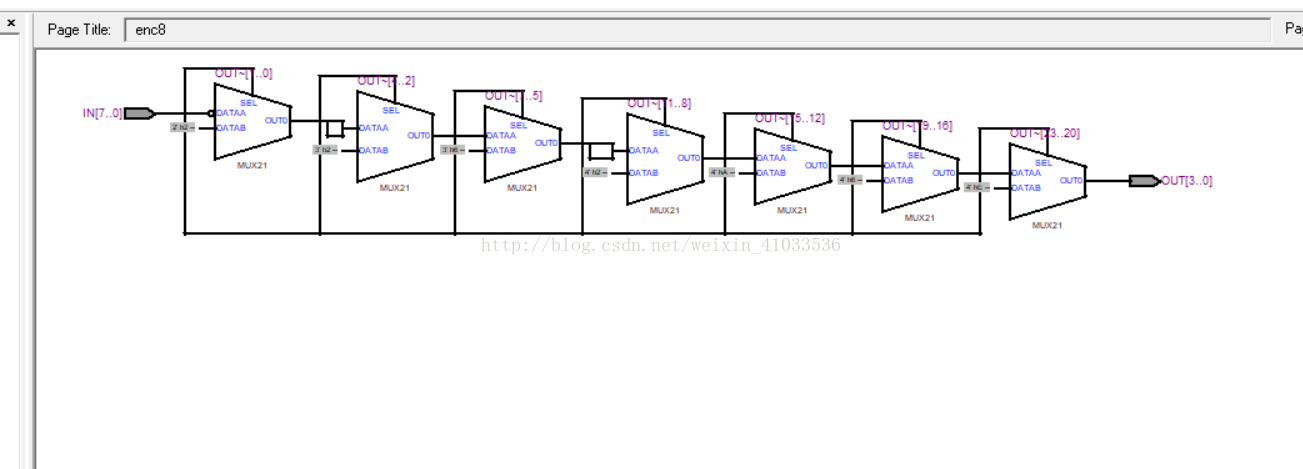

3. 編寫一個8輸入的優先編碼器,然後編譯,看RTL View:

實驗分析:4輸入的優先編碼器本質就是一個4位輸入的訊號對輸出進行控制,當對應為輸入1時,輸出與位數對應的數值,且高位輸入控制優先。編寫8輸入的優先編碼器實際上就是對4輸入的位數進行一個簡單拓展。

實驗程式碼設計如下:

RTL檢視如下:

波形模擬結果如下:

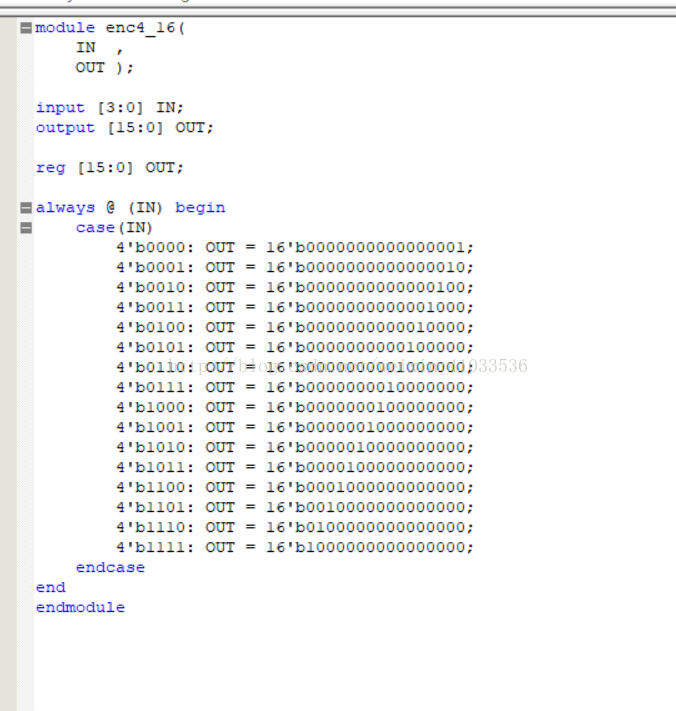

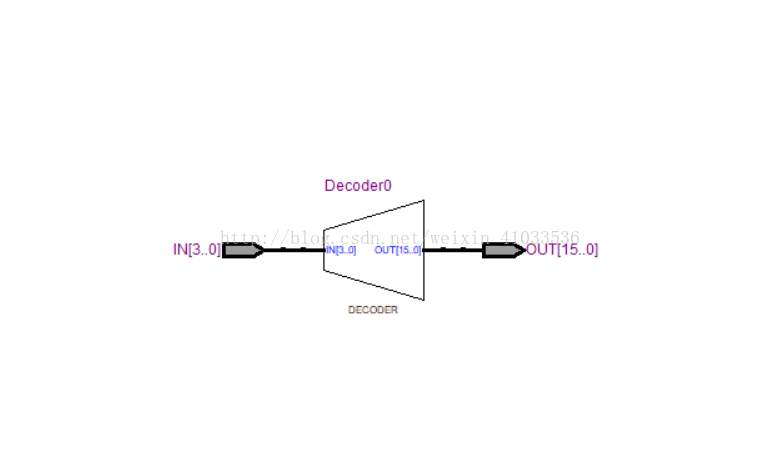

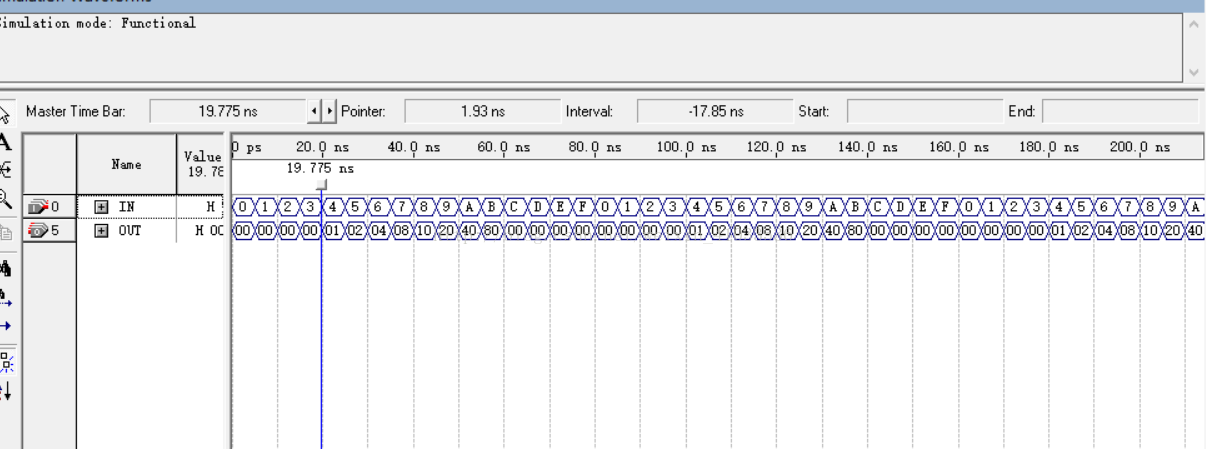

4. 編寫一個4-16的譯碼器,編譯;和3-8譯碼器對比資源開銷;看RTL View:

實驗分析:3-8譯碼器即3位輸入的2進位制值對應相應位置的輸出位輸出1。編寫4-16譯碼器本質上是對3-8譯碼器輸入、輸出位數的一個拓展。

實驗程式碼設計如下:

RTL檢視如下:

波形模擬結果如下:

資源消耗變化如下:

3-8譯碼器

4-16譯碼器

輸入多了一位、輸出多了八位的情況下資源消耗幾乎多了一倍,可見資源消耗主要與輸出位數正相關。

5. (1)把加法器的輸出訊號改成4位元位寬,編譯,波形模擬。觀察輸出結果,說出輸出和輸入的對應關係。

(2)把加法器的輸入訊號改成8位元位寬,編譯,波形模擬。觀察加法器的輸出延遲,和4位元輸入位寬的情況對比,你有什麼結論,為什麼?

實驗分析:例子程式給出無符號加法器是一個4位輸入5位輸出的加法器,即兩個0~15的數相加,其結果範圍應該在0~30。當輸入仍為4位而輸出改為4位時,輸出結果範圍僅為0~15,當兩位輸入相加結果大於15後輸出結果會出現錯誤,僅能輸出正確結果的後四位;而輸入改為8位而輸出仍為5位時,兩個0~127的數相加,可結果範圍只能為0~31,這時只能輸出正確結果的後5位,然而加法器仍然要運算正確結果的前3位,所以輸出延時應該要大於4輸入-5輸出的加法器。

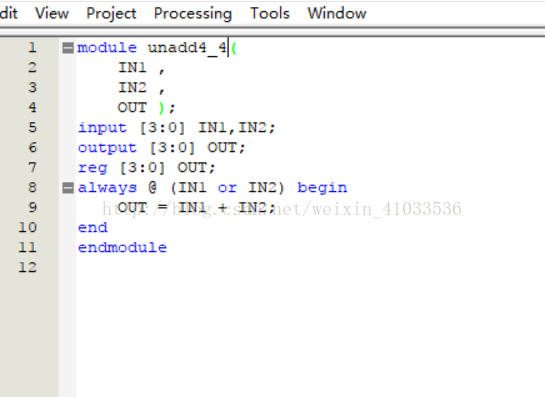

實驗程式碼設計如下:

4輸入-4輸出無符號加法器

8輸入-5輸出無符號加法器

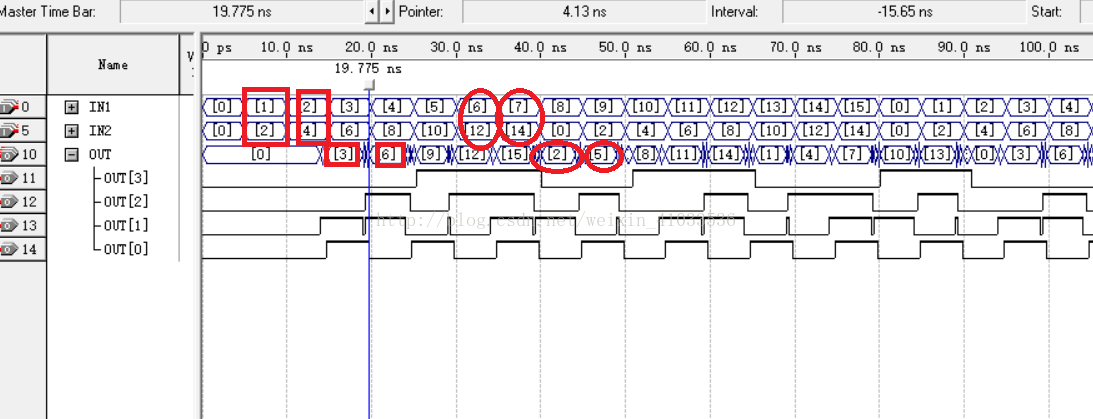

波形模擬結果如下:

4輸入-4輸出無符號加法器

可見當正確結果大於15後只能輸出正確結果的後4位。

8輸入-5輸出無符號加法器

可見其輸出時延稍大於4輸入的無符號加法器。

6. 把加法器的輸出訊號改成4位元位寬,編譯,波形模擬。觀察輸出結果,觀察輸出結果在什麼時候是正確的?。 把加法器的輸入訊號改成8位元位寬,編譯,波形模擬。觀察加法器的輸出延遲,和4位元輸入位寬的情況對比,你有什麼結論,為什麼?

實驗分析:其基本原理與上面無符號加法器相同,只不過其運演算法則變為補碼運算。對於組合邏輯閘的層面來說,主要是“Signed”關鍵字生成的。

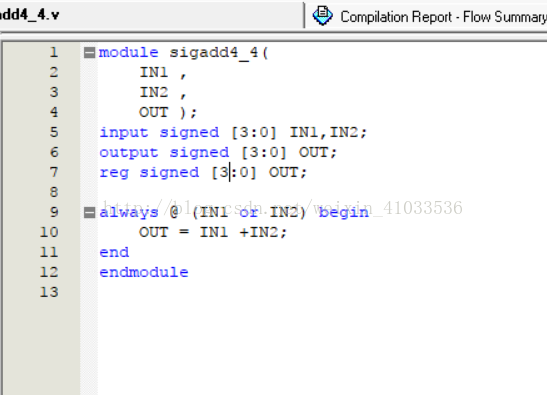

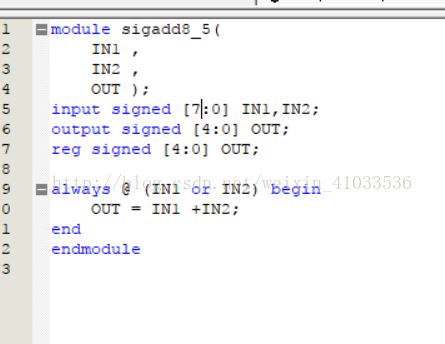

實驗程式碼設計如下:

4輸入-4輸出補碼加法器

8輸入-5輸出補碼加法器

波形模擬結果如下:

4輸入-4輸出補碼加法器

8輸入-5輸出補碼加法器

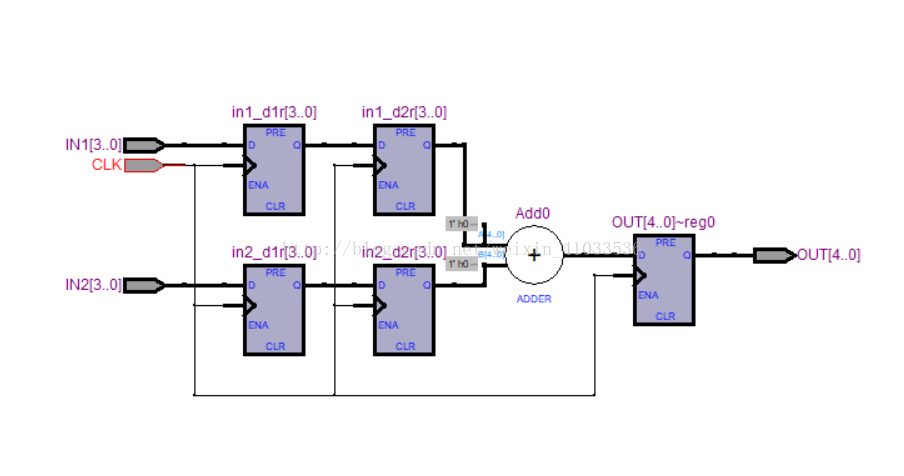

7. 不改變流水線的級數,把加法器的輸入訊號改成8位元位寬,編譯,波形模擬,和不帶流水線的情況對比一下,你有什麼結論? 在8位元輸入位寬的情況下,在輸入上再新增一級流水線,觀察編譯和模擬的結果,你有什麼結論?

實驗分析:與不加流水線的加法器相比,帶流水線的加法器即在加法器的輸入與輸出都連線了D觸發器,有效的減少了組合邏輯的競爭與冒險,從而明顯減少了“毛刺”的長度。而流水線的級數越高,毛刺也隨之越短,但輸出的時延也會相應的對一個時鐘週期。

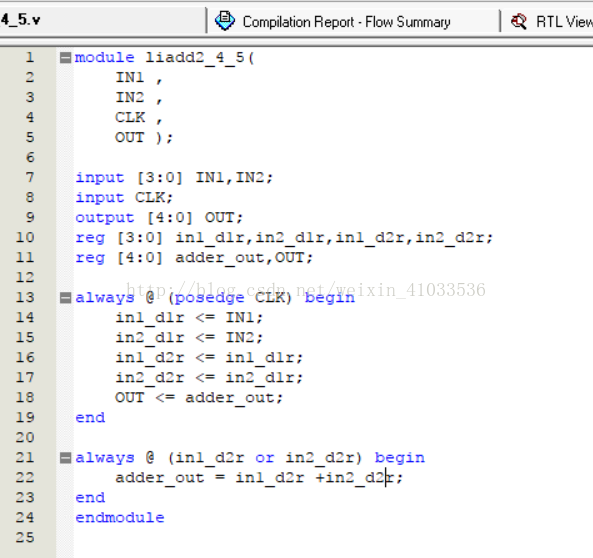

實驗程式碼設計如下:

8輸入-5輸出帶流水線加法器

4輸入-5輸出2級流水線加法器

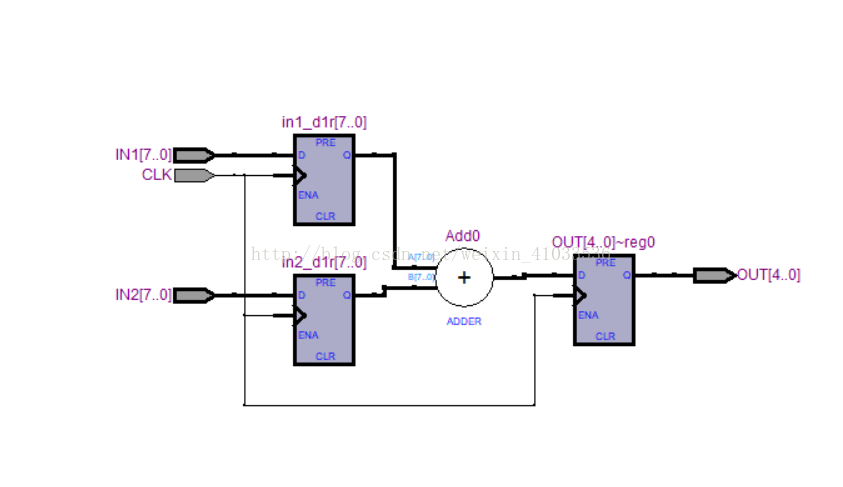

RTL檢視如下:

8輸入-5輸出帶流水線加法器

4輸入-5輸出2級流水線加法器

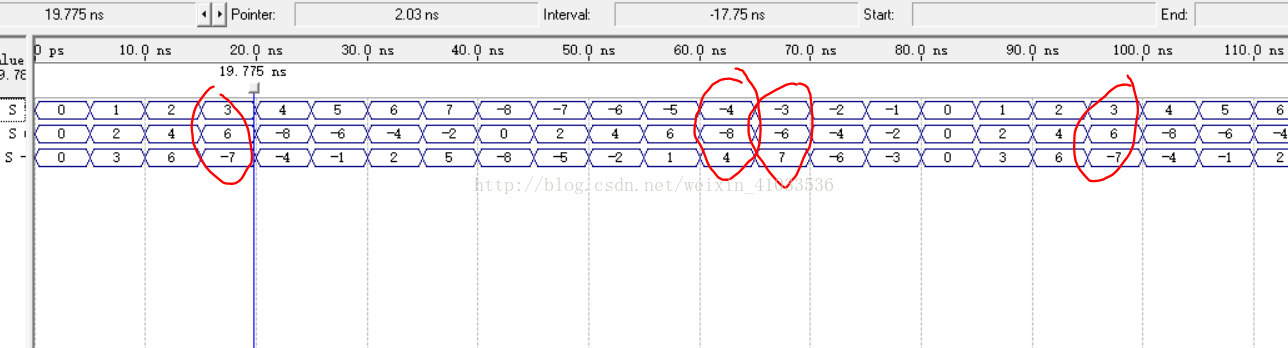

波形模擬結果如下:

8輸入-5輸出帶流水線加法器

4輸入-5輸出2級流水線加法器

8. (1)改變乘法器的輸入位寬為8位元,編譯,波形模擬,觀察訊號毛刺的時間長度。

(2)選一款沒有硬體乘法器的FPGA晶片(例如Cyclone EP1C6)對比8位元的乘法器和加法器兩者編譯之後的資源開銷(Logic Cell的數目)

(3)編寫一個輸入和輸出都有D觸發器的流水線乘法器程式碼,編譯後波形模擬,觀察組合邏輯延遲和毛刺的時間,和不帶流水線的情況下對比。

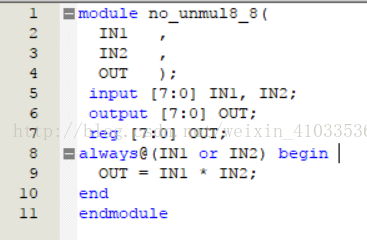

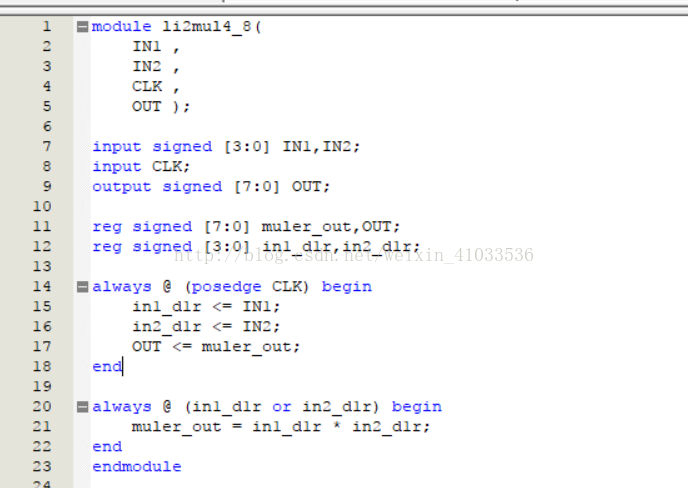

實驗程式碼設計如下:

8輸入-8輸出無符號乘法器

無硬體乘法器晶片的8輸入-8輸出無符號乘法器

4輸入-8輸出帶流水線乘法器

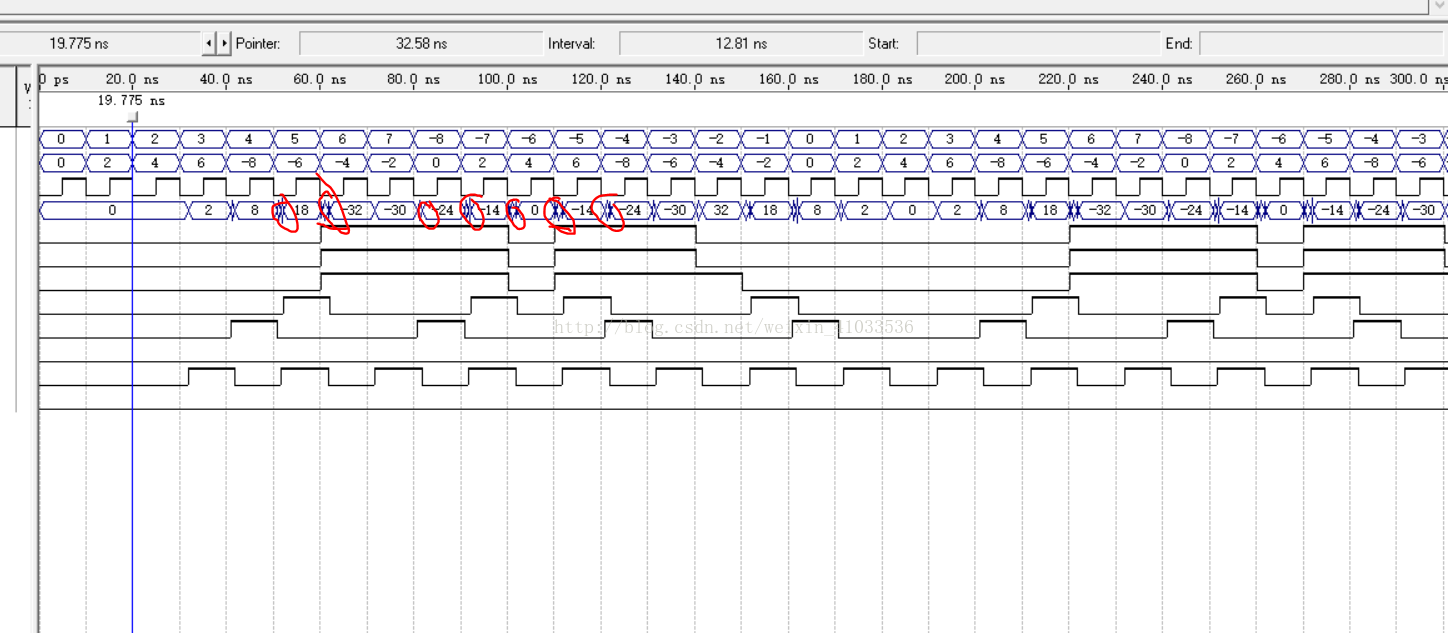

波形模擬結果如下:

8輸入-8輸出無符號乘法器

可見相較4輸入的無符號乘法器“毛刺”時間變短。

無硬體乘法器晶片的8輸入-8輸出無符號乘法器

可見無硬體乘法器的無符號乘法器“毛刺”時間大大變長。

4輸入-8輸出帶流水線乘法器

可見相較4輸入-8輸出無流水線乘法器,其毛刺時間相較更短,但輸出延時更長(多了一個時間週期)。

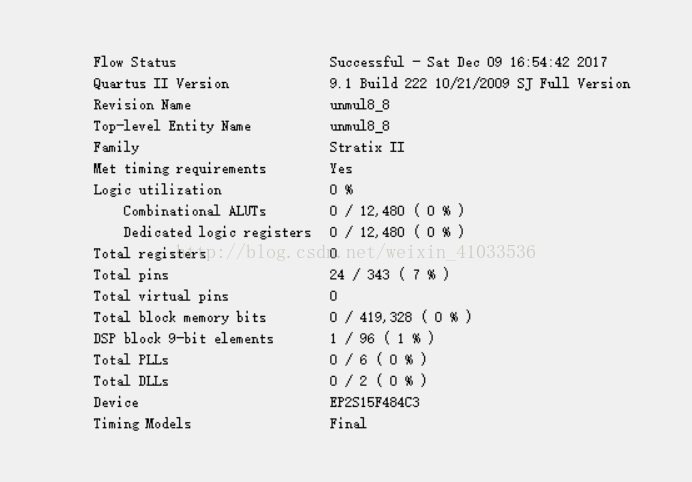

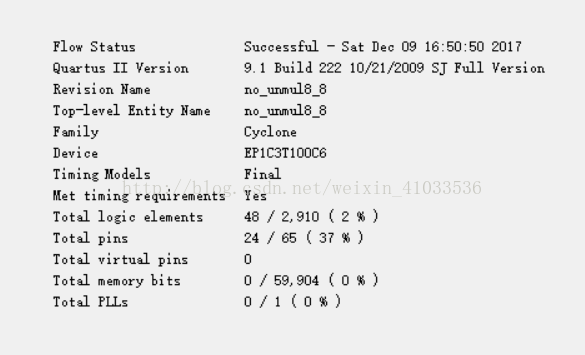

資源消耗如下:

8輸入-8輸出無符號乘法器

無硬體乘法器晶片的8輸入-8輸出無符號乘法器

可見無硬體乘法器晶片的無符號乘法器硬體資源消耗非常巨大。

9. (1)設計一個最簡單的計數器,只有一個CLK輸入和一個OVerflow輸出,當計數到最大值的時鐘週期CLK輸出1

(2)設計複雜的計數器,和本例相似,帶有多種訊號,其中同步清零CLR的優先順序最高,使能EN次之,LOAD最低。

實驗分析:(1)中所要求的即不再考慮清零訊號、使能訊號、置數訊號,當計數器還沒到達最大值時,每個時間週期內計數加1,當達到計數最大值時,輸出訊號置1、計數置0即可;(2)即改變三個額外輸入訊號的優先順序,只要CLR為1則執行清零,否則判斷EN是否為1,為1則執行最基本的技術功能,否則執行置數功能。

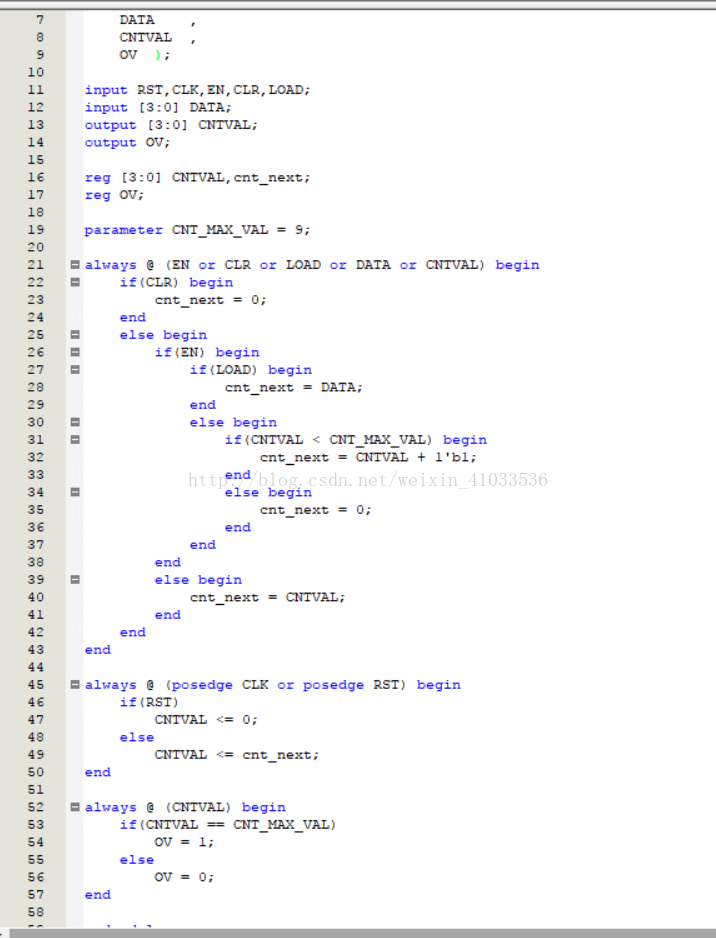

實驗程式碼設計:

只有CLK和Overflow訊號的簡單計數器

改變三種訊號優先順序的計數器

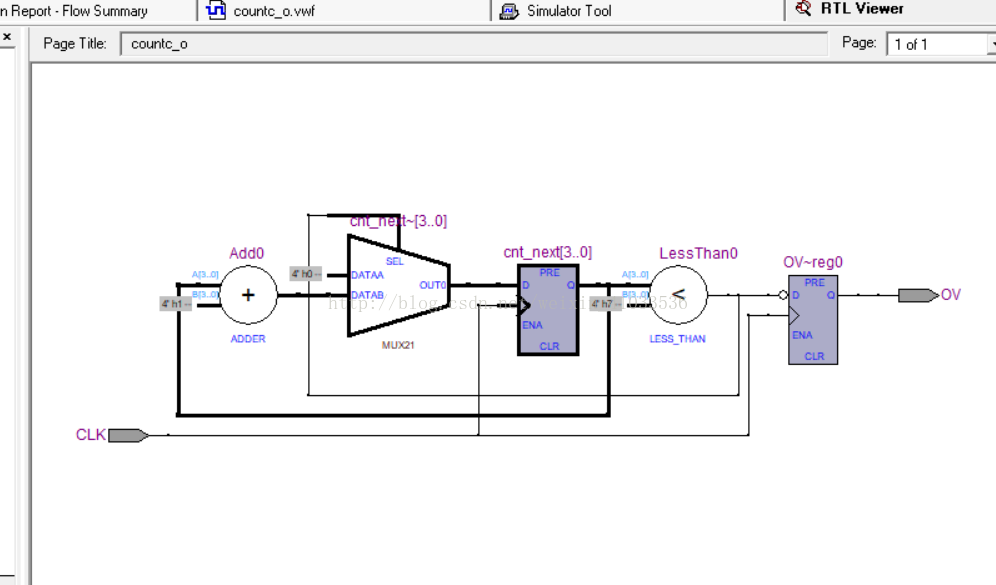

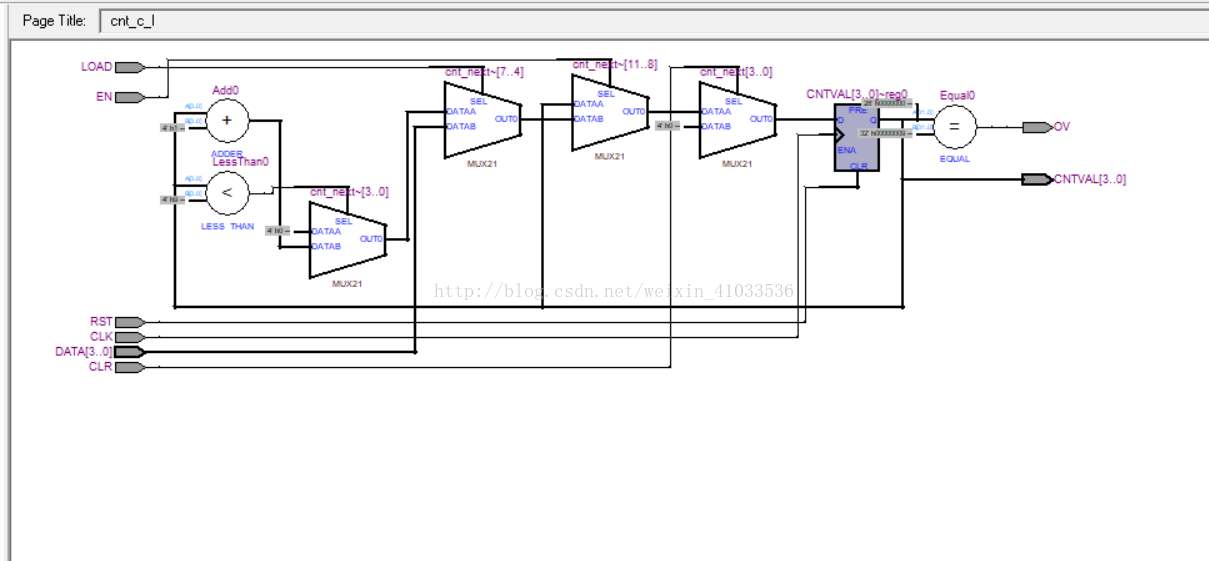

RTL檢視如下:

只有CLK和Overflow訊號的簡單計數器

改變三種訊號優先順序的計數器

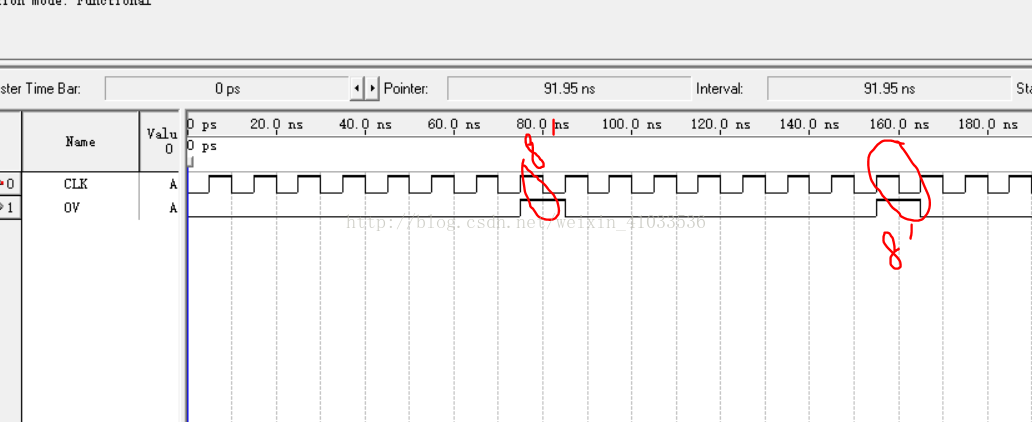

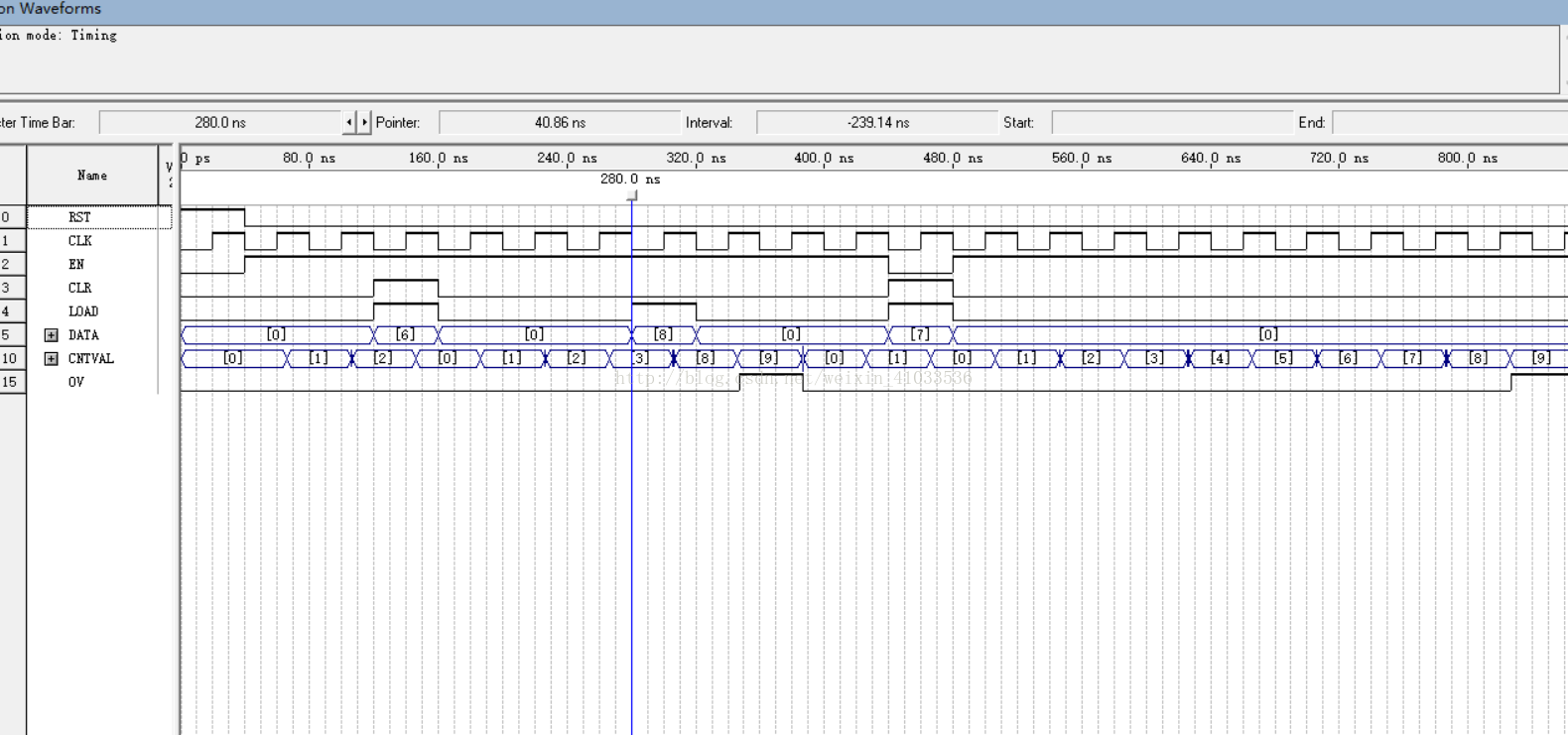

波形模擬結果如下:

只有CLK和Overflow訊號的簡單計數器

改變三種訊號優先順序的計數器

10. 設計一個用於識別2進位制序列“1011”的狀態機

(1) 基本要求:電路每個時鐘週期輸入1位元資料,當捕獲到1011的時鐘週期,電路輸出1,否則輸出0;使用序列101011010作為輸出的測試序列;

(2) 擴充套件要求:給你的電路新增輸入使能埠,只有輸入使能EN為1的時鐘週期,才從輸入的資料埠向內部獲取1位元序列資料。

實驗分析:因為要捕獲的是“1011”序列,從最低位開始進行匹配,匹配成功跳轉到下一狀態匹配更高一位,只要有一位匹配錯誤就應該跳轉至狀態0重新開始。而加上使能訊號後,只有EN為1才從輸入端讀入輸入資料進行匹配。

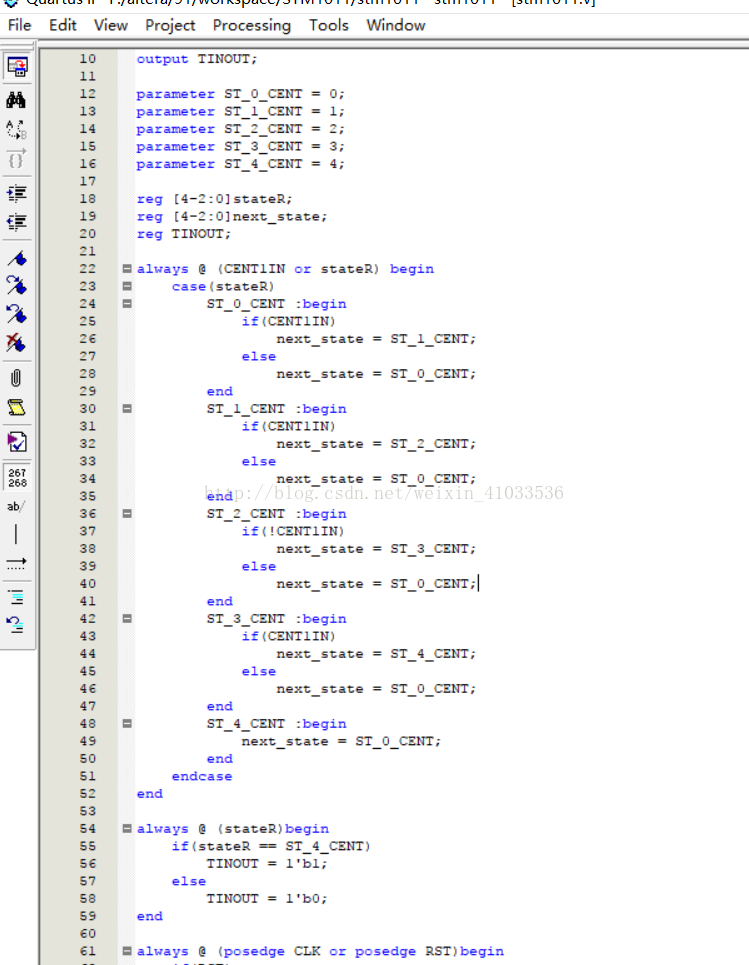

實驗程式碼設計如下:

基本要求的狀態機

帶使能訊號的狀態機

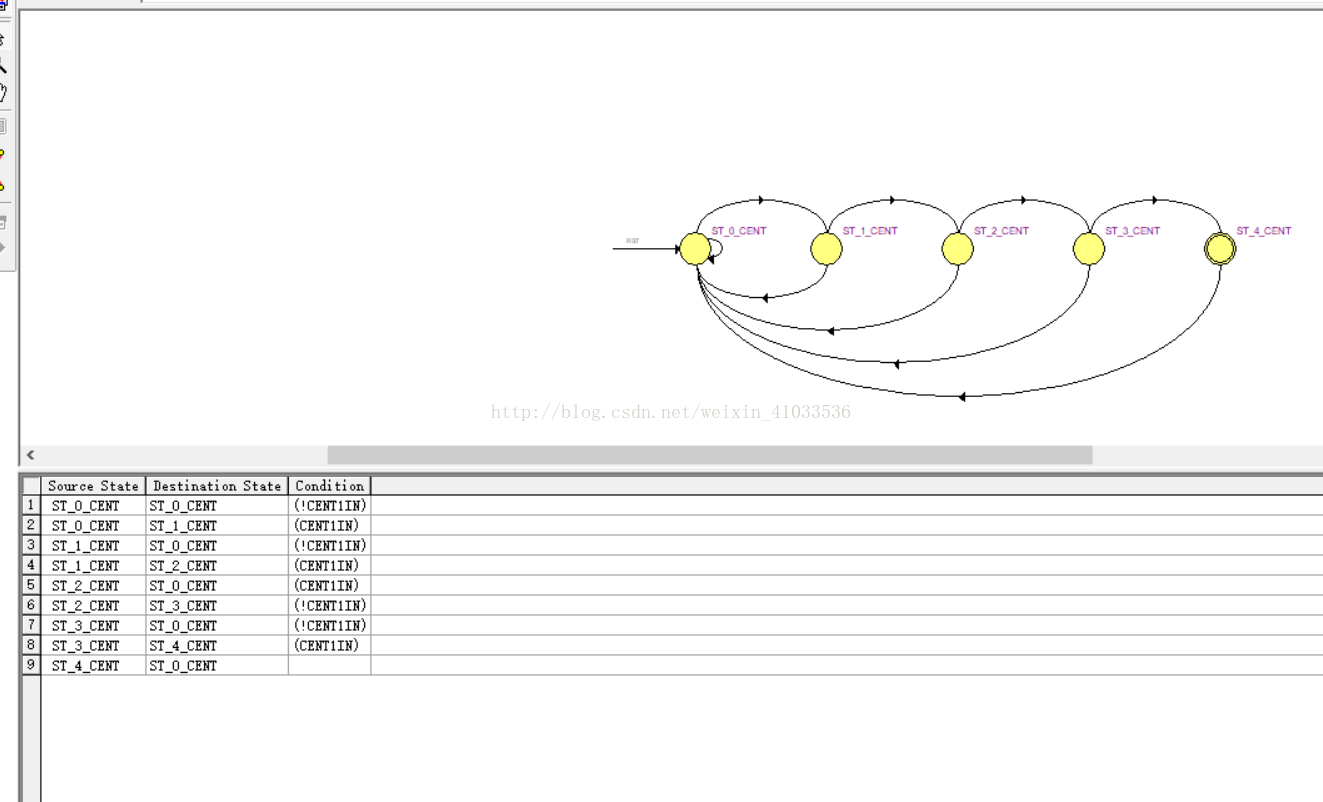

狀態轉移圖及表示式如下:

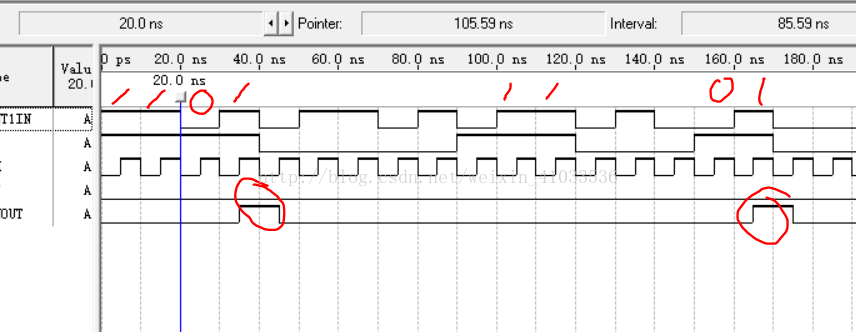

波形模擬結果如下:

基本要求的狀態機

帶使能訊號的狀態機

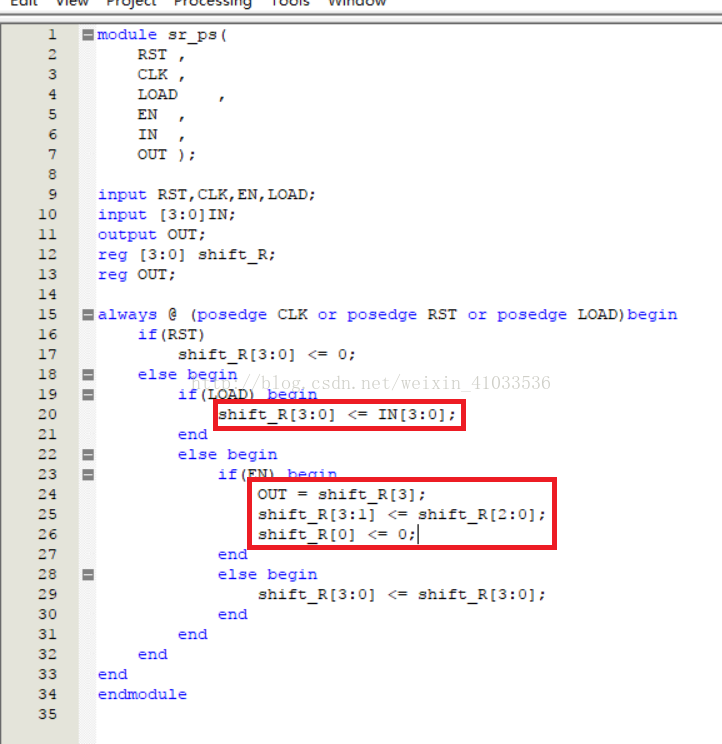

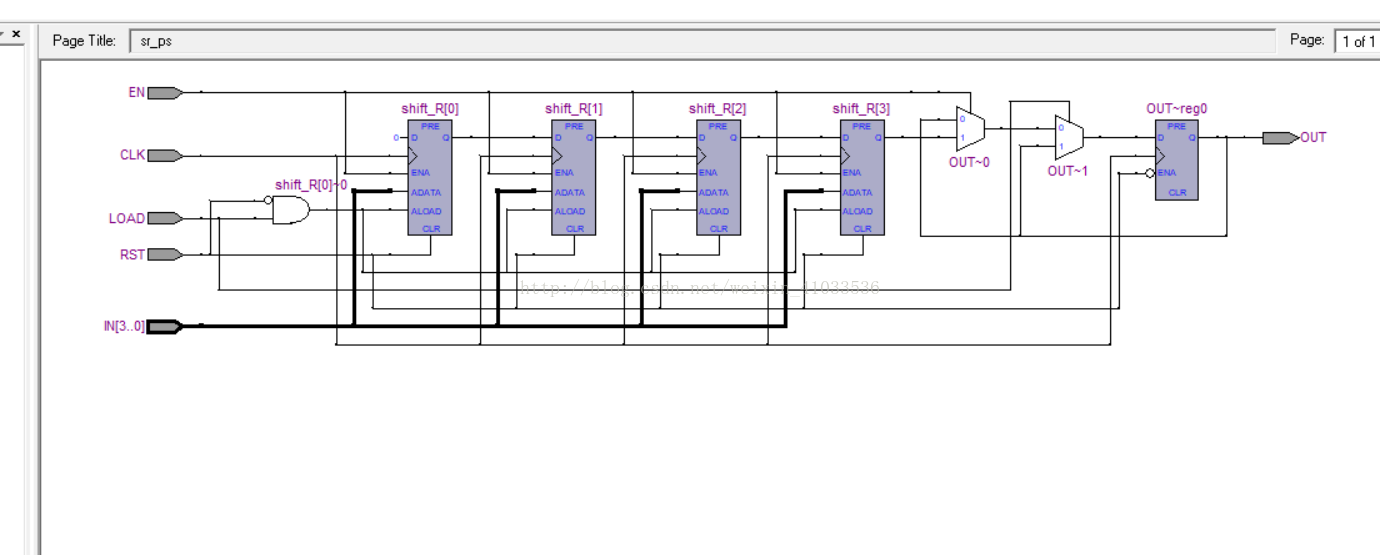

11. 設計一個如本節“電路描述”部分的“帶載入使能和移位使能的併入串出”的移位暫存器,電路的RTL結構圖如“電路描述”部分的RTL結構圖所示。

實驗分析:所謂“串入並出”的移位暫存器,及輸入一個1位輸入訊號,移位暫存器將這個一位資料存入第0位,並將原本的後3位一同前移1位,最後從高到低並行輸出四位資料。而“併入串出”的移位暫存器是指,輸入一個4位輸入訊號,存入移位暫存器,若移位使能有效,則將最高位輸出,移位暫存器後三3同時前移1位,最低位存入0;若載入時能有效,則從輸入端重新讀入4位資料。

實驗程式碼設計如下:

RTL檢視如下:

波形模擬結果如下:

實驗小結:

本次實驗共分為11個小的實驗,通過Verilog程式碼模擬了各種邏輯組合電路的基本原理。通過例子實驗和自主進行的實驗可以發現,任何一個複雜的組合電路都可以拆分成許多簡單的基本電路,通過熟練這些基本電路的Verilog程式碼編寫,並在每次實驗前都先對要完成的專案進行拆分與簡化,重視RTL檢視,就可以實現各類大型專案的編寫。

同時,在實驗過程中自己也檢驗了對Verilog程式碼的使用熟練度與理解,如[3:0]即宣告一個最高位為第三位最低位為第零位的變數、if...else語句最好使用begin...end括起來,以及一些其他的程式碼規範。這些都對之後的開發模擬工作有極大的提示幫助。