Rockchi之RK3288解決MIPI屏黑屏問題

Rockchi之RK3288解決MIPI屏黑屏問題

繼上一次解決液晶屏出現花屏現象之後,在公司4臺測試機上測試可用,但不久便傳來工廠測試時液晶屏出現黑屏現象,緊接著上次任務,我又繼續了無盡頭的除錯,同樣,拿到液晶屏,開啟液晶屏的配置檔案dts檔案.

開啟檢視引數,想起上次修改的是rockchip,dsi_hs_clk這個引數,上次改的值是450,然後在不斷開機的時候就會出現黑屏現象或者開機動畫不正常現象,但是當我把這個引數改大,液晶屏經過連續的開關機並不會出現黑屏或者開機動畫不正常現象,但是致命的就是液晶屏左側會出現一條豎線,繼續增大rockchip,dsi_hs_clk這個值,就會出現花屏,然後我的第一想法就是改一個剛好合適的值,讓它既不會黑屏又不會有水紋,但是最後結果我錯了.

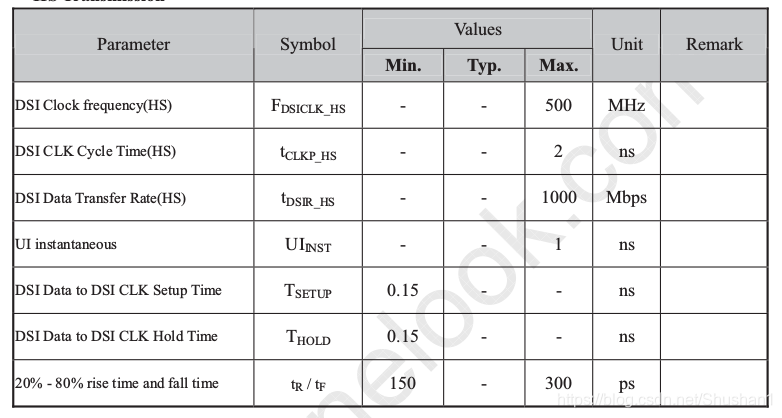

檢視lcd屏的資料手冊,看到rockchip,dsi_hs_clk的值最大為500,但是dts上rockchip,dsi_hs_clk

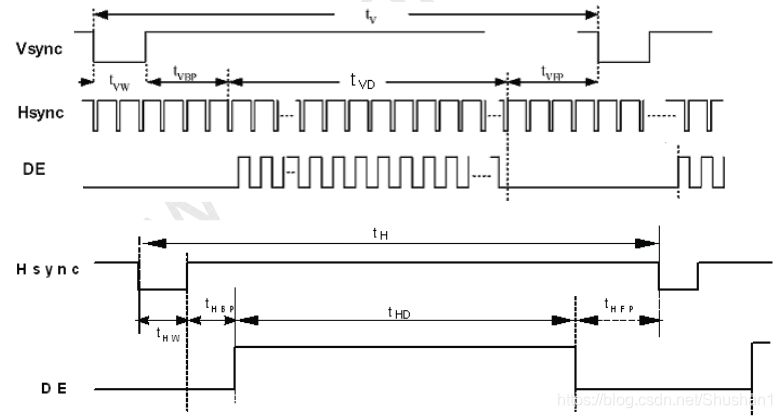

由圖中可以看到,Hsync水平同步訊號和Vsync垂直同步訊號的時序,其中tvw和thw為無效時間,tvbp和thbp為等待時間tvd為垂直畫素,thd為水平同步訊號,tvfp和thfp為結束時間,根據這張圖我去調節dts裡的引數,但是這些引數又有限制,LCD的資料手冊上寫了很清楚.

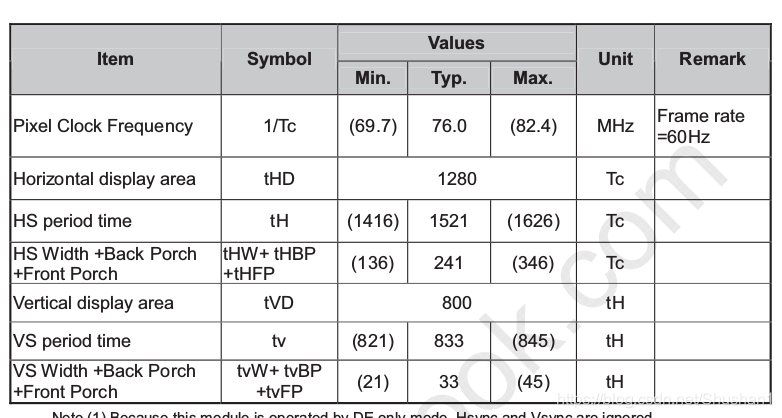

tHW+tHBP+tHFP的典型值為241,tvW+tvBP+tvFP的典型值為33,根據這個,調節引數

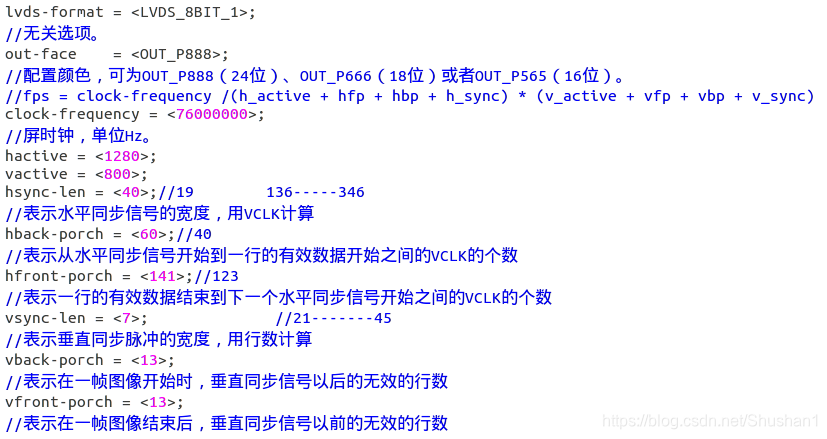

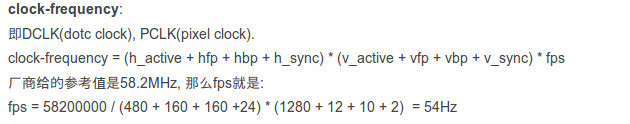

但是最後發現,無論我怎麼調節行場訊號都不能解決問題,甚至對液晶屏顯示都沒有一點影響,很沮喪,就這樣調節clock-frequency畫素時鐘和各行場訊號,雖然有時候測試十多二十次正常,但是經不起次數更多的測試,這也花費了我不少時間,但是有一天我看到了網友們的除錯經驗,我發現我之前的想法錯了,不多說上圖

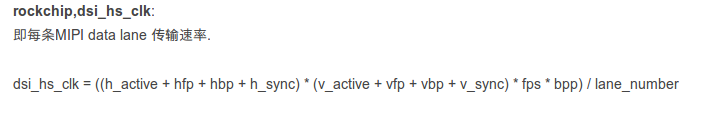

其中bpp為畫素位寬,在本LCD屏中,設定的是24位畫素

我之前對這個rockchip,dsi_hs_clk引數很模糊,不知到他到底怎麼來的,直到今天明白,他是由行場訊號、重新整理率、畫素位寬以及資料data線的數量有關,只有rockchip,dsi_hs_clk和重新整理率兩者匹配液晶屏才能正常顯示,然而液晶屏的重新整理率又是

根據計算,LCD資料手冊給出的典型值算下來的fps重新整理率正好為60,雖然是59.9多,但是可以認為是60,但是這個60在android系統中是最大的重新整理率了,所以我就把這些引數都設定成典型值,根據上面rockchip,dsi_hs_clk公式可以計算出來每條MIPI data lane傳輸速率為456.

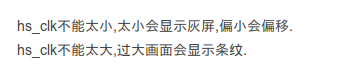

填入456後,測試30次正常,很開心很激動,繼續測試到45次開機動畫不正常,卡了一下,瞬間奔潰,但是還是很開心的,因為找到了突破點,之後我把引數改成450,發現液晶屏顯示發生偏移,改成460發現液晶屏顯示出現波紋,簡直就是完美,然後我從560往下降,一個個測試,最終當引數改為458的時候,液晶屏測試100次無誤,這也就符合了網友說的

好了,液晶屏一切正常了,是不是要手工領盒飯了呢,並不能,因為作為一個嚴謹好學的孩子,是不能停止腳步的,根據公式我算了一下資料手冊上的DSI Clock frequency(HS)引數,當畫素時鐘clock-frequency最大為82.4MHz其他行場訊號最小HW+tHBP+tHFP的值為136,tvW+tvBP+tvFP的為21時,重新整理率fps為70.8多,最終算下來rockchip,dsi_hs_clk的值為494多,和資料手冊上的MAX值為500相符,所以資料手冊上的引數是正確的。

除此之外對公式進行解析:

dsi_hs_clk = ((h_active + hfp + hbp + h_sync) * (v_active + vfp + vbp + v_sync) * fps * bpp) / lane_number

一幀畫面需要的資料量為(單位bit):

FRAME_BIT = (螢幕有效顯示寬度+hsync+hfp+hbp) x ( 螢幕有效顯示高度+vsync+vfp+vbp) x(RGB顯示資料寬度24)

一秒鐘內需要傳輸的資料量為(單位bps):

FRAME_BIT x fps(幀率)。

那為何要除以lane_num----因為mipi通訊協議中,一個CLOCK幾個lane是可以同時傳輸資料的.

但是有些還要再除2,因為根據mipi通訊協議,CLK_N、CLK_P這兩根時鐘線的上升沿/下降沿可以獲取到資料,但是我們這個mipi屏好像沒有上升下降都獲取資料,所以暫且不除2。

因此我們可以得出如下結論:

- 在相同的時鐘頻率下,lane數越多,則單位時間內可以傳輸的資料越多。若顯示幀率固定不變,則可以支援的更大的解析度;而解析度固定不變的情況下,則我們可以考慮支援更高的幀率顯示。

- 在lane數固定的情況下,提高傳輸的時鐘頻率,則單位時間內也可以傳輸更多的顯示資料。進而我們可以考慮是提高幀率還是提高解析度,或兩者做出平衡。

那麼我們是否可以任意無限制的提高mipi的傳輸時鐘頻率及lane數目呢?mipi通訊協議對此進行了限制,一組CLOCK最高只能支援4組lane,一組lane的傳輸速度最高只能支援到1 Gbps。也就是說一組CLOCK最高只能支援到4 Gbps速度傳輸。

此時就引出了一個新問題:4Gbps速度傳輸,是滿足不了現在市場上推出的4K電視的頻寬要求的,怎麼辦?答案是使用8組lane,使用兩組clock來傳輸。