晶振旁的電阻(並聯與串聯)和電容的作用

無源晶振再使用時可以見到如下幾種形式,具體如下:

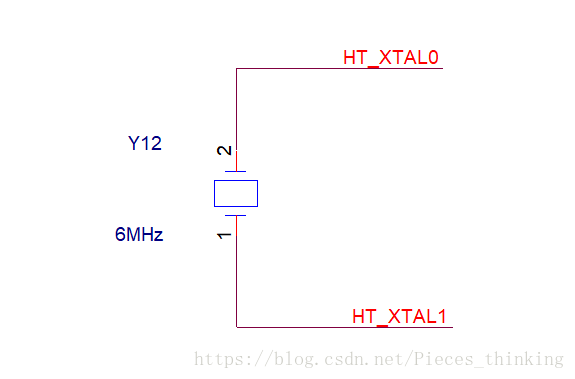

1.

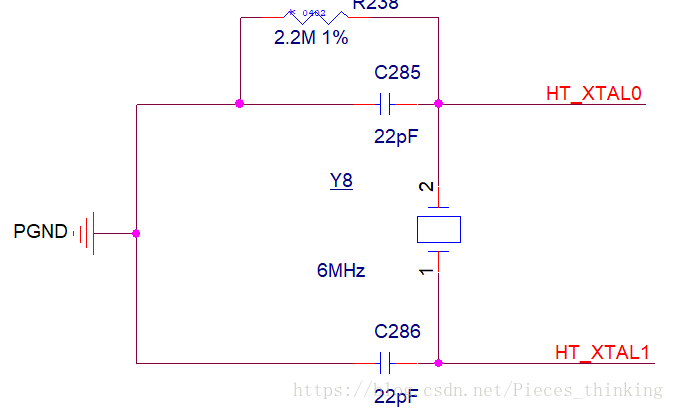

2.

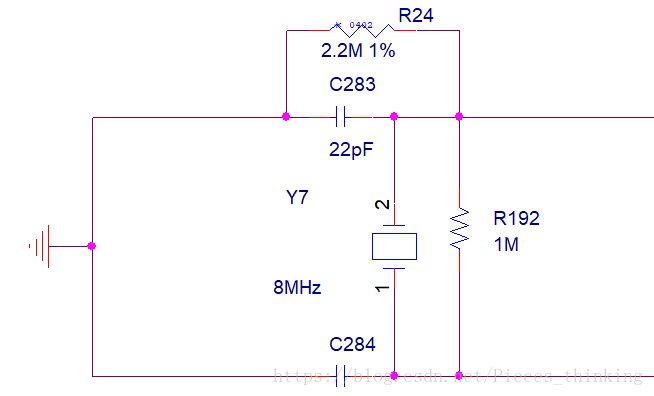

3.

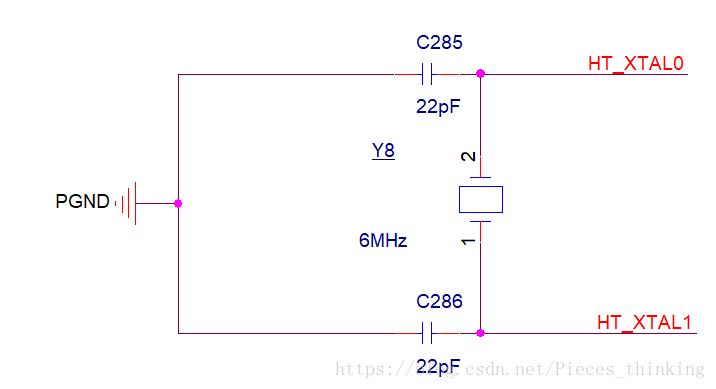

各種形式基本都有,最常見的就是下圖中的格式:

4.

首先按照1.電容的有無?2.並聯電阻和串聯電阻的作用?兩部分進行說明

一、電容的作用

1、晶體旁邊不加電容是可以的。

2、晶體旁邊加的這個電容被我們稱之為晶體負載電容。晶體的諧振頻率為Fr,加了電容的諧振頻率為有載諧振頻率FL。晶體諧振頻率Fr與晶體有載諧振頻率FL的關係為:

FL=Fr + Ts*CL

式中Ts為晶體的牽引量,單位為ppm/pF。CL為晶體的負載電容,即晶體旁邊加的那個電容,單位為pF。

3、如果電路不加負載電容,則電路會工作在晶體諧振頻率上。所以電路中是可以不加負載電容的。

4、晶體發生諧振後,會呈現為純電阻,即諧振阻抗。在有載諧振中,諧振電阻一般會與負載電容呈反比例關係。也就是說負載電容越小,電路的諧振阻抗越高,就越不容易起振,輸出波形幅度就越小。

5、而事實上,電路直接工作在晶體諧振頻率的狀態是非常理想化的。我們一般的電路都或多或少的有一些雜散電容。當電路振盪時,這些雜散電容便被視為晶體的負載電容進行工作。由於這些雜散電容一般都很小,且不穩定,這就造成晶體振盪頻率不穩定,且諧振阻抗增高,“可能工作不穩定,頻率不準確”。當然,如果你的振盪電路較為簡單,而且PCB走線設計的又十分合理,PCB上的雜散電容小到可以忽略不計且十分穩定,那麼就可以不加電容。

6、那麼在設計電路時該如何加這個負載電容呢?首先你要明白FL這個有載諧振頻率就是你的電路所要的頻率。電路中的雜散電容為Cy的話,根據上面的公式,你所設計的電路頻率應為:

FL = Fr + Ts*(Cy+CL)

設計時,你的負載電容CL可以用可調電容替代,調整CL值直到電路工作在你所要的頻率上。一般時候這個負載電容CL值不要太小,上面說過電容太小,諧振阻抗會變高,不利於起振且輸出幅度小。所以這個電容值一般選取在10至30pF之間。此時由於負載電容CL值遠遠大於雜散電容Cy值,因此對雜散電容的不穩定性可以忽略不計。所以加了負載電容的電路會更穩定,頻率更準確。

一、並聯或者串聯電阻的作用

一份電路在其輸出端串接了一個22K的電阻,在其輸出端和輸入端之間接了一個10M的電阻,這是由於連線晶振的晶片端內部是一個線性運算放大器,將輸入進行反向180度輸出,晶振處的負載電容電阻組成的網路提供另外180度的相移,整個環路的相移360度,滿足振盪的相位條件,同時還要求閉環增益大於等於1,晶體才正常工作。

晶振輸入輸出連線的電阻作用是產生負反饋,保證放大器工作在高增益的線性區,一般在M歐級,輸出端的電阻與負載電容組成網路,提供180度相移,同時起到限流的作用,防止反向器輸出對晶振過驅動,損壞晶振。

和晶振串聯的電阻常用來預防晶振被過分驅動。晶振過分驅動的後果是將逐漸損耗減少晶振的接觸電鍍,這將引起頻率的上升,並導致晶振的早期失效,又可以講drive level調整用。用來調整drive level和發振餘裕度。

Xin和Xout的內部一般是一個施密特反相器,反相器是不能驅動晶體震盪的.因此,在反相器的兩端並聯一個電阻,由電阻完成將輸出的訊號反向 180度反饋到輸入端形成負反饋,構成負反饋放大電路.晶體並在電阻上,電阻與晶體的等效阻抗是並聯關係,自己想一下是電阻大還是電阻小對晶體的阻抗影響小大?

電阻的作用是將電路內部的反向器加一個反饋迴路,形成放大器,當晶體並在其中會使反饋迴路的交流等效按照晶體頻率諧振,由於晶體的Q值非常高,因此電阻在很大的範圍變化都不會影響輸出頻率。過去,曾經試驗此電路的穩定性時,試過從100K~20M都可以正常啟振,但會影響脈寬比的。

晶體的Q值非常高, Q值是什麼意思呢? 晶體的串聯等效阻抗是 Ze = Re + jXe, Re<< |jXe|, 晶體一般等效於一個Q很高很高的電感,相當於電感的導線電阻很小很小。Q一般達到10^-4量級。

避免訊號太強打壞晶體的。電阻一般比較大,一般是幾百K。

串進去的電阻是用來限制振盪幅度的,並進去的兩顆電容根據LZ的晶振為幾十MHZ一般是在20~30P左右,主要用與微調頻率和波形,並影響幅度,並進去的電阻就要看 IC spec了,有的是用來反饋的,有的是為過EMI的對策

可是轉化為 並聯等效阻抗後,Re越小,Rp就越大,這是有現成的公式的。晶體的等效Rp很大很大。外面並的電阻是併到這個Rp上的,於是,降低了Rp值 —–> 增大了Re —–> 降低了Q

精確的分析還可以知道,對頻率也會有很小很小的影響。

總結

並聯電阻的作用:

1.降低晶體的Q值,Q值降低後晶體起振比較容易

2.抑制EMI,EMI不過時,可減小阻值

3.提供直流工作點

4.使閘電路工作於線性區

串聯電阻的作用:

1.降低晶體的激勵功率,防止損壞。

2.限制振盪幅度。

例項:

已成型的一款產品因更換陶瓷晶振廠家後,陶振不容易起振,經過測試,將晶振並聯一個1M電阻,晶振能夠正常起振。

原因:這個電阻是為了使本來為邏輯反相器的器件工作線上性區, 以獲得增益, 在飽和區是沒有增益的, 而沒有增益是無法振盪的. 如果用晶片中的反相器來作振盪, 必須外接這個電阻, 對於CMOS而言可以是1M以上, 對於TTL則比較複雜, 視不同型別(S,LS…)而定. 如果是晶片指定的晶振引腳, 如在某些微處理器中, 常常可以不加, 因為晶片內部已經制作了, 要仔細閱讀DATA SHEET的有關說明.

附:電阻的作用是將電路內部的反向器加一個反饋迴路,形成放大器,當晶體並在其中會使反饋迴路的交流等效按照晶體頻率諧振,由於晶體的Q值非常高,因此電阻在很大的範圍變化都不會影響輸出頻率。過去,曾經試驗此電路的穩定性時,試過從100K~20M都可以正常啟振,但會影響脈寬比的。