如何在AltiumDesigner中實現兩片DDR等長走線

但在Altium Designer中,SOC的某一ADDR

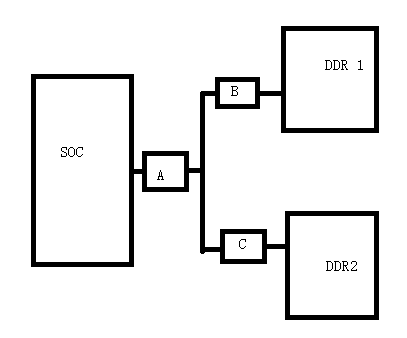

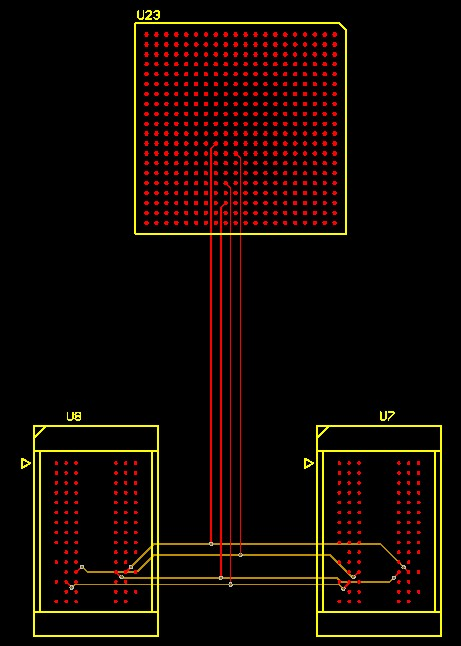

下面以一個專案中DRAM_A0 ~ A3四根訊號線的等長設計為例,介紹在Altium Designer中實現DDRII SDRAM的等長佈線。U23為CPU,U7和U8為兩片DDRII SDRAM。DRAM_A0 ~ A3為低四位地址訊號。

下面以一個專案中DRAM_A0 ~ A3四根訊號線的等長設計為例,介紹在Altium Designer中實現DDR

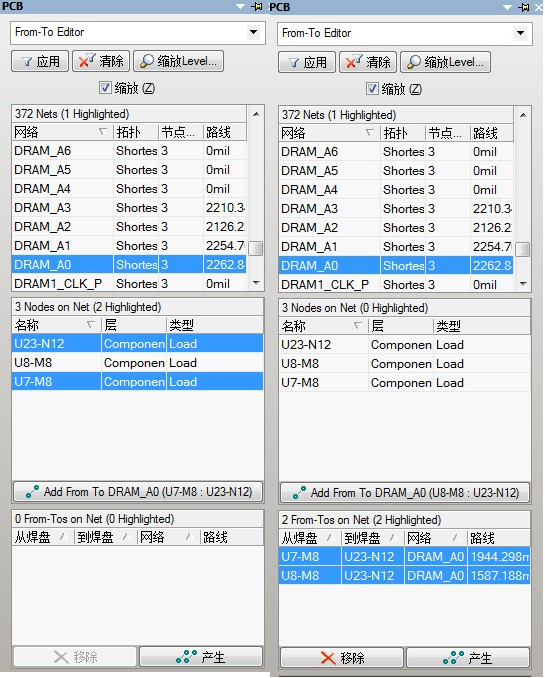

一,在From-To Editor中定義DRAM_A0 ~ A3的From To。

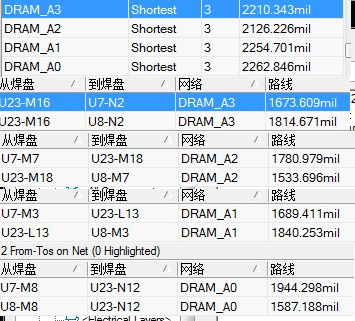

在From-To Editor中,選擇DRAM_A0,則可以看到DRAM_A0這個網路上有三個節點。分別是U23-N12, U7-8和U8-8。在節點列表裡選中U23-N12和U7-M8,然後點選按鈕 Add From To DRAM_A0(U7-M8:U23-N12),生成DRAM_A0的第一個From-To。然後按同樣的方法生成第二個From To,U23-N12和U8-M8。(如面兩個圖所示)

後面就按照同樣的步驟,依次生成DRAM_A1~A3的From To。

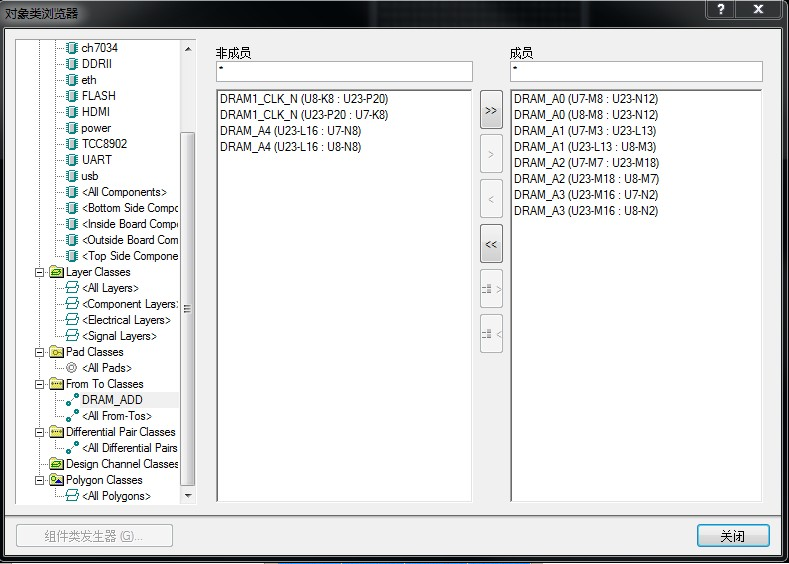

一,新增From To類DRAM_ADD

在From To Classes中,新增一個新的名字為DRAM_ADD的類,然後將DRAM_A0 ~ A3所有的From To都新增到這個類裡。如下圖所示:

三,找出最長的走線,作為等長佈線的基準線。首先列出DRAM_A0 ~ A3各net的長度和所有From To的長度。找到最長的From

To的長度 - 1944mil(為了方便計算,取整數),以及對應的net - DRAM_A0 - 的長度2263mil和另外一個From

To的長度 1587mil。最後根據這三個長度確定出ADDRESS net的等長佈線的基準。

L = 2263 + (1944 - 1587) = 2620 mil。

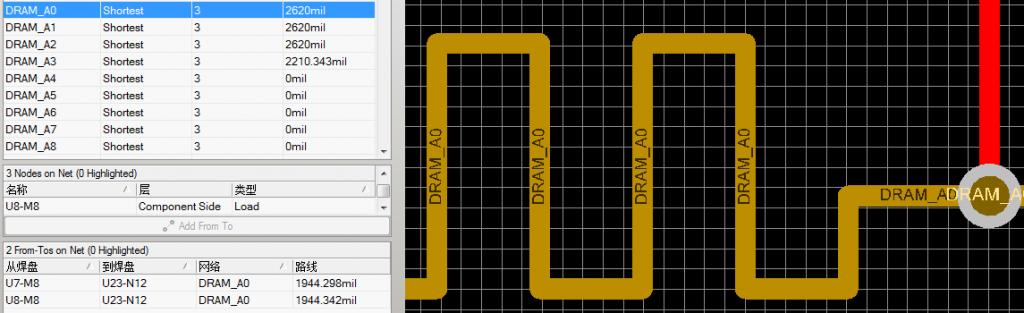

四,使用網路等長調節命令,在DRAM_A0的U8-M8 到U23-N12的From To(兩個From To的較短者)上,調整DRAM_A0的net長度為2620mil

五,DRAM_A1 ~ A3 的net長度調整

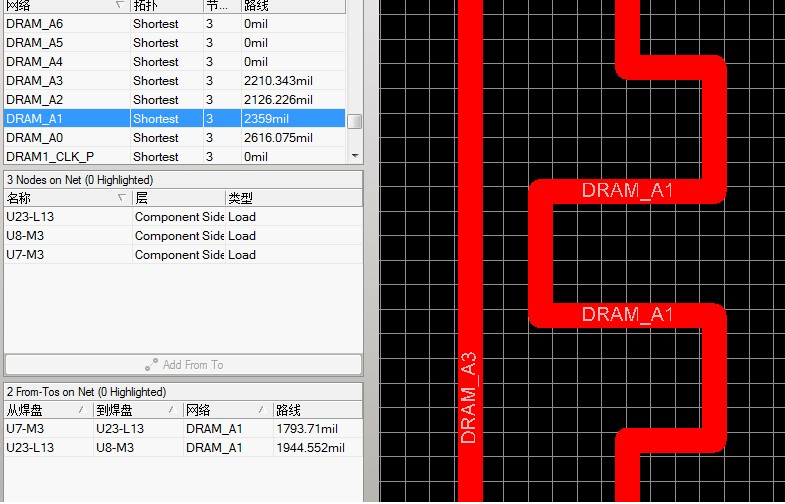

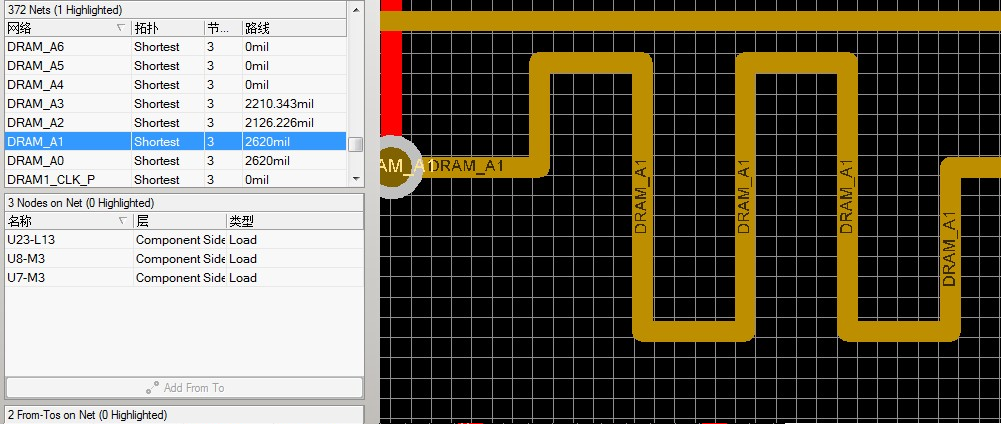

DRAM_A1的兩個From To的長度分別是1840mil和1689mil,net長度為2255mil。首先在DRAM_A1的公共部分(A)上,調整net長度為2359mil(2255 + 1944 – 1840)。 然後在較短的From To(1689mil)上,調整net長度為2510mil {[1944 -(1944 – 1840 + 1689)] + 2359 }

按照同樣的方法完成DRAM_A2 ~ A3的長度調整。

六:最後結果每個From To的長度都約等於1944mil,實現了等長佈線。(略微存在的差異是由於取整實際的走線長度造成的)