Vivado+FPGA學習之第一次上電

背景:我本人沒有怎麼接觸過FPGA,但是這次一上來就被要求做FPGA的工作,實在是讓我感到無從下手,前前後後忙活了好幾天才第一次上電成功,所以把整個經過整理了一下,以便方面後來人。

開發平臺:Vivado 2015.2

FPGA :Xilinx Virtex-7系列晶片

一上來就碰到這種高階FPGA晶片,沒有什麼資料,至於下面的FPGA的板子也是自制的(上面沒有按鈕,沒有數碼管,只有2個led燈),所以感到無從下手。那麼針對這種情況怎麼辦呢?下面將全面介紹一下。

//************************************************************//

1.時鐘:

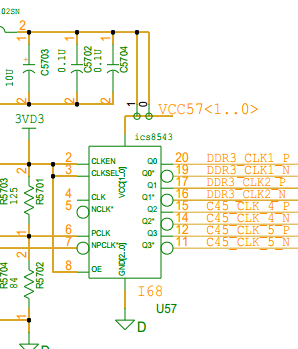

從圖中可以看出,使用了ICS8543晶片,檢視該晶片的datasheet,可以知道該晶片的輸出為4對差分口,IO標準為LVDS,並且通過檢視原理圖可以知道Q3和Q3*是作為FPGA工作的時鐘,此時記下在FPGA中的引腳。

//************************************************************//

2.建立工程:這一步網上有很多教程,我在這裡就略過了

//************************************************************//

3.呼叫Clocking wizard:

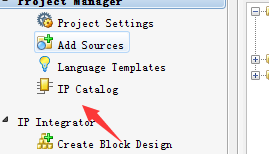

選擇IP Catalog

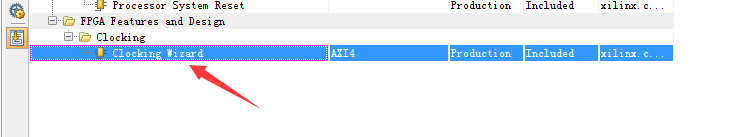

雙擊Clocking Wizard

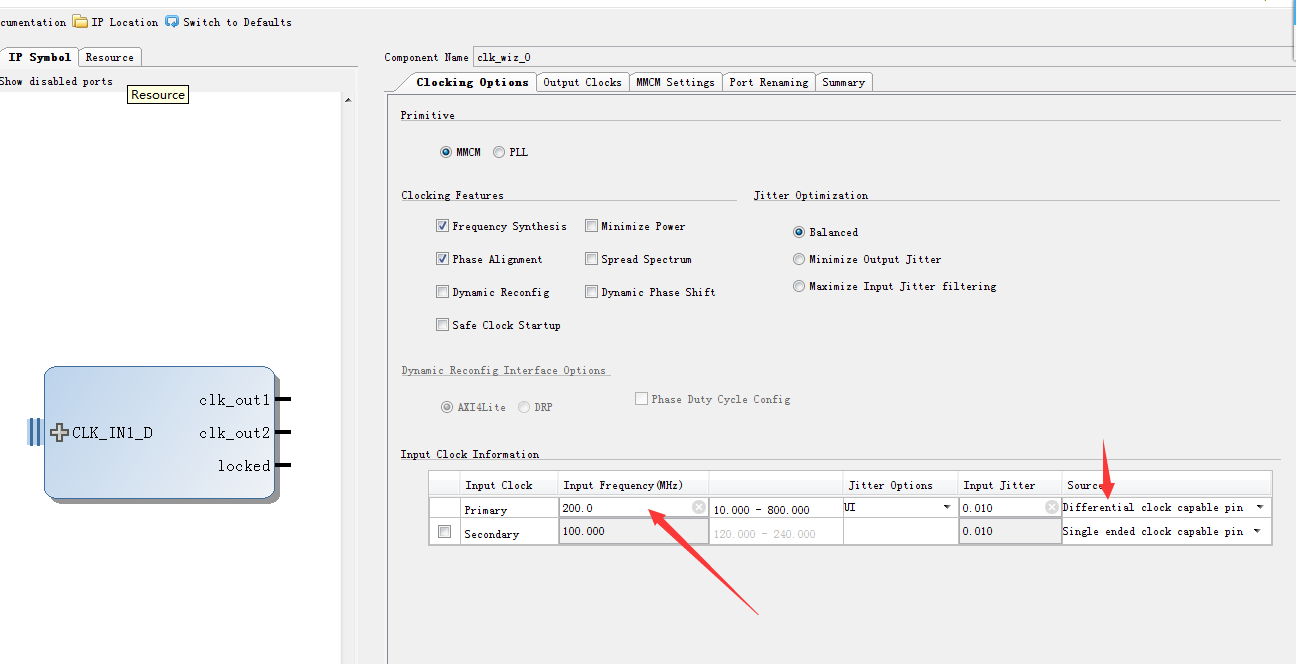

設定外部時鐘的輸入頻率,我這裡是200M的時鐘,由於時鐘使用的是差分傳輸,所以我在這裡選擇了Differential clock capable pin

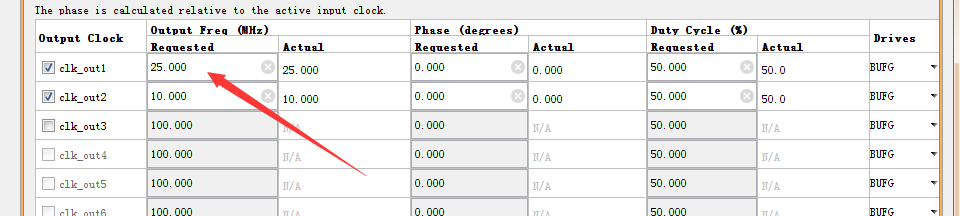

這裡是填寫輸出時鐘,根據需要選擇即可

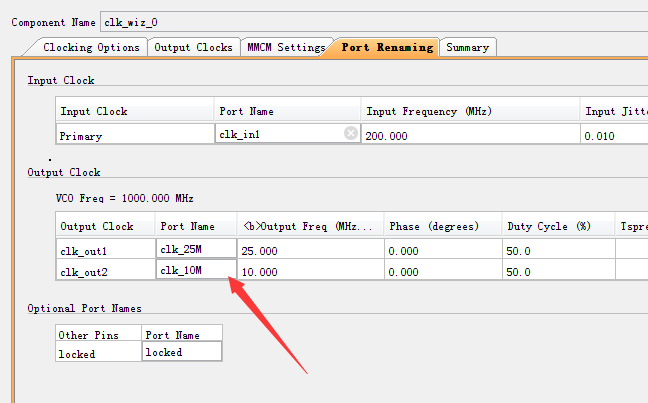

這裡是對例項化的IP core的輸出埠的重新命名,方便自己記憶

//************************************************************//

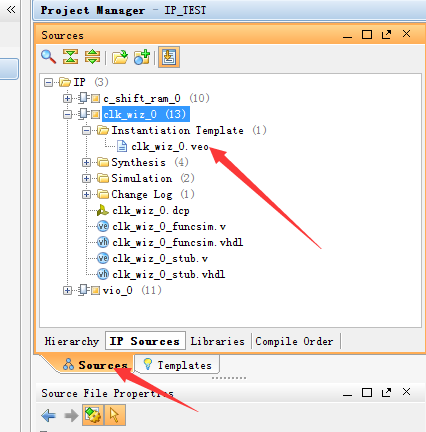

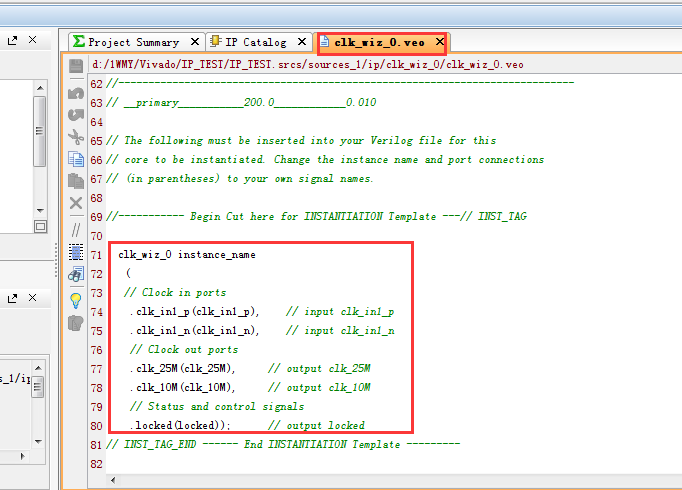

4.使用IP Core:使用Vivado提供的例化模版在v檔案中例項化

複製紅框中的內容,貼上到自己的工程檔案中

//************************************************************//

5.編寫程式碼:

在程式碼很簡單,就是利用輸出的25M時鐘,做了一個分頻,點亮一盞LED燈,由於我使用的平臺沒有外部按鍵,所以又呼叫一個VIO的IP core來做復位控制,關於VIO這個IP Core我會在以後的文章中提到。

module top(

input clk_in1_p,

input clk_in1_n,

output reg flag,

output led

);

wire clk_25M,clk_10M;

wire locked,rst_n;

reg [31:0] cnt_r;

clk_wiz_0 instance_name

(

// Clock in ports

.clk_in1_p(clk_in1_p), // input clk_in1_p

.clk_in1_n(clk_in1_n), // input clk_in1_n

// Clock out ports

.clk_25M(clk_25M), // output clk_25M

.clk_10M(clk_10M), // output clk_10M

// Status and control signals

.locked(locked)); // output locked

always @ (posedge clk_10M, negedge rst_n) begin

if(rst_n == 0)begin

cnt_r <= 0;

end

else begin

if (cnt_r == 32'b1111_1111_1111_1111_1111_1111_1111_1111) begin

cnt_r <= 0;

end

else cnt_r <= cnt_r +1;

end

end

always @ (posedge clk_10M)begin

if(cnt_r < 32'b1000_0000_0000_0000_0000_0000_0000_0000) flag <= 1;

else flag <= 0;

end

vio_0 your_instance_name (

.clk(clk_10M), // input wire clk

.probe_in0(cnt_r), // input wire [31 : 0] probe_in0

.probe_out0(rst_n), // output wire [0 : 0] probe_out0

.probe_out1(led)

);

endmodule//************************************************************//

6.配置管腳:程式碼編寫好之後,為了讓FPGA能夠工作,需要將module的輸出輸入管腳配置到實際的地方才能正常工作

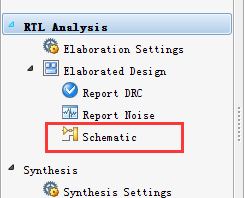

開啟Schematic

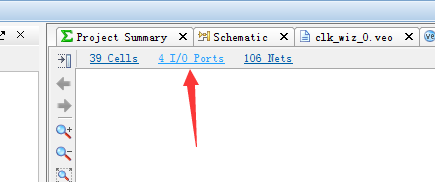

點選IO Ports

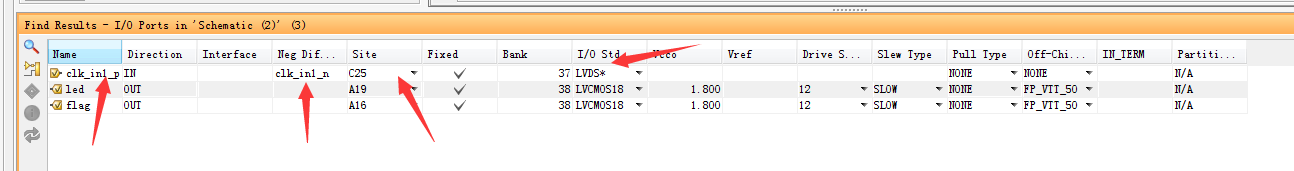

這裡就是配置管腳的地方,可以看到我將clk_in1_p配置為了C25(由於是差分管腳的關係,Vivado能夠自動識別,自動的把clk_in1_n配置為了C26),根據之前ICS8543的datasheet,IO std應該設定為LVDS。flag是我用來控制led燈的管腳,分配到了a16(不同板子位置不一樣,這個需要檢視原理圖才能知道),至於還有一個名為“led”的引腳,這個大家可以暫時忽略,這個引腳是直接被VIO控制的,在以後會講到。

7.生成bit檔案:這就是最後一步了,雖然過程看起來簡單,但是要成功的來到這一步也是很困難的,如果一切順利的話,這裡就能夠生成bit檔案了(因為沒有配置vio核,所以如果直接用我的程式碼的話,是會報錯的,需要刪除vio,並且對相應的輸入輸出進行修改)

這裡吐槽一下Vivado,我用的電腦是I7-4790+16G記憶體+SSD,從頭跑一次也要快10分鐘的時間,簡直太慢了。