Vivado Hardware Manager的使用

Hardware Manager是整合在VIVADO中的片上除錯工具,功能類似於ISE套件中的Chipscope,但功能更加強大,且使用更加方便。Hardware Manager不僅能夠管理本機或者遠端連線的FPGA資源,將生成的bit檔案下載,而且也可以對片上邏輯進行除錯,Hardware Manager將片上除錯的工作和檔案集中在該工程的目錄下,使得軟硬體除錯結合的更加緊密。

在實際的工程專案中,使用Hardware Manager進行片上除錯給我們的工作帶來了極大的便利,我也確實感受到Hardware Manager的強大,所以一直以來想寫一篇關於它的博文來與大家分享。但鑑於我能力有限,所以只能從比較淺的表面來介紹Hardware Manager及其使用,希望能拋磚引玉,激起大家摸索Hardware Manager的興趣。

一、 除錯IP核

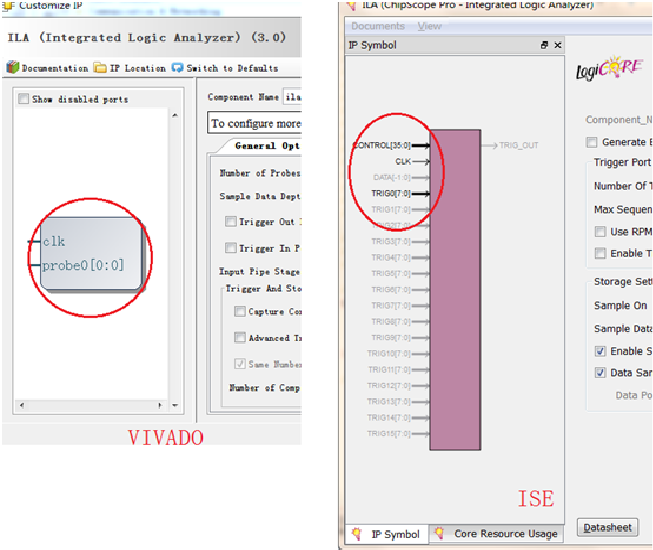

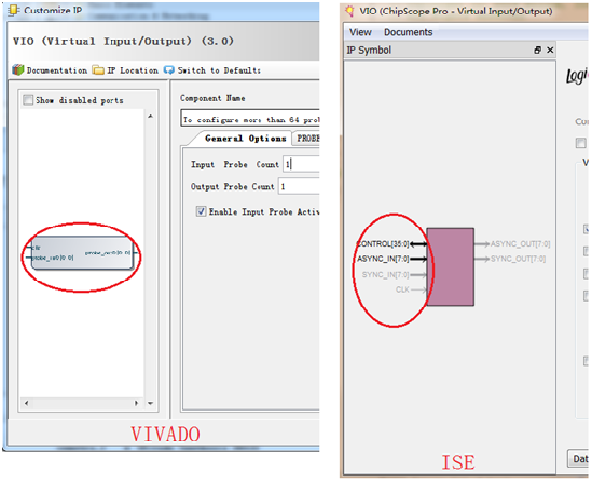

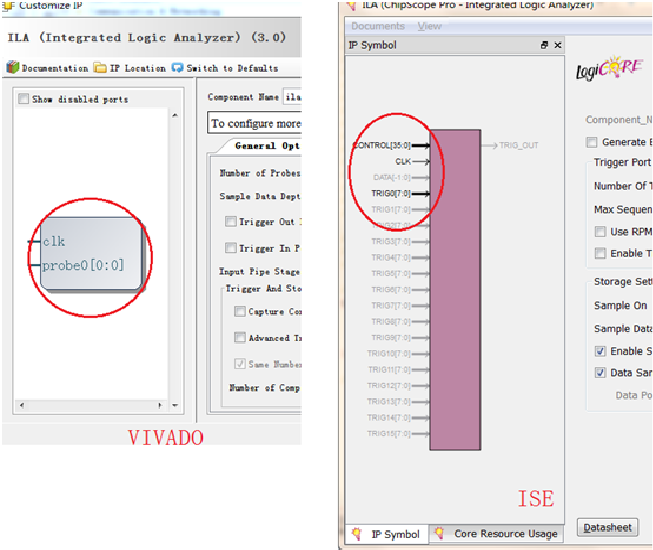

同Chipscope的除錯原理一樣,Hardware Manager也是藉助於Jtag來實現的,也需要在工程中加入除錯IP核。然而,對比ISE中和VIVADO中的除錯IP核,我們會發現,VIVADO中的除錯IP使用起來更為方便。首先,使用Chipscope時需要用到ICON、ILA或VIO來配合工作,而在Hardware Manager下進行了簡化只需要用到ILA或VIO即可,ICON不需要使用者來顯式控制。

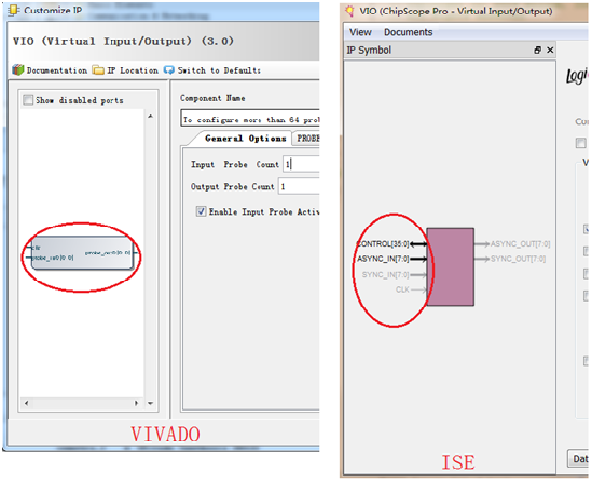

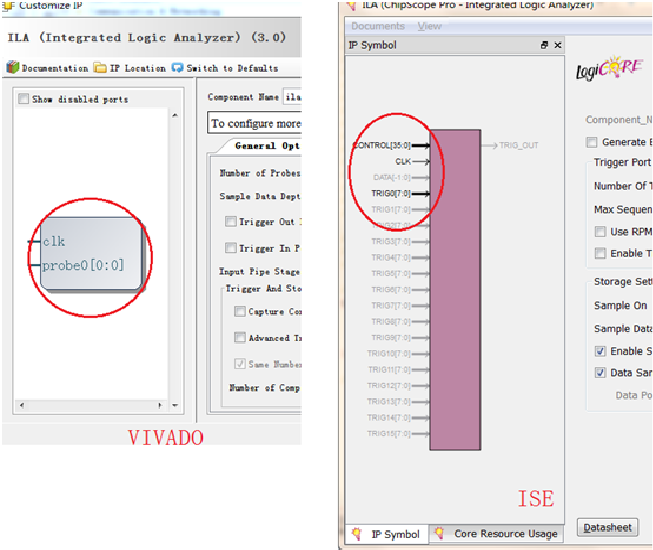

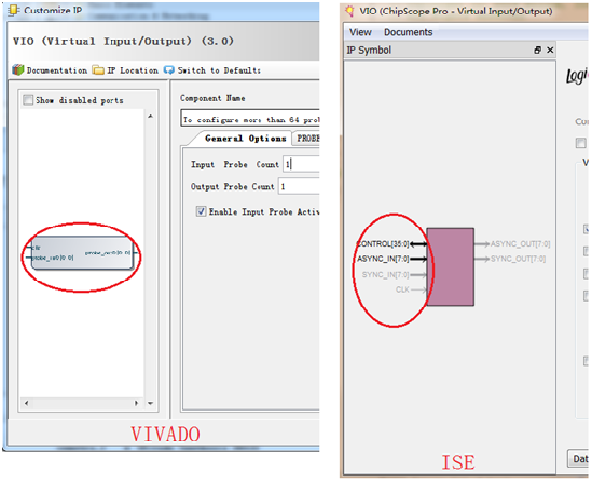

其次,如上圖是VIVADO和ISE中ILA除錯IP的對比,從引腳來看VIVADO中ILA的引腳分類更加清晰和簡潔,從配置介面上來看VIVAOD中ILA的配置也更為靈活,更便於使用者使用,而ISE中需要使用者加入較多的控制。下圖是兩者VIO除錯IP核的對比,可以發現VIVADO下的使用更為方便和靈活。VIO具有虛擬輸入輸出的功能,不僅能夠捕捉片上訊號,而且也可以往片上輸入訊號。

二、 使用方法

我們需要在工程檔案中加入除錯IP核,同Chipscope類似,Hardware Manager可以通過HDL的方法來加入除錯IP核,也可以通過網表的方法來插入除錯IP核。我個人更傾向於前者HDL加入的方法,因為這樣像使用普通IP核一樣方便,省去在網表文件中苦苦尋找網線和暫存器的工作。

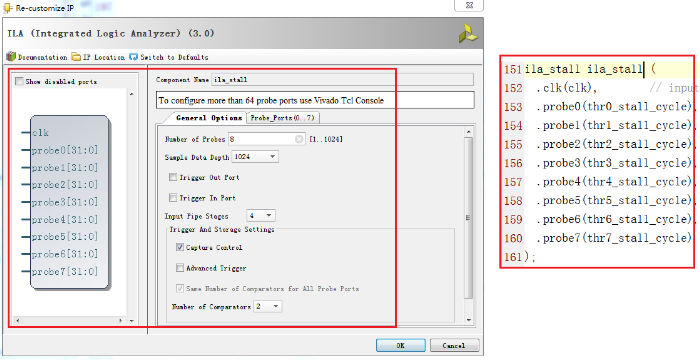

這裡以HDL加入除錯IP的方法為例來簡要介紹,首先是根據需要配置好相應的除錯IP核,如捕捉訊號的數量及寬度、是否需要觸發條件等等。然後,在程式碼中的相應位置進行例項化,連線需要捕獲的訊號或者輸入的訊號,如下圖所示。最後,重新對該工程進行綜合實現。

在工程中可以加入多個不同的除錯IP核,以我個人的經驗來看,只要加入除錯IP捕捉的訊號不是太多,整個工程的時序問題不會受到影響。當然,這也要看當前工程的時序情況以及資源利用情況。

三、 片上除錯

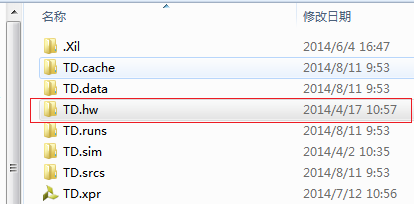

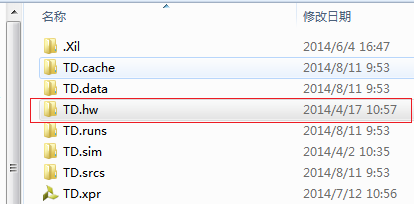

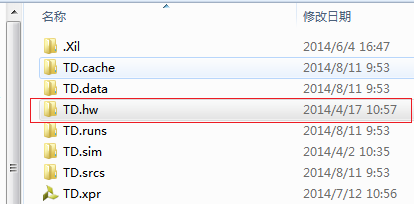

綜合實現完成之後,在工程的檔案目錄下會有xx.hw的資料夾,如上圖所示,該資料夾中有捕捉訊號的配置檔案,能夠將捕捉的訊號自動對應到HDL程式碼中的訊號變數名,這樣省去了在使用Chipscope時的一些手動配置過程,給使用者的使用帶來了方便。

如下圖,開啟Hardware Manager,新建一個新的目標裝置,此時會有一個選擇目標裝置位置的視窗,需要輸入主機IP和埠號,所以,我們可以發現Hardware Manager不僅可以管理本機所連線的FPGA裝置,也可以管理網路中其他主機所連線的FPGA裝置。

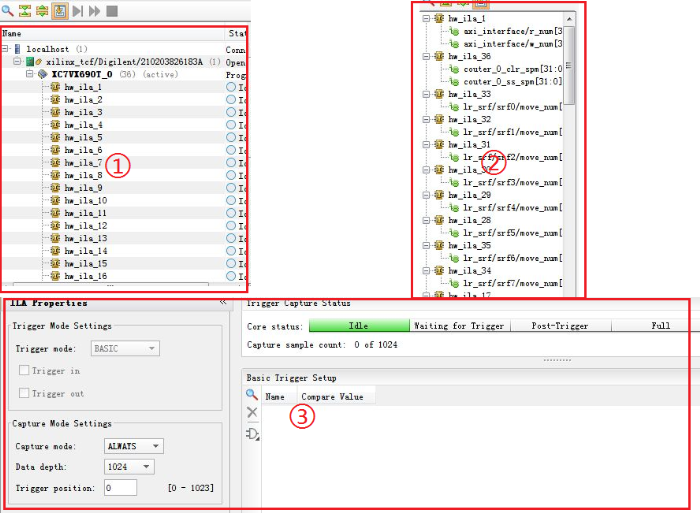

接下來是確認目標裝置和配置傳輸波特率的兩個視窗,在配置完成之後,就會彈出下圖所示的除錯視窗。其中,①是裝置及除錯邏輯的總的檢視,②是所有除錯IP的資訊,③是每個除錯IP核的狀態極其配置的視窗。

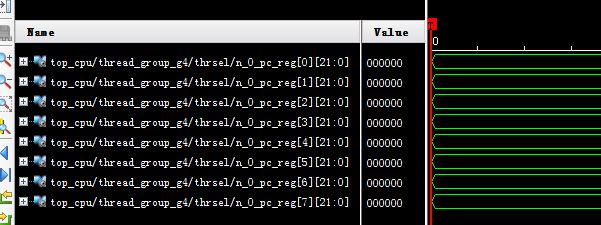

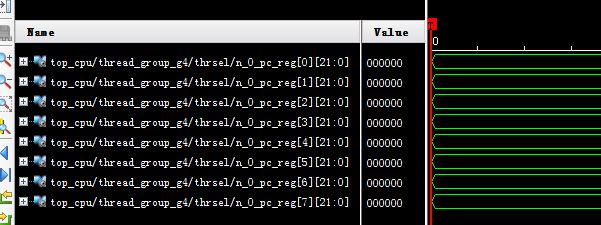

雖然在上圖②中除錯IP核的名字與程式碼中的有所不同,但是IP核捕獲的訊號名是沒有變的,如下圖所示。我們發現該除錯視窗介面同行為級模擬的介面是完全相同的,且捕獲的訊號也方便使用者分析,給使用者的除錯帶來極大的便利。

Hardware Manager是整合在VIVADO中的片上除錯工具,功能類似於ISE套件中的Chipscope,但功能更加強大,且使用更加方便。Hardware Manager不僅能夠管理本機或者遠端連線的FPGA資源,將生成的bit檔案下載,而且也可以對片上邏輯進行除錯,Hardware Manager將片上除錯的工作和檔案集中在該工程的目錄下,使得軟硬體除錯結合的更加緊密。

在實際的工程專案中,使用Hardware Manager進行片上除錯給我們的工作帶來了極大的便利,我也確實感受到Hardware Manager的強大,所以一直以來想寫一篇關於它的博文來與大家分享。但鑑於我能力有限,所以只能從比較淺的表面來介紹Hardware Manager及其使用,希望能拋磚引玉,激起大家摸索Hardware Manager的興趣。

一、 除錯IP核

同Chipscope的除錯原理一樣,Hardware Manager也是藉助於Jtag來實現的,也需要在工程中加入除錯IP核。然而,對比ISE中和VIVADO中的除錯IP核,我們會發現,VIVADO中的除錯IP使用起來更為方便。首先,使用Chipscope時需要用到ICON、ILA或VIO來配合工作,而在Hardware Manager下進行了簡化只需要用到ILA或VIO即可,ICON不需要使用者來顯式控制。

其次,如上圖是VIVADO和ISE中ILA除錯IP的對比,從引腳來看VIVADO中ILA的引腳分類更加清晰和簡潔,從配置介面上來看VIVAOD中ILA的配置也更為靈活,更便於使用者使用,而ISE中需要使用者加入較多的控制。下圖是兩者VIO除錯IP核的對比,可以發現VIVADO下的使用更為方便和靈活。VIO具有虛擬輸入輸出的功能,不僅能夠捕捉片上訊號,而且也可以往片上輸入訊號。

二、 使用方法

我們需要在工程檔案中加入除錯IP核,同Chipscope類似,Hardware Manager可以通過HDL的方法來加入除錯IP核,也可以通過網表的方法來插入除錯IP核。我個人更傾向於前者HDL加入的方法,因為這樣像使用普通IP核一樣方便,省去在網表文件中苦苦尋找網線和暫存器的工作。

這裡以HDL加入除錯IP的方法為例來簡要介紹,首先是根據需要配置好相應的除錯IP核,如捕捉訊號的數量及寬度、是否需要觸發條件等等。然後,在程式碼中的相應位置進行例項化,連線需要捕獲的訊號或者輸入的訊號,如下圖所示。最後,重新對該工程進行綜合實現。

在工程中可以加入多個不同的除錯IP核,以我個人的經驗來看,只要加入除錯IP捕捉的訊號不是太多,整個工程的時序問題不會受到影響。當然,這也要看當前工程的時序情況以及資源利用情況。

三、 片上除錯

綜合實現完成之後,在工程的檔案目錄下會有xx.hw的資料夾,如上圖所示,該資料夾中有捕捉訊號的配置檔案,能夠將捕捉的訊號自動對應到HDL程式碼中的訊號變數名,這樣省去了在使用Chipscope時的一些手動配置過程,給使用者的使用帶來了方便。

如下圖,開啟Hardware Manager,新建一個新的目標裝置,此時會有一個選擇目標裝置位置的視窗,需要輸入主機IP和埠號,所以,我們可以發現Hardware Manager不僅可以管理本機所連線的FPGA裝置,也可以管理網路中其他主機所連線的FPGA裝置。

接下來是確認目標裝置和配置傳輸波特率的兩個視窗,在配置完成之後,就會彈出下圖所示的除錯視窗。其中,①是裝置及除錯邏輯的總的檢視,②是所有除錯IP的資訊,③是每個除錯IP核的狀態極其配置的視窗。

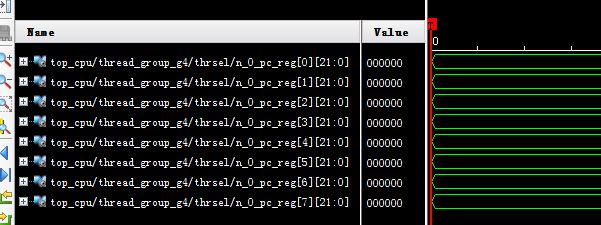

雖然在上圖②中除錯IP核的名字與程式碼中的有所不同,但是IP核捕獲的訊號名是沒有變的,如下圖所示。我們發現該除錯視窗介面同行為級模擬的介面是完全相同的,且捕獲的訊號也方便使用者分析,給使用者的除錯帶來極大的便利。

Hardware Manager是整合在VIVADO中的片上除錯工具,功能類似於ISE套件中的Chipscope,但功能更加強大,且使用更加方便。Hardware Manager不僅能夠管理本機或者遠端連線的FPGA資源,將生成的bit檔案下載,而且也可以對片上邏輯進行除錯,Hardware Manager將片上除錯的工作和檔案集中在該工程的目錄下,使得軟硬體除錯結合的更加緊密。

在實際的工程專案中,使用Hardware Manager進行片上除錯給我們的工作帶來了極大的便利,我也確實感受到Hardware Manager的強大,所以一直以來想寫一篇關於它的博文來與大家分享。但鑑於我能力有限,所以只能從比較淺的表面來介紹Hardware Manager及其使用,希望能拋磚引玉,激起大家摸索Hardware Manager的興趣。

一、 除錯IP核

同Chipscope的除錯原理一樣,Hardware Manager也是藉助於Jtag來實現的,也需要在工程中加入除錯IP核。然而,對比ISE中和VIVADO中的除錯IP核,我們會發現,VIVADO中的除錯IP使用起來更為方便。首先,使用Chipscope時需要用到ICON、ILA或VIO來配合工作,而在Hardware Manager下進行了簡化只需要用到ILA或VIO即可,ICON不需要使用者來顯式控制。

其次,如上圖是VIVADO和ISE中ILA除錯IP的對比,從引腳來看VIVADO中ILA的引腳分類更加清晰和簡潔,從配置介面上來看VIVAOD中ILA的配置也更為靈活,更便於使用者使用,而ISE中需要使用者加入較多的控制。下圖是兩者VIO除錯IP核的對比,可以發現VIVADO下的使用更為方便和靈活。VIO具有虛擬輸入輸出的功能,不僅能夠捕捉片上訊號,而且也可以往片上輸入訊號。

二、 使用方法

我們需要在工程檔案中加入除錯IP核,同Chipscope類似,Hardware Manager可以通過HDL的方法來加入除錯IP核,也可以通過網表的方法來插入除錯IP核。我個人更傾向於前者HDL加入的方法,因為這樣像使用普通IP核一樣方便,省去在網表文件中苦苦尋找網線和暫存器的工作。

這裡以HDL加入除錯IP的方法為例來簡要介紹,首先是根據需要配置好相應的除錯IP核,如捕捉訊號的數量及寬度、是否需要觸發條件等等。然後,在程式碼中的相應位置進行例項化,連線需要捕獲的訊號或者輸入的訊號,如下圖所示。最後,重新對該工程進行綜合實現。

在工程中可以加入多個不同的除錯IP核,以我個人的經驗來看,只要加入除錯IP捕捉的訊號不是太多,整個工程的時序問題不會受到影響。當然,這也要看當前工程的時序情況以及資源利用情況。

三、 片上除錯

綜合實現完成之後,在工程的檔案目錄下會有xx.hw的資料夾,如上圖所示,該資料夾中有捕捉訊號的配置檔案,能夠將捕捉的訊號自動對應到HDL程式碼中的訊號變數名,這樣省去了在使用Chipscope時的一些手動配置過程,給使用者的使用帶來了方便。

如下圖,開啟Hardware Manager,新建一個新的目標裝置,此時會有一個選擇目標裝置位置的視窗,需要輸入主機IP和埠號,所以,我們可以發現Hardware Manager不僅可以管理本機所連線的FPGA裝置,也可以管理網路中其他主機所連線的FPGA裝置。

接下來是確認目標裝置和配置傳輸波特率的兩個視窗,在配置完成之後,就會彈出下圖所示的除錯視窗。其中,①是裝置及除錯邏輯的總的檢視,②是所有除錯IP的資訊,③是每個除錯IP核的狀態極其配置的視窗。

雖然在上圖②中除錯IP核的名字與程式碼中的有所不同,但是IP核捕獲的訊號名是沒有變的,如下圖所示。我們發現該除錯視窗介面同行為級模擬的介面是完全相同的,且捕獲的訊號也方便使用者分析,給使用者的除錯帶來極大的便利。