FPGA影象處理系列——乒乓球追蹤設計例項

注:本博文將講解一個FPGA設計影象處理系統例項,此例項的功能為高速追蹤乒乓球。讀者可以參考本博文的演算法思路、工程框架,但博主並不提供工程。

當前,實用的影象處理系統都要求高速處理。目前廣泛採用軟體進行處理,但軟體處理存在速度、成本的問題。近年來,隨著現成可程式設計門陣列FPGA的發展,為提高影象處理系統的效能提供了新的思路和方法。FPGA的並行特性所帶來的高速性,以及低成本低功耗等特性,都是計算機無法比擬的。

小球追蹤平臺的FPGA以及PCB部分由本人開發。採用digilent公司Basys3 FPGA開發板作為控制核心,此款開發板採用xilinx 7系列晶片,板卡設計小巧,同時片上資源也足以滿足大多教學應用場合。此平臺擁有如下功能:

· 採集攝像頭影象,將影象顯示在VGA上

· 控制舵機-攝像頭雲臺,高速追蹤單一顏色物體(比如乒乓球)

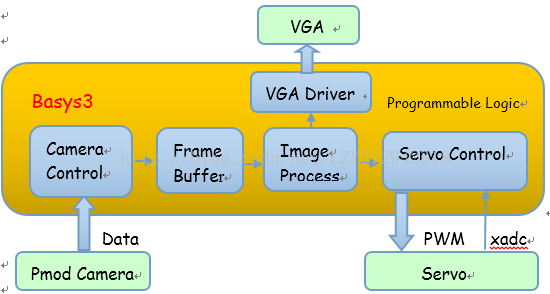

系統框架

小球追蹤平臺的系統框圖如下:

從系統框圖可知,片上主要分為5個模組,簡要介紹如下表格:

|

名稱 |

功能簡介 |

|

Camera control |

攝像頭控制,包含驅動、IIC配置 |

|

Frame buffer |

幀快取 |

|

Image process |

影象處理 |

|

Vga driver |

VGA驅動 |

|

Servo control |

舵機控制 |

IP詳解

1. 攝像頭模組

小球追蹤平臺的攝像頭採用OV系列的OV7725攝像頭。這款攝像頭時序、暫存器配置都比較簡單,效能也足以滿足追蹤的需要。

關於OV7725具體的引數和時序,使用者可以參考OV7725的官方手冊。本平臺在工程中構建了兩個關於攝像頭的IP核——一個是攝像頭時序控制模組;另一個是暫存器配置模組。

攝像頭的採集模組IP封裝如下圖所示:

引腳說明如下表格:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

pclk |

1 |

輸入 |

畫素時鐘,來自於外部攝像頭。依據此時鐘來取樣攝像頭資料 |

|

vsync |

1 |

輸入 |

幀同步訊號,來自外部攝像頭,採集完一幀會有一個vsync脈衝產生 |

|

href |

1 |

輸入 |

行資料有效訊號,來自外部攝像頭,當此訊號為高電平時,說明攝像頭有資料輸入到此模組 |

|

d |

8 |

輸入 |

攝像頭資料輸入 |

|

addr |

17 |

輸出 |

幀快取寫地址訊號 |

|

dout |

16 |

輸出 |

RGB565畫素輸出 |

|

we |

1 |

輸出 |

幀快取寫使能訊號 |

此IP的功能為:根據攝像頭的時序,對輸入的pclk、vsync、href訊號進行時序分析,將輸入的攝像頭初始資料d[7:0]轉換為使用者需要的RGB565畫素,並對應每一個RGB畫素產生一個地址、一個寫使能,以便將畫素正確存到幀快取之中。注意到,攝像頭的工作時鐘xclk並不由此模組提供。在工程中,我們直接新增一個clock模組來提供所有時鐘,其中產生一路25MHz給攝像頭,充當xclk。

OV7725內部有一些暫存器,這些暫存器的內容決定攝像頭的工作引數、工作模式等,主機可以通過IIC協議讀寫這些暫存器。本系統我們構建了一個IIC的IP。

暫存器配置IP封裝如下圖:

引腳說明如下表格:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

iCLK |

1 |

輸入 |

模組工作時鐘,25MHz |

|

rst |

1 |

輸入 |

復位(高電平復位) |

|

I2C_SCLK |

1 |

輸出 |

IIC的時鐘 |

|

I2C_SDAT |

1 |

輸出 |

IIC的資料訊號 |

|

Config_Done |

1 |

輸出 |

IIC配置結束訊號 |

此IP的功能為:產生IIC時序,並通過IIC向攝像頭暫存器寫入資料,使得攝像頭能正常工作。如果想再次配置,只需rst引腳復位一次即可。

在本系統中,我們通過IIC模組將攝像頭配置成QVGA的解析度(320*240)、RGB565的畫素格式。關於配置指令的詳細內容,使用者可以參考OV7725的官方手冊。

2. 幀快取

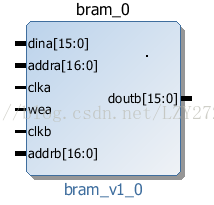

一個完整的影象採集系統一定要有幀快取。因為影象的採集端和輸出端往往並非同步,它們中間需要有一個儲存器來快取整張影象,將影象的採集、輸出部分分開,互不干擾。在硬體上,通常選用雙口ram來實現幀快取。雙口ram可以讀、可以寫,並且讀寫可以同時進行,互不影響。本系統採用的幀快取ip採用了vivado自帶的簡單雙口bram,封裝如下:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

dina |

16 |

輸入 |

寫資料訊號,為16bit的RGB565畫素 |

|

addra |

17 |

輸入 |

寫地址,影象大小為320*240,因此地址範圍為0-76799 |

|

clka |

1 |

輸入 |

寫時鐘,採用pclk |

|

wea |

1 |

輸入 |

寫使能 |

|

clkb |

1 |

輸入 |

讀時鐘,採用25MHz的時鐘,與VGA畫素時鐘同步 |

|

addrb |

17 |

輸入 |

讀地址,來自於VGA驅動模組 |

|

doutb |

16 |

輸出 |

讀資料 |

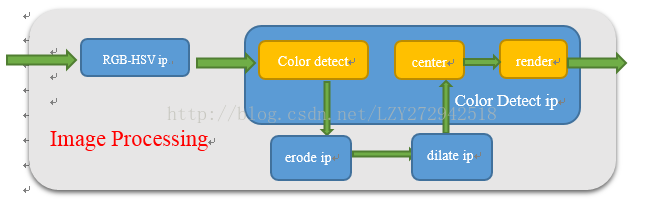

3.影象處理部分功能框圖:

· 色彩空間轉換模組RGB2HSV

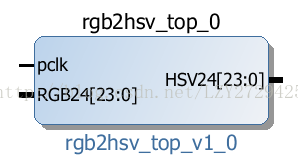

攝像頭模組得到的是RGB資料。在實際環境中,光照經常會給影象中同一物體的RGB分量帶來影響。不過,光照對於HSV(Hue、Saturation、Value)色彩空間中H、S分量的影響卻相對小很多。本平臺由於攝像頭位置隨時在變化,影象明暗程度經常會變化,為了追蹤色彩單一的乒乓球,採用HSV色彩空間是一個比較合適的策略。本系統即構建了一個RGB畫素到HSV畫素的轉換ip,IP的封裝如下:

引腳說明如下:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

pclk |

1 |

輸入 |

畫素時鐘,與VGA畫素時鐘同步 |

|

RGB24 |

24 |

輸入 |

輸入的24bit RGB畫素,R、G、B各8位 |

|

HSV24 |

24 |

輸出 |

轉換後的24bit HSV畫素,H、S、V各8位 |

IP功能說明:將輸入的RGB畫素,轉換成HSV畫素。RGB色空間和HSV空間之間的轉換為非線性的,硬體實現需要考慮時鐘同步、演算法優化、實時性等問題。此ip內部呼叫了低延遲的除法器實現Hue分量與Saturation分量的高速計算,從而實現了RGB轉換成HSV。

· 色彩提取與座標計算模組ColorDetect IP

本系統追蹤乒乓球的原理是應用了色彩方面的理論,尋找類似乒乓球色彩的區域,然後計算這個區域的中心。首先需要人為提取乒乓球的HSV分量(只提取一次);之後的每一幀都進行如下操作:遍歷影象每個畫素,對HSV分量和乒乓球相近的畫素進行標註,然後對標註後的區域去噪,去噪後,對此區域進行中心點的計算。每一幀結束都會將計算所得的中心座標傳送給舵機控制模組。

本系統提供的ColorDetect IP能實現以下功能:

·檢測顏色

·標註並上色

·計算標註區域的中心座標

在標註過程中,假如背景有橘黃色的物體,就會產生噪聲。本系統去噪、降噪的策略有兩個方面:1.形態學處理,直接去除面積較小的噪點;2.設定權值的概念,降低較大噪點影響。

對於形態學處理,在colorDetact ip內部並沒有包含,而是將待處理訊號引出到其他IP——erode ip和dilate ip。後續內容中,會介紹erode ip和dilate ip這兩個在本系統中專門用來形態學處理的IP。對於權值降噪,在ColorDetectip中,有一個權值計算模組,中心點的計算會和權值相關。對於每一個標註畫素,都計算此畫素和上一幀得到的中心點的距離,根據距離遠近設定不同大小的權值,越接近中心的標註畫素,權值越大,否則越小。這樣就會降低和乒乓球實際球體距離較遠,但面積較大的噪點的影響

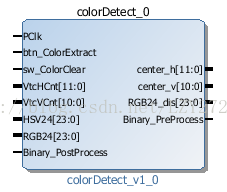

ColorDetect IP的封裝如下:

引腳說明如下表所示:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

PClk |

1 |

輸入 |

畫素時鐘,與VGA畫素時鐘同步 |

|

btn_ColorExtract |

1 |

輸入 |

顏色提取按鍵,按下一次就儲存一組參考色彩的值 |

|

sw_ColorClear |

1 |

輸入 |

顏色清除開關。為1時,清除之前儲存的參考色彩值 |

|

VtcHCnt |

12 |

輸入 |

當前畫素的列計數值,來自於VGA驅動模組 |

|

VtcVCnt |

11 |

輸入 |

當前畫素的行計數值,來自於VGA驅動模組 |

|

HSV24 |

24 |

輸入 |

輸入的HSV畫素 |

|

RGB24 |

24 |

輸入 |

輸入的RGB畫素 |

|

Binary_PostProcess |

1 |

輸入 |

輸入的去噪後的標註畫素(1bit),來自於dilate IP |

|

Binary_PreProcess |

1 |

輸出 |

輸出的去噪前的標註畫素(1bit),提供給erode IP |

|

center_h |

12 |

輸出 |

計算得到的小球區域中心點橫座標 |

|

center_v |

11 |

輸出 |

計算得到的小球區域中心點縱座標 |

|

RGB24_dis |

24 |

輸出 |

· 膨脹與腐蝕模組——erode IP & dilate IP

在影象中,利用形態學處理演算法,可以去除較小的噪點。在FPGA上實現腐蝕和膨脹兩種操作的演算法,關鍵是濾波視窗的實現。

設計的思路是:因為視窗在遍歷影象過程中,每一個畫素都會被視窗多次使用,因此需要通過快取來儲存畫素,使得它們能在後續的視窗位置被重複利用。本平臺需要的視窗大小為3*3,在FPGA中,可以設計3個單口行快取,藉助狀態機和列計數值實現這種視窗,採用流水處理的方法,實現加速計算。

得到視窗之後,就可以對其中的單元並行操作。對於腐蝕演算法,假設輸入的影象為單畫素1bit的二值化影象,只有當視窗所有元素都為1時,視窗最後輸出才為1,否則輸出為0。而對於膨脹演算法,只有當視窗所有元素都為0時,視窗最後輸出才為0,否則輸出為1。

本系統構建了erode ip和dilate ip,先通過erode ip對影象進行腐蝕,去掉小的噪點,但同時對非噪聲區域也削去了一部分邊緣;然後再經過dilate ip對影象進行膨脹,恢復被削去的非噪聲區域的邊緣。

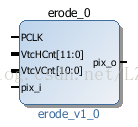

Erode IP的封裝如下:

引腳說明如下:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

PCLK |

1 |

輸入 |

畫素時鐘,與VGA畫素時鐘同步 |

|

VtcHCnt |

12 |

輸入 |

當前畫素的列計數值,來自於VGA驅動模組 |

|

VtcVCnt |

11 |

輸入 |

當前畫素的行計數值,來自於VGA驅動模組 |

|

pix_i |

1 |

輸入 |

單bit的畫素,如果是標註區域,為1,否則為0 |

|

pix_o |

1 |

輸出 |

單bit的畫素,如果是標註區域,為1,否則為0 |

dilate IP的封裝如下:

引腳說明:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

PCLK |

1 |

輸入 |

畫素時鐘,與VGA畫素時鐘同步 |

|

VtcHCnt |

12 |

輸入 |

當前畫素的列計數值,來自於VGA驅動模組 |

|

VtcVCnt |

11 |

輸入 |

當前畫素的行計數值,來自於VGA驅動模組 |

|

pix_i |

1 |

輸入 |

單bit的畫素,如果是標註區域,為1,否則為0 |

|

pix_o |

1 |

輸出 |

單bit的畫素,如果是標註區域,為1,否則為0 |

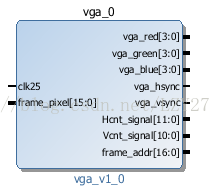

VGA IP

模組功能:產生VGA時序訊號、資料訊號,產生影象的行列計數值,以及幀快取的讀地址

IP的封裝如圖所示:

引腳說明:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

Clk25 |

1 |

輸入 |

VGA工作時鐘,25MHz |

|

frame_pixel |

16 |

輸入 |

16bit RGB畫素輸入 |

|

vga_red |

4 |

輸出 |

VGA 輸出資料(R通道) |

|

vga_green |

4 |

輸出 |

VGA 輸出資料(G通道) |

|

vga_blue |

4 |

輸出 |

VGA 輸出資料(B通道) |

|

vga_hsync |

1 |

輸出 |

VGA 行同步訊號 |

|

vga_vsync |

1 |

輸出 |

VGA 場同步訊號 |

|

Hcnt_signal |

12 |

輸出 |

當前畫素的列計數值 |

|

Vcnt_signal |

11 |

輸出 |

當前畫素的行計數值 |

|

frame_addr |

17 |

輸出 |

幀快取的讀地址訊號,由vga時序產生 |

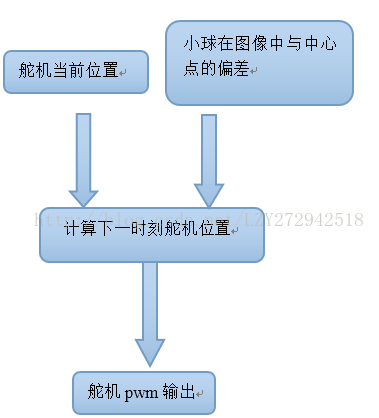

舵機控制IP

本系統為了實現追蹤,需要水平方向、豎直方向各一個舵機,以組成二自由度平臺。平臺採用的舵機是四線舵機,除了電源、地以及pwm訊號線以外,還有一根反饋訊號線,能夠以電壓的形式返回舵機當前的位置(角度)。反饋訊號使得控制演算法設計變得簡單而有效,本系統的控制演算法框圖如下:

本系統的舵機控制IP,封裝如下:

引腳說明:

|

埠名稱 |

位寬 |

方向 |

埠說明 |

|

Clk_50M |

1 |

輸入 |

工作時鐘,50MHz |

|

reset |

1 |

輸入 |

模組復位 |

|

Move_EN |

1 |

輸入 |

舵機運動使能 |

|

vsync_in |

1 |

輸入 |

幀同步輸入 |

|

x |

12 |

輸入 |

小球中心點橫座標 |

|

y |

11 |

輸入 |

小球中心點縱座標 |

|

A_VAUXP |

1 |

輸入 |

A路ADC差分輸入P端 |

|

A_VAUXN |

1 |

輸入 |

A路ADC差分輸入N端 |

|

B_VAUXP |

1 |

輸入 |

B路ADC差分輸入P端 |

|

B_VAUXN |

1 |

輸入 |

B路ADC差分輸入P端 |

|

pwm_x |

1 |

輸出 |

舵機雲臺水平方向舵機的pwm訊號 |

|

pwm_y |

1 |

輸出 |

舵機雲臺豎直方向舵機的pwm訊號 |

為了採集反饋訊號,需要一個模擬-數字轉換器件。Xilinx 7系列的晶片都集成了模數轉換器(XADC)。這是相比Xilinx前一代產品新增加的特性,可在系統設計中免去外接的ADC器件,提高了系統的整合度。XADC的框圖如下:

XADC的主要效能指標有:

l 12-bit,1M取樣率;

l 即可採集片外電壓訊號輸入,又可採集晶片溫度、晶片供電電壓

l 通過DRP(dynamic reconfigurationport)介面,可靈活配置XADC的工作模式和引數(輸入極性、取樣通道選擇、報警值等),也可檢視ADC轉換結果。

本平臺的XADC的呼叫和配置,參考了《7 Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPSAnalog-to-Digital Converter User Guide》(ug480)的p77-p85。具體讀者可查閱此文件。本系統的XADC有兩路,每一路都為差分訊號,分別用到上面ADC框圖中,外部模擬輸入的VAUXP[6]/ VAUXN[6]以及VAUXP[7] / VAUXN[7]。

舵機控制模組的工作原理為:影象每一幀都會得到一組小球中心點的橫縱座標。在幀同步訊號vsync_in的驅動下,根據ADC取樣值計算出當前的舵機角度,同時計算出當前小球中心點座標與畫面中心點座標的距離,將這兩個數值的單位統一換算成pwm,然後根據上述控制演算法框圖,計算出下一時刻舵機的pwm值。

相關推薦

FPGA影象處理系列——乒乓球追蹤設計例項

注:本博文將講解一個FPGA設計影象處理系統例項,此例項的功能為高速追蹤乒乓球。讀者可以參考本博文的演算法思路、工程框架,但博主並不提供工程。 當前,實用的影象處理系統都要求高速處理。目前廣泛採用軟體進行處理,但軟體處理存在速度、成本的問題。近年來,隨著現成可程式設計門陣列

FPGA影象處理系列——實現窗處理

窗處理是影象處理中常見的一種處理,它的思想是對於影象矩陣,通過一個固定大小(例如3*3)的小矩陣對影象進行運算操作。常用的窗處理包括Sobel邊緣檢測,形態學操作,模糊濾波,高斯濾波等。在基於PC的影象處理領域,可以方便的實現窗處理操作。比如,在opencv庫中可以自己隨意構建視窗大小,然後呼叫相關

FPGA影象處理系列-video訊號轉Avalon-ST模組

年前到手一塊Altera的SoCKit開發板,跑了跑友晶的VIP例程。也是為了練手,自己寫了個video input format detection模組(此模組官方有提供IP)。功能為:將輸入的包含RGB data, hsync,vsync,data_valid訊

FPGA影象處理之行快取(linebuffer)的設計一 FPGA影象處理之行快取(linebuffer)的設計一

轉載: FPGA影象處理之行快取(linebuffer)的設計一 FPGA影象處理之行快取(linebuffer)的設計一 作者:OpenS_Lee 1 背景知識 在FPGA數字影象處理中,行快取的使用非常頻繁,

android影象處理系列之五--給圖片新增邊框(中)

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

android影象處理系列之六--給圖片新增邊框(下)-圖片疊加

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

android影象處理系列之四--給圖片新增邊框(上)

分享一下我老師大神的人工智慧教程!零基礎,通俗易懂!http://blog.csdn.net/jiangjunshow 也歡迎大家轉載本篇文章。分享知識,造福人民,實現我們中華民族偉大復興!

FPGA影象處理入門(一)

本人有過多年用FPGA做影象處理的經驗,在此也談一下自己的看法。用FPGA做影象處理最關鍵的一點優勢就是:FPGA能進行實時流水線運算,能達到最高的實時性。因此在一些對實時性要求非常高的應用領域,做影象處理基本就只能用FPGA。例如在一些分選裝置中影象處理基本上用的都是FPGA,因為在其中相機從看到

【數字影象處理系列二】基本概念:亮度、對比度、飽和度、銳化、解析度

本系列python版本:python3.5.4 本系列opencv-python版本:opencv-python3.4.2.17 本系列使用的開發環境是jupyter notebook,是一個python的互動式開發環境,測試十分方便,並集成了vim

【數字影象處理系列四】影象資料集增強方式總結和實現

本系列python版本:python2.7.15 本系列opencv-python版本:opencv-python3.4.2.17 本系列使用的開發環境是jupyter notebook,是一個python的互動式開發環境,測試十分方便,並集成了vim操作,

android影象處理系列之七--圖片塗鴉,水印-圖片疊加

圖片塗鴉和水印其實是一個功能,實現的方式是一樣的,就是一張大圖片和一張小點圖片疊加即可。前面在android影象處理系列之六--給圖片新增邊框(下)-圖片疊加中也講到了圖片疊加,裡面實現的原理是直接操作畫素點。下面給出別外一種方式讓圖片疊加--用Canvas處理圖片,canva

Matlab影象處理系列3———空間域銳化濾波器

注:本系列來自於影象處理課程實驗,用Matlab實現最基本的影象處理演算法 1.銳化濾波器 銳化濾波,是將影象的低頻部分減弱或去除,保留影象的高頻部分,即影象的邊緣資訊。 影象的邊緣、輪廓一般位於灰度突變的地方,也就是影象的高頻部分,通常用灰度差分提取邊緣

Matlab影象處理系列1———線性變換和直方圖均衡

注:本系列來自於影象處理課程實驗,用Matlab實現最基本的影象處理演算法 影象點處理是影象處理系列的基礎,主要用於讓我們熟悉Matlab影象處理的程式設計環境。灰度線性變換和灰度拉伸是對畫素灰度值的變換操作,直方圖是對畫素灰度值的統計,直方圖均衡是對灰度值分

FPGA影象處理之路

下面論述FPGA在影象處理領域中的地位: 影象處理,它是一個非常廣義的概念,它包含影象增強,影象復原,影象重建,影象分析,模式識別,計算機視覺等N多個應用方向。這些應用技術有許多在本質上是相通的,但是不同應用領域的關注點往往是不同的。 從網路上的開源情況來看,

FPGA 影象處理的開源庫

F-I-L是一個FPGA平臺的開源的影象處理庫,已經擁有了許多常用操作,並在不斷更新中。這些操作被以IP核的形式進行了封裝,遵循同一種規範化的介面,同時具有流水線和請求響應兩種使用模式。大部分I

Matlab影象處理系列2———空間域平滑濾波器

注:本系列來自於影象處理課程實驗,用Matlab實現最基本的影象處理演算法 本文章是Matlab影象處理系列的第二篇文章,介紹了空間域影象處理最基本的概念————模版和濾波器,給出了均值濾波起和中值濾波器的Matlab實現,最後簡要討論去躁效果。 1.空

影象處理系列(1):測地線動態輪廓(geodesic active contour)

動態輪廓是影象分割的一個熱點,從早期的snake,就有很多的優化版,測地線動態輪廓(GAC)就是其中之一。總體來說,其摒棄了snake對引數的依賴,並加入了水平集,使得輪廓曲線更貼近目標物的拓撲結構。 經典的動態輪廓模型(activecontour model)的能量公式為

【數字影象處理系列三】影象增強:線性、 分段線性、 對數、 反對數、 冪律(伽馬)變換、直方圖均衡

本系列python版本:python3.5.4 本系列opencv-python版本:opencv-python3.4.2.17 本系列使用的開發環境是jupyter notebook,是一個python的互動式開發環境,測試十分方便,並集成了vim操作,安

android影象與影象處理系列(一、Bitmap和BitmapFactory)

1、Drawable物件 Android應用添加了Drawabe資源之後,Android SDK會為這份資原始檔在R清單檔案中建立一個索引項:R.drawable.file_name,接著我們可以在xml資原始檔中通過@drawable/file_name來訪問該draw

C#中基於GDI+(Graphics)影象處理系列之高質量縮圖

簡介 生成圖片縮圖的功能在Web開發的工作是經常遇到的,比如使用者上傳一張圖片作為使用者頭像,根據業務的需要生成若干不同尺寸的縮圖,不同的功能使用不同尺寸的圖片等等。 大家知道Image類有一個GetThumbnailImage的方法來生成縮圖,但是這貨表現