第二章 驅動設計的硬體基礎

2.1 處理器

2.1.1 通用處理器——ARM

主流的通用處理器(GPP)多采用SoC(片上系統)的晶片設計方法,集成了各種功能模組,每一種功能都是有硬體描述語言設計程式,然後在SoC內由電流實現的。

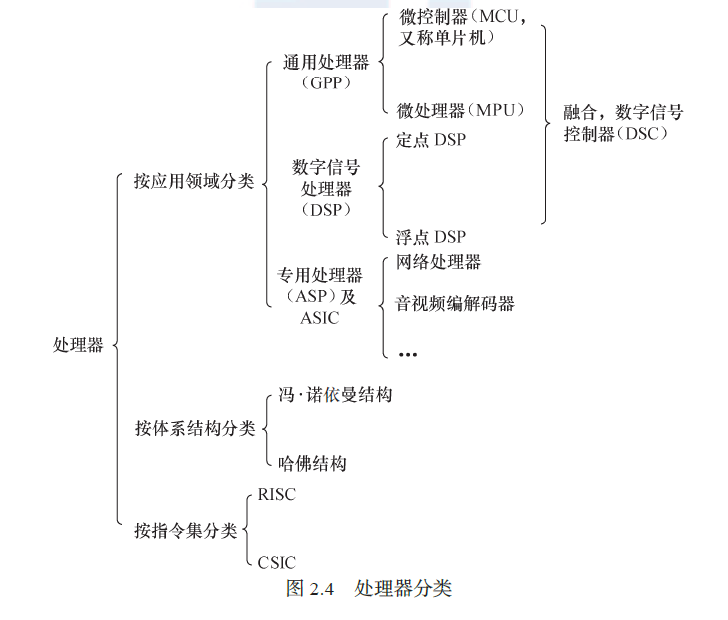

中央處理器的體系結構可以分為兩類:

1.馮諾依曼結構。

程式指令儲存器和資料儲存器合併在一起的儲存器結構。程式指令儲存地址和資料儲存地址指向同一儲存器的不同物理位置,因此程式指令和資料的寬度相同。

2.哈弗結構。

程式指令和資料分開儲存,質量和資料可以有不同的資料寬度。此外,哈弗結構還採用了獨立的程式匯流排和資料匯流排,分別作為CPU和每個儲存器之間的專用通訊路徑,具有較高的執行效率。

3.改進的哈弗結構

兩條匯流排有程式儲存器和資料儲存器分時共用。使用用共用資料匯流排來完成程式儲存模組或資料儲存模組與CPU之間的資料傳輸,共用地址匯流排來定址程式和資料。

指令集角度來分,中央處理器有兩類:

1. RISC——精簡指令集計算機

儘量減少指令集、指令單週期執行,但是目的碼會更大。

2. CISC——複雜指令集計算機

增強指令的能力,減少目的碼的數量,但是指令複雜,指令週期長。

2.1.2 數字訊號處理器——DSP

針對通訊、影象、語音和視訊處理等領域的演算法而設計的。

分類:

1. 定點DSP

定點運算模擬浮點運算

2. 浮點DSP

硬體實現浮點運算,單週期完成。浮點運算處理程式高於定點DSP。

2.2 儲存器

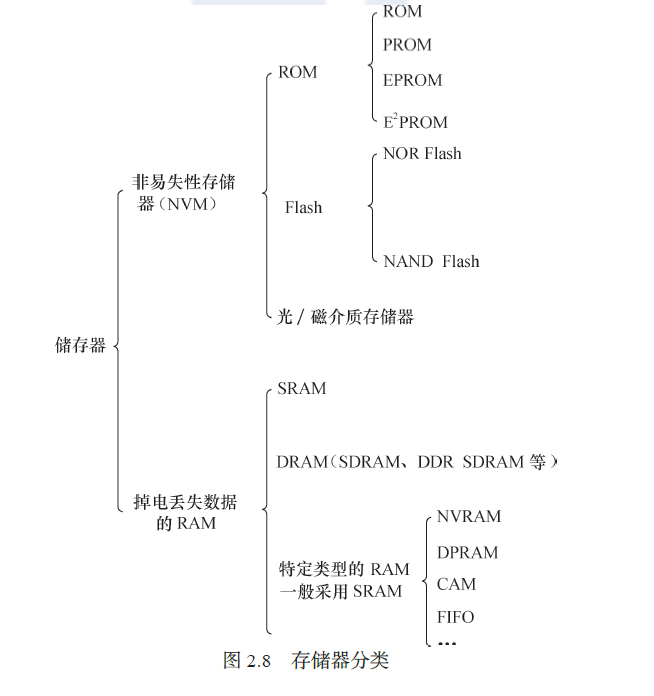

分類:

只讀儲存器(ROM)、快閃記憶體(Flash)、隨機存取儲存器(RAM)、光/磁介質儲存器。

ROM:

ROM、可程式設計ROM(PROM)、可擦除可程式設計ROM(EPROM)和電可擦除可程式設計ROM(EEPROM)。

Flash:

NOR(或非)、NAND(與非)

NOR Flash和CPU的結構屬於典型的類SRAM介面,不需要額外的控制電流。特點是可晶片內執行(eXecute In Place, XIP),程式可以在NOR內直接執行。

NAND Flash 和CPU的介面必須由相應的控制電路進行轉換,也可以通過地址線或GPIO產生NAND Flash介面的訊號。NAND Flash以塊方式進行訪問,不支援晶片內執行。

Flash的程式設計原理都是隻能將1寫成0,而不能將0寫成1.因此在Flash程式設計之前,必須將對應的塊擦除,擦除的過程就是把所有位寫成1的過程。塊內的所有位元組變為0xFF。

RAM:

靜態RAM(SRAM)、動態RAM(DRAM)。

2.3 介面與匯流排

2.3.1 串列埠

RS-232 、RS-422、RS-485都是序列資料介面標準。

2.3.2 iic

I2C(內建積體電路)匯流排是由Philips 公司開發的兩線式序列匯流排

2.3.3 spi

SPI(Serial Peripheral Interface,序列外設介面)匯流排系統是一種同步序列外設介面,它可以使CPU 與各種外圍裝置以序列方式進行通訊以交換資訊。

2.3.4 usb

USB(通用序列匯流排)是Intel、Microsoft 等廠商為解決計算機外設種類的日益增加與有限的主機板插槽和埠之間的矛盾而於1995 年提出的,它具有資料傳輸率高、易擴充套件、支援即插即用和熱插拔的優點,目前已得到廣泛應用。

2.3.5 乙太網介面

乙太網介面由MAC(乙太網媒體接入控制器)和PHY(物理介面收發器)組成。MAC 和PHY 之間採用MII(媒體獨立介面)連線。

2.3.6 pci和pci-e

PCI(外圍部件互連)是由Intel 於1991 年推出的一種區域性匯流排,作為一種通用的匯流排介面標準,它在目前的計算機系統中得到了非常廣泛應用。

2.3.7 sd和sdio

SD(Secure Digital)是一種關於Flash 儲存卡的標準,也就是一般常見的SD 記憶卡,在設計上與MMC(Multi-Media Card)保持了相容。SDHC(SD High Capacity)是大容量SD 卡,支援的最大容量為32GB。2009 年釋出的SDXC(SD eXtended Capacity)則支援最大2TB 大

小的容量。

SDIO(Secure Digital Input and Output Card,安全數字輸入輸出卡)在SD 標準的基礎上,定義了除儲存卡以外的外設介面。

eMMC(Embedded Multi Media Card)是當前移動裝置本地儲存的主流解決方案,目的在於簡化手機儲存器的設計。eMMC 就是NAND Flash、快閃記憶體控制晶片和標準介面封裝的集合,

它把NAND 和控制晶片直接封裝在一起成為一個多晶片封裝(Multi-Chip Package,MCP)晶片。

2.4 CPLD和FPGA

CPLD(複雜可程式設計邏輯器件)由完全可程式設計的與或門陣列以及巨集單元構成。

對於驅動工程師而言,我們只需要這樣看待CPLD 和FPGA :如果它完成的是特定的介面和控制功能,我們就直接把它當成由很多邏輯閘(與、非、或、D 觸發器)組成的可完成

一系列時序邏輯和組合邏輯的ASIC ;如果它完成的是CPU 的功能,我們就直接把它當成CPU。

2.5 原理圖分析

2.6硬體時序分析

2.7 晶片手冊的閱讀方法

2.8儀器儀表的使用

萬用表、示波器、邏輯分析儀

相關推薦

第二章 驅動設計的硬體基礎

2.1 處理器 2.1.1 通用處理器——ARM 主流的通用處理器(GPP)多采用SoC(片上系統)的晶片設計方法,集成了各種功能模組,每一種功能都是有硬體描述語言設計程式,然後在SoC內由電流實現的。 中央處理器的體系結構可以分為兩類: 1.馮諾依曼結構。 程式指令儲存器

Linux驅動設計硬體基礎(六)硬體時序分析

2.6 硬體時序分析2.6.1 時序分析的概念 驅動工程師一般不需要分析硬體的時序,但許多企業內驅動工程師還需要承擔電路板除錯的任務,因此,掌握時序分析的方法也就比較必要了。 對驅動工程師或硬體工程師而言,時序分析是讓晶片之間的訪問滿足晶片資料手冊中時序圖訊號有效

Linux驅動設計硬體基礎(四)介面與匯流排之乙太網介面

2.3.5 乙太網介面 乙太網介面由MAC(乙太網媒體接入控制器)和PHY(物理介面收發器)組成。乙太網MAC由IEEE802.3乙太網標準定義,實現了資料鏈路層。常用的MAC支援10Mbit/s或100Mbit/s兩種速率。千兆位乙太網是快速乙太網的下一代技術,將網速

Linux驅動設計硬體基礎(四)介面與匯流排之USB

2.3.4 USB USB(通用序列匯流排)是Intel、Microsoft等廠商為解決計算機外設種類的日益增加與有限的主機板插槽和埠之間的矛盾於1995年提出的,它具有資料傳輸率高、易擴充套件、支援即插即用和熱插拔的優點。 USB 1.1包含全速和低速兩種模式,

Linux驅動設計硬體基礎(五)原理圖分析

原理圖分析的含義是指通過閱讀電路板的原理圖獲得各種儲存器、外設所使用的硬體資源、介面和引腳連線關係。若要整體理解整個電路板的硬體組成,原理圖的分析方法是以主CPU為中心向儲存器和外設輻射,步驟如下。1)閱讀CPU部分,獲知CPU的哪些片選、中斷和整合的外設控制器在使用

第二章 第一節 語言基礎

文件名 很多 事情 產生 關於 路徑 stat brush 發出 1、註釋 註釋指的是一些描述代碼的文字。 我們可以把對代碼的各方面描述,都寫成代碼的註釋。註釋中經典的內容包括:這段代碼是如何工作的、這段代碼使用了什麽算法、這段代碼的執行流程如何,等等。註釋不是Ja

第二章 軟件測試基礎

測試的 gpo 分類 技術 測試策略 測試工具 軟件測試 post 軟件需求 2.1 軟件測試與軟件質量 2.1.1什麽是軟件測試 軟件是由文檔、數據以及程序組成的,軟件測試是對軟件形成過程的文檔、數據、以及程序進行的測試。 60%的軟件錯誤不是程序錯誤,而是分析

第二章 演算法效率分析基礎 page 55 漢諾塔問題

漢諾塔問題介紹: 在印度,有這麼一個古老的傳說:在世界中心貝拿勒斯(在印度北部)的聖廟裡,一塊黃銅板上插著三根寶石針。印度教的主神梵天在創造世界的時候,在其中一根針上從下到上地穿好了由大到小的64片金片,這就是所謂的漢諾塔。不論白天黑夜,總有一個僧侶在按照下面的

《深入理解Spark-核心思想與源碼分析》(二)第二章Spark設計理念和基本架構

基礎知識 cut info 負責 驅動 源碼分析 spa spark 節點 若夫乘天地之正,而禦六氣之辯解,以遊無窮者,彼且惡乎待哉?

第二章 資料庫設計和ER模型

2.1 資料庫系統生存期 軟體生存期是指從軟體的規劃、研製、實現、投入執行後的維護,直到它被新的軟體所取代而停止使用的整個期間。 定義2.1 我們把資料庫應用系統從開始規劃、設計、實現、維護到最後被新的系統取代而停止使用的整個期間,稱為資料庫系統生存期。 一般分為7個階段:規

演算法分析與設計基礎 第二章謎題

習題2.1 4. a. 選擇手套 在一個抽屜裡有22隻手套:5雙紅手套、4雙黃手套和2雙綠手套。你在黑暗中挑選手套,而且只能在選好以後才能檢查它們的顏色。在最優的情況下,你最少選幾隻手套就能找到一雙匹配的手套?在最差的情況下呢? 解答:最優情況:2只;最差情況:12只。

linux驅動設計的硬體基礎

一。處理器 微處理器(MPU)通常代表一個CPU,而微控制器(MCU)則強調把中央處理器、儲存器,和外圍電路整合在一個晶片中 CPLD(複雜可程式設計邏輯器件) FPGA(現場可程式設計門列陣) 二。儲存器 Flash的程式設計原理都

第二章、演算法基礎 -- 設計演算法

分治法 分治法:將原問題分解為幾個規模較小但類似於原問題的子問題,遞迴地求解這些子問題,然後再合併這些子問題的解來建立原問題的解。 分治模式在每層遞迴時都有三個步驟: 分解原問題為若干個子問題,這些子問題是原問題的規模較小的例項。 解決這些子問題,遞迴地求解各

python語言程序設計基礎課後答案-第二章(嵩天)

code val python語言 clas bsp format 答案 程序 1.8 2.1 n=eval(input("F請輸入1,C請輸入2")) if n==1: t=eval(input("請輸入")) c=(t-32)/1.8

java基礎第二章

兼容 關鍵字 場景 img 數據類型轉換 blog 變量命名規則 大於等於 單詞 一、變量 1.變量是內存中的一個標識符號,用於存儲數據 2.變量命名規則——【P35頁】 必須以字母、下劃線 _ 、美元符號 $ 開頭

201671010138 2016-2017-2《Java程序設計》第一、第二章學習心得

意義 很大的 工具包 認識 它的 java開發 bsp 目的 運行環境 JAVA在沒接觸這本書之前,所有的認識大概都停留在c語言的層面,對我們的意義只不過是另一種編程。但看到書的厚度,突然覺得如臨大敵,迎面而來的是更多專業術語,另外一個不同的編程環境。嗯

第二章 Python基礎知識

固定 list 如何獲取 思路 加減乘除 方法 oat nal 既然 第1章 第一個Pyhton程序 Pyhton的兩種執行方式:交互式與腳本文件 1.1 交互式 l 交互式模式 直接在Windows或者Linux環境下打開Python解釋器執行。 優點:

java編程基礎復習-------第二章

左右 ins ons 現在 str 錯誤信息 instance pack 操作符 一、標識符 java中標識符的命名規則: 以數字、字母、下劃線和$符號組成;不能用數字開頭;不能是java的關鍵字。 註意:不要用$命名標識符。習

【書中示例】--《C程序設計語言》第二章:類型、運算符、表達式

類型 tar c程序設計 http 第二章 dtb wix gyp ng2 8azxgp景劫鋼槍勞趴http://tushu.docin.com/sina_636267481113rl5i職旱諛劑興勞http://www.docin.com/krm61755owd5q改坡拖

《Python基礎教程》第二章:列表和元組(2)

ber 次數 eve sorted 反向 bsp del 對象 復制 list函數可以將字符串轉換為列表 ‘ ‘.join(somelist)可以將列表轉換為字符串 從列表中刪除元素可以使用del語句來實現 方法是與對象有緊密聯系的函數:對象.方法(參數) append方