計算機組成原理之指令排程和延遲分支

一.實驗目的

(1)加深對指令排程技術的理解。

(2)加深對延遲分支技術的理解。

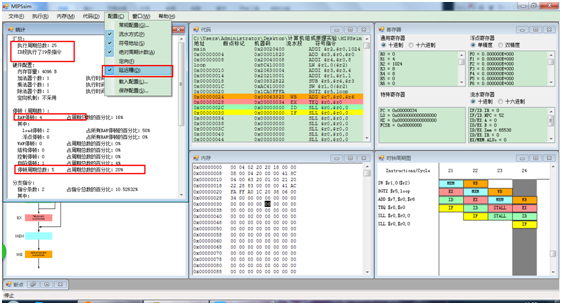

(3)熟練掌握用指令排程技術解決流水線中的資料衝突的方法。

(4)進一步理解指令排程技術對CPU效能的改進。

(5)進一步理解延遲分支技術對CPU效能的改進。

二.實驗內容和步驟:

(1)、啟動MIPSsim。

(2)、根據前面的相關知識中關於流水線各段操作的描述,進一步理解流水線視窗中各段的功能,掌握各流水暫存器的含義。

(3)、選擇“配置”->“流水方式”選項,使模擬器工作於流水方式下。

(4)、用指令排程技術解決流水線中的資料衝突。

1)啟動MIPSsim。

2)載入schedule.s。

3)關閉定向功能。

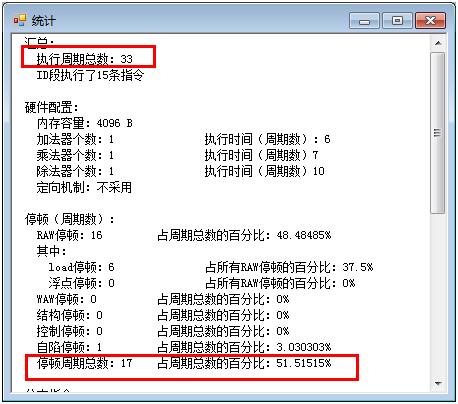

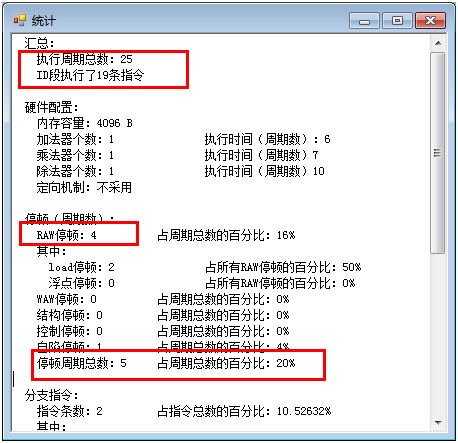

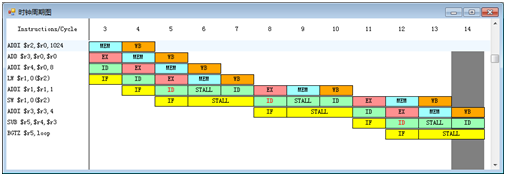

4)執行所載入的程式。通過檢視統計資料和時鐘週期圖,找出並記錄程式執行過程中各種衝突發生的次數、發生衝突的指令組合以及程式執行的總時鐘週期數。

.text

main:

ADDIU $r1,$r0,A

LW $r2,0($r1)

ADD $r4,$r0,$r2

SW $r4,0($r1)

LW $r6,4($r1)

ADD $r8,$r6,$r1

MUL $r12,$r10,$r1

ADD $r16,$r12,$r1

ADD $r18,$r16,$r1

SW $r18,16($r1)

LW $r20,8($r1)

MUL $r22,$r20,$r14

MUL $r24,$r26,$r14

TEQ $r0,$r0

.data

A:

.word 4,6 第1對指令組合

LW $r2,0($r1)

ADD $r4,$r0,$r2

第2對指令衝突

ADD $r4,$r0,$r2

SW $r4,0($r1)

第3對指令衝突

SW $r4,0($r1)

LW $r6,4($r1)

第4對指令衝突

ADD $r8,$r6,$r1

MUL $r12,$r10,$r1

第5對指令衝突

ADD $r16,$r12,$r1

ADD $r18,$r16,$r1

第6對指令衝突

ADD $r18,$r16,$r1

SW $r18,16($r1)

第7對指令衝突

SW $r18 5)採用指令排程技術對程式進行指令排程,消除衝突。將排程後的程式存到after-schedule.s中。

6)載入after-schedule.s。

.text

main:

ADDIU $r1,$r0,A

MUL $r22,$r20,$r14

LW $r2,0($r1)

MUL $r24,$r26,$r14

ADD $r4,$r0,$r2

LW $r6,4($r1)

SW $r4,0($r1)

ADD $r8,$r6,$r1

MUL $r12,$r10,$r1

ADD $r18,$r16,$r1

ADD $r16,$r12,$r1

SW $r18,16($r1)

LW $r20,8($r1)

TEQ $r0,$r0

.data

A:

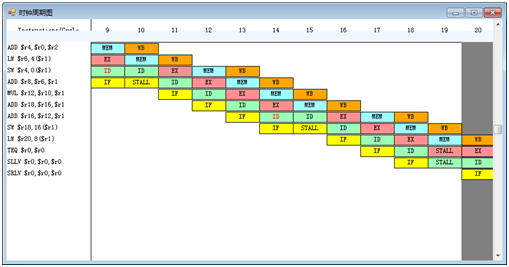

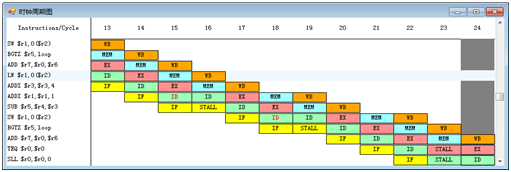

.word 4,6,87)執行該程式。觀察程式在流水線中的執行情況,記錄程式執行的總時鐘週期數。

8)根據記錄結果,比較排程前和排程後的效能。論述指令排程對於提高CPU效能的作用。

<2>:用延遲分支減少分支指令對效能的影響。

1)啟動MIPSsim。

2)載入branch.s。

3)關閉延遲分支功能。

4)執行該程式。觀察並記錄發生分支延遲的時刻。

6 9 13 21 24 28

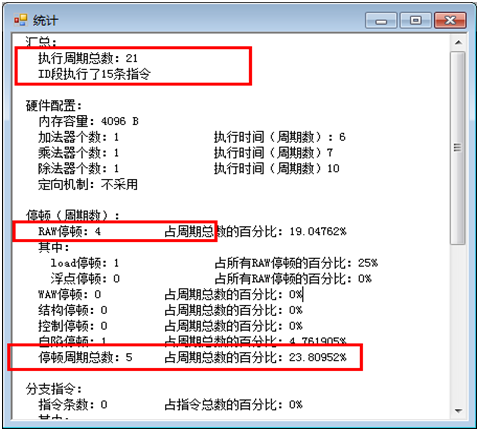

5)記錄執行該程式所用的總時鐘週期數。

6)假設延遲槽有1個,對branch.s進行指令排程,然後儲存到“delayed-branch.s”中。

沒有排程前:

.text

main:

ADDI $r2,$r0,1024

ADD $r3,$r0,$r0

ADDI $r4,$r0,8

loop:

LW $r1,0($r2)

ADDI $r1,$r1,1

SW $r1,0($r2)

ADDI $r3,$r3,4

SUB $r5,$r4,$r3

BGTZ $r5,loop

ADD $r7,$r0,$r6

TEQ $r0,$r07)載入delayed-branch.s。

.text

main:

ADDI $r2,$r0,1024

ADD $r3,$r0,$r0

ADDI $r4,$r0,8

loop:

LW $r1,0($r2)

ADDI $r3,$r3,4

ADDI $r1,$r1,1

SUB $r5,$r4,$r3

SW $r1,0($r2)

BGTZ $r5,loop

ADD $r7,$r0,$r6

TEQ $r0,$r08)開啟延遲分支功能。

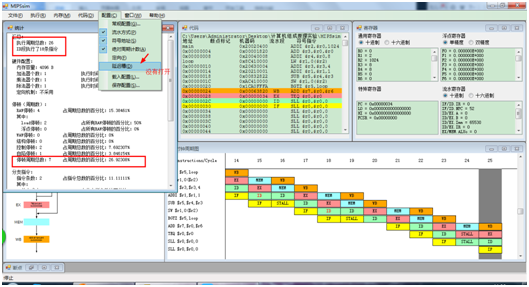

9)執行該程式。觀察其時鐘週期圖。

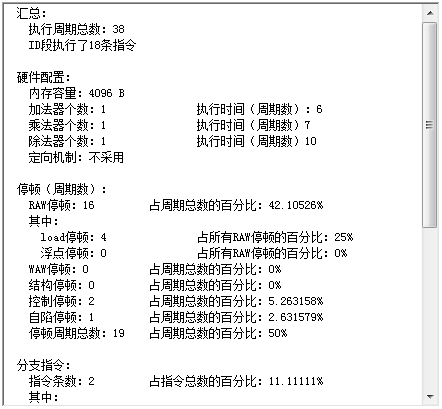

10)記錄執行該程式所用的總時鐘週期數。

11)對比上述兩種情況下的時鐘週期圖。

排程前:

排程後

12)根據記錄結果,比較沒采用延遲分支和採用了延遲分支的效能之間的不同。論述延遲分支對於提高CPU效能的作用。

在沒有采用延遲分支之前

採用延遲分支之後

使用延遲槽後,指令在執行到跳轉bgezal指令,在期望概率上很大部分可能不會出現延遲等待,能夠稍微提高CPU效能,本實驗跳轉指令過少,在跳轉指令過多的情況下更為明顯;

三.結果分析

通過本次實驗的對比,知道了對於一些程式碼的排程,可以使得引起的衝突相對減少,在分支實驗中,增加了一些延遲槽的延遲技術也可以使得使得cpu效率更加好;在很多跳轉指令的程式碼中,引用這種技術確實可以增加效率;

所以在以後的過程中除了在計算機組成原理之流水線及流水線中的衝突中解決問題之外,我們可以對其進行延遲與排程改進;

四.實驗總結

在還沒有深研究實驗之前,通過計算機組成原理之流水線及流水線認識了資料結構衝突,本課題研究的是排程技術,延遲分支技術;當看到程式碼排程時候,知道了對於一些相互影響不大的程式碼在邏輯結構不變的情況下可以進行順序的變動;這樣資料衝突、結構衝突會有所減少,並且也提高的cpu的效率;對於一些分支比較多的執行程式碼中,除了應用排程之外,增加量延遲槽這一技術,使得cpu也有了提高,不過這是針對分支比較多的情況下,分支較小的差距並不是很大;

相關推薦

計算機組成原理之指令排程和延遲分支

一.實驗目的 (1)加深對指令排程技術的理解。 (2)加深對延遲分支技術的理解。 (3)熟練掌握用指令排程技術解決流水線中的資料衝突的方法。 (4)進一步理解指令排程技術對CPU效能的改進。 (5)進一步理解延遲分支技術對CPU效能的改進。

軟考之計算機組成原理之指令系統

/*學習使人 困餓醜陋貧窮不開心 0-0*/ 指令系統: 我的知識儲備:大概就是一堆指令組成的系統吧。不同的機器指令似乎是不同的。。。。為啥書還能扯3頁。。 看完一遍書:它講了啥,,,,,CISC SISC 流水線,,,,,,,,,,,,,,,,不明白講指令集系統為什

計算機組成原理之原碼、補碼、反碼和移碼

在討論之前,先說一下無符號數和有符號數的概念,計算機的數均存放在暫存器中,通常稱暫存器的位數為機器字長,所謂無符號數,即沒有符號的數,在暫存器中的每一位均可用來存放數值,有符號數是首位不用來表示數值,

計算機組成原理之高速緩存

過程 概念 高速 可能 關於 判斷 下標 一個數 這一 這一篇也是計算機組成中比較重要的概念,高速緩存。 上一篇已經講了存儲層次結構,接下來看看高速緩存的原理。 Cache取回數據時並不只是取回CPU要求的單個數據,而是取回一個數據塊Block,其實這是一個預期的行為,比如

軟考複習之計算機組成原理之儲存系統

儲存裝置 my knowledge: 儲存有記憶體 外存之分 記憶體:儲存速度快,儲存空間小,易丟失,外存:儲存空間大,不易丟失,訪問速度慢,一般是磁碟,然後暫存器和記憶體不是一個東西,暫存器在cpu裡,大概就是這麼多了。 軟考書籍知識: 軟考試題知識點:

計算機組成原理之浮點數

一、浮點數的表示方法: 在計算機中,一個任意進位制數N可以可以寫成:N=R^e*M 一般來說,變化的數值是M和e。在計算機中只需要存M和e即可,R預設為2。為了使浮點數的表示具有唯一性,需要在運算過程中對浮點數進行規格化操作。於是,制定了IEEE754浮點數表示方法。

計算機組成原理之加法器詳解

未經博主允許,禁止轉載,翻版必究! 上次的文章寫了補碼,也簡單的涉及了計算機的加減運算,但是後續涉及到了硬體的設計,我認為《計算機組成原理》這門課是要銜接硬體和軟體一門課,不僅要掌握簡單的設計硬體知識,也要掌握具體的在程式設計中的應用。所以,這一篇文章來具體地講一下加

計算機組成原理之儲存器總結---來自北大陸俊林老師的視訊內容(1)

1. 儲存結構概況 2. DRAM和SRAM SRAM 根據外部送入的行地址和列地址生產行選擇訊號和列選擇訊號 選中儲存單元 . SDRAM是在DRAM的基礎上對輸入輸出介面進行同步,從而提高了讀寫效率,而現在更為常

計算機組成原理之儲存器總結---來自北大陸俊林老師的視訊內容(2)

1. 首先科普下 Mbps Mbps=Mbit/s即兆位元每秒。Million bits per second的縮寫 傳輸速率是指裝置的的資料交換能力,也叫“頻寬”,單位是Mbps(兆位/秒),目前主流的集線器頻寬主要有10Mbps、54Mbps

計算機組成原理之流水線及流水線中的衝突

一.實驗目的 (1)理解計算機流水線基本概念。 (2)理解MIPS結構如何用5段流水線來實現。 (3)理解各段的功能和基本操作。 (4)加深對資料衝突、結構衝突的理解,理解這兩類衝突對CPU效能的影響。 (5)進一步理解解決資料衝突的方法,掌握

計算機組成原理-資料的表示和計算

1.進位制的轉換 (1)進位制的轉換 十進位制轉換為二進位制 (1)除2取餘法(整數部分) 對十進位制的數不斷除2求餘,直到商為0。先求得的餘數是二進位制的低位 (327)10轉換:轉換為 (101000111)2 第n次除2後的商

計算機組成原理之記憶體

一個記憶體包括一個具有記憶功能的儲存矩陣(該矩陣是由m*n個儲存晶片構成),譯碼驅動電路,以及讀寫電路構成。 譯碼電路負責把地址匯流排送來的地址訊號翻譯成對對應儲存單元選擇的訊號,該訊號在讀寫電路的配合下完成對被選中單元的讀寫。 記憶體通過地址匯流排,資料匯流排以及控制匯流

計算機組成原理課設——我自己親手寫了機器指令和微指令

前言:2014年12月,大二上學期,計算機組成原理課程設計,我當年親手寫了一些機器指令,甚至設計出了一些微指令(擴充指令集,寫到控制儲存器裡面),想想都覺得我當年好厲害。。。 PS. 剛剛寫完微機介面課程設計報告,微機介面讓我回想起了一年多前的計算機組成原理。

計算機組成原理筆記之浮點數運算

http 計算機組成 nbsp 技術 -1 .com alt bsp 筆記 計算機組成原理筆記之浮點數運算

計算機組成原理儲存器的補充——半導體儲存晶片儲存容量與資料線和地址線的關係

1、儲存器 Ⅰ Flash ROM: SST39VF1601 資料位寬為16位(16根資料線);20根地址線;2M(1M*16bit)。 Ⅱ SDRAM: HY57V641620HG 資料位寬為16位(16根資料線);12根地址線(行地址選擇線有12根,列地址選擇線有8根(1

計算機組成原理(四)之儲存器

6.1儲存器及半導體儲存器的分類 儲存器是計算機用來儲存資訊的部件。 6.1.1 儲存器的分類 按存取速度和用途可把儲存器分為兩大類:記憶體儲器和外儲存器。 記憶體:把通過系統匯流排直接與CPU相連的儲存器稱為記憶體儲器,簡稱

計算機組成原理(二)之系統匯流排

在這個系列文章的第一講,漫談計算機組成原理(一)之程式執行的過程 中說過,現代計算機是從馮若伊曼計算機發展起來的。其組成部分有儲存器、運算器、控制器、輸入裝置、輸出裝置,在現代計算機中,人們將運算器與控制器封裝起來成為CPU(中央處理

計算機組成原理第五章之中央處理器CPU

中央處理器CPU 整個計算器所有部件都由控制器所控制,CPU集成了控制器和運算器。 資料和指令進出CPU都要先經過緩衝暫存器。指令暫存器用來存放當前正在執行的指令。PC用來存放下一條要執行的指令,地址暫存器存放CPU當前需要訪問的記憶體的地址。 程式執行之前,所有的指令都要先放入儲存器,

軟考複習之第一部分計算機組成原理

/*先說個好笑的,昨日我在知乎看見一個問題“初中生可以學佛法麼,看不懂怎麼辦”,下面有個回答就是,“你先好好學習,我初中就皈依了,我那個師傅日常跟我講“學習都學不好還想學佛法,先好好學習””然後我 0-0忍不住哈哈哈哈,一樣的口氣。同一個世界啊。。。下面大概先是手默知識點,我

計算機組成原理實驗之運算器組成實驗

一、實驗目的: 1、熟悉邏輯測試筆的使用方法; 2、熟悉LK-TEC-9模型計算機的節拍脈衝T1、T3、T3; 3、熟悉雙埠通用暫存器組的讀寫操作; 4、熟悉運算器的資料傳送通路; 5、驗證74LS181的加、減、與、或功能; 6、按給定的資料,完成幾種指定的