計算機組成原理之儲存器總結---來自北大陸俊林老師的視訊內容(1)

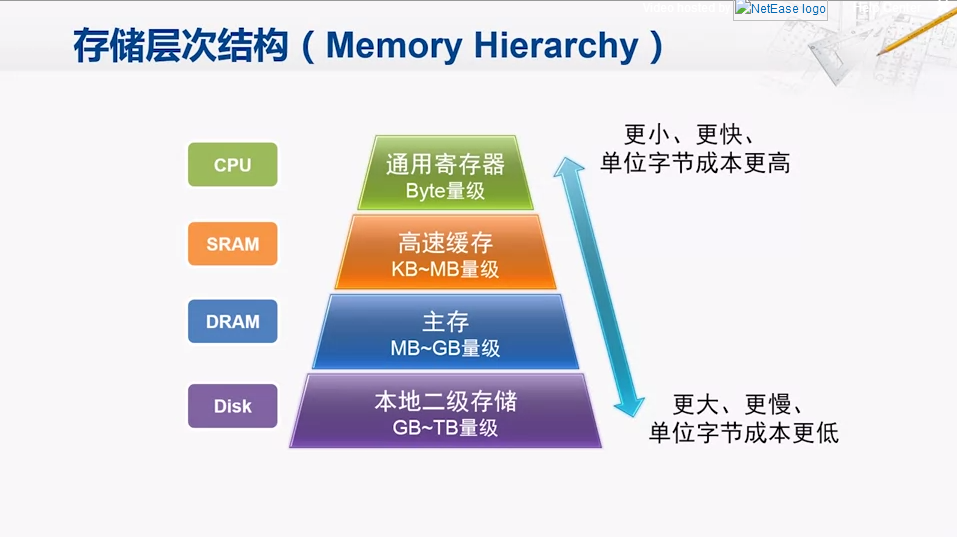

1. 儲存結構概況

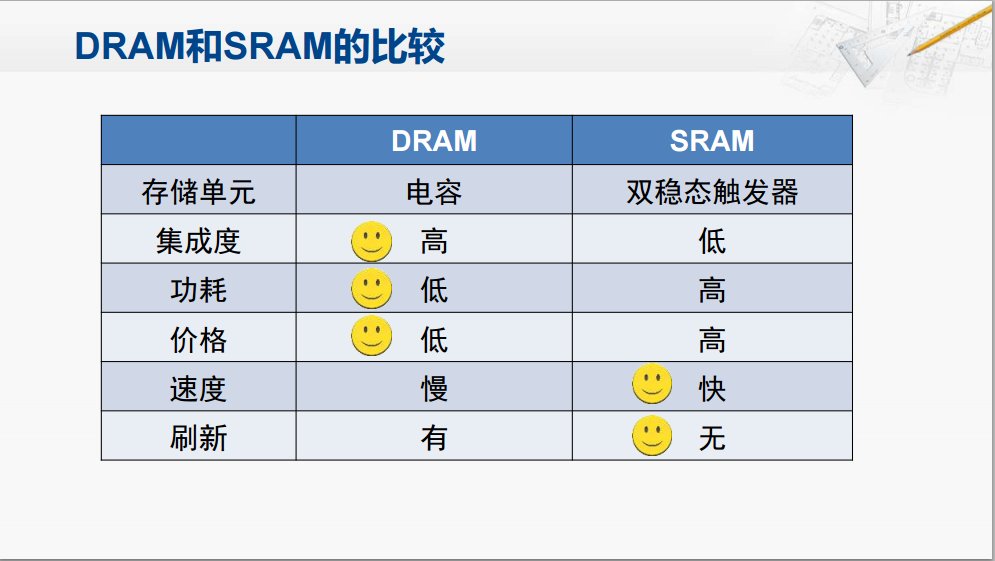

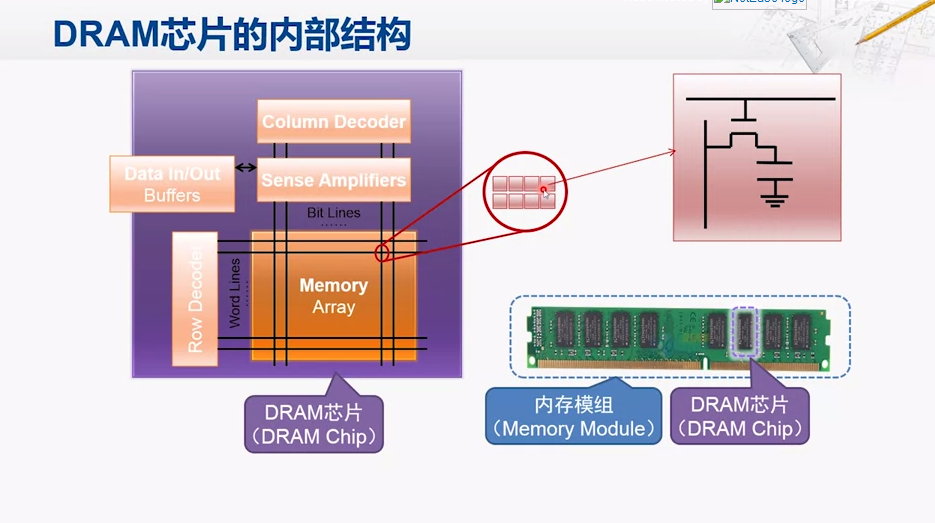

2. DRAM和SRAM

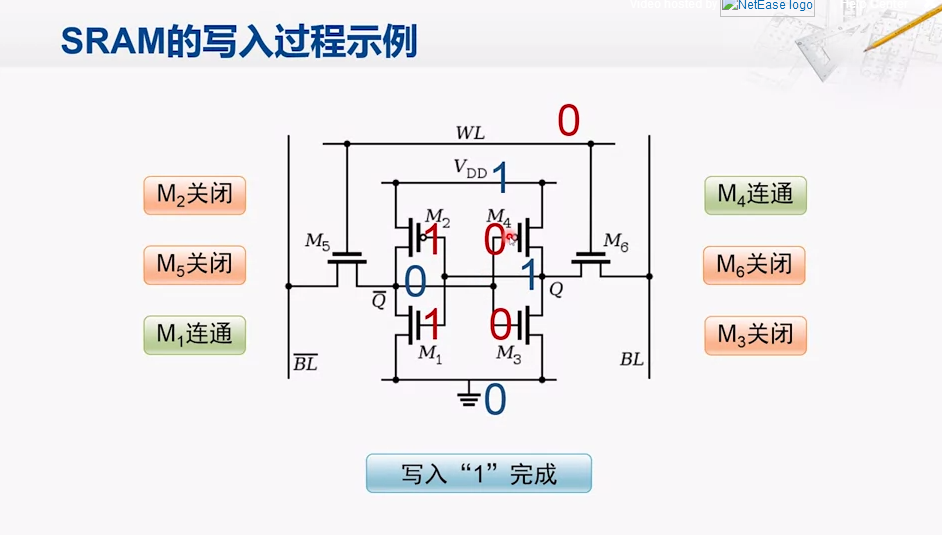

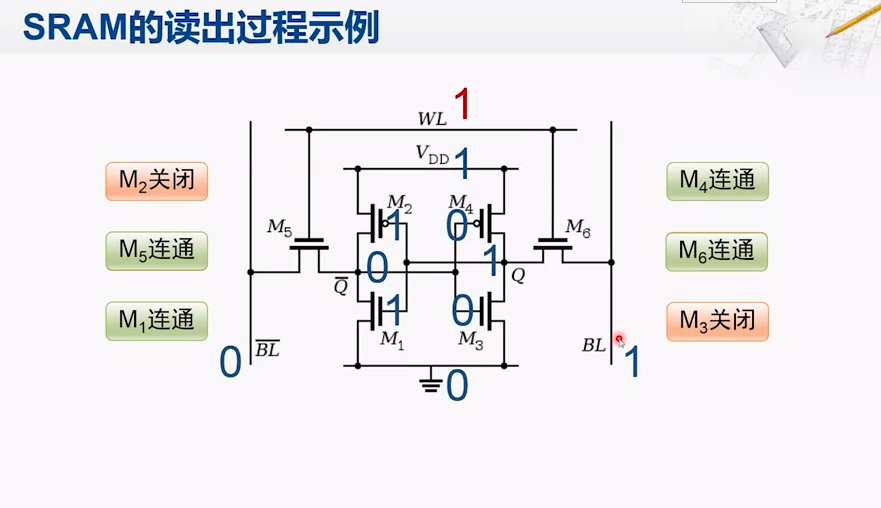

SRAM

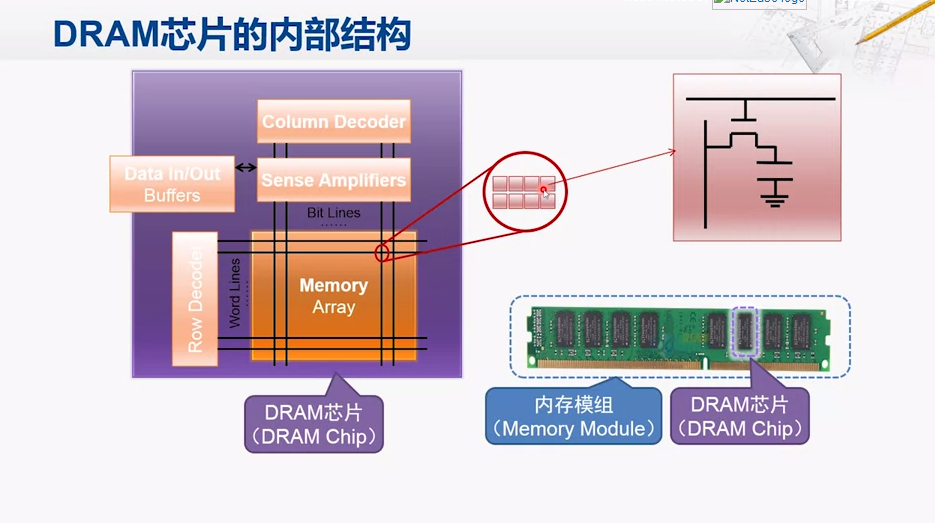

根據外部送入的行地址和列地址生產行選擇訊號和列選擇訊號 選中儲存單元 .

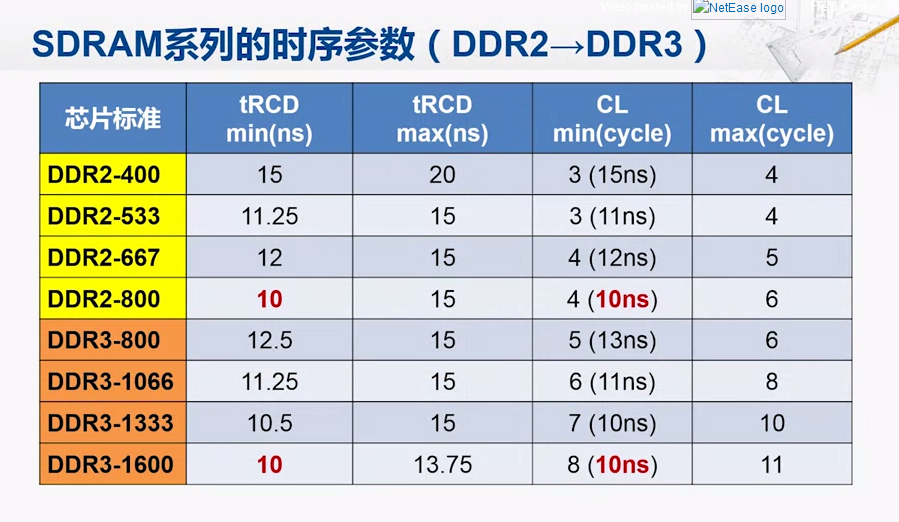

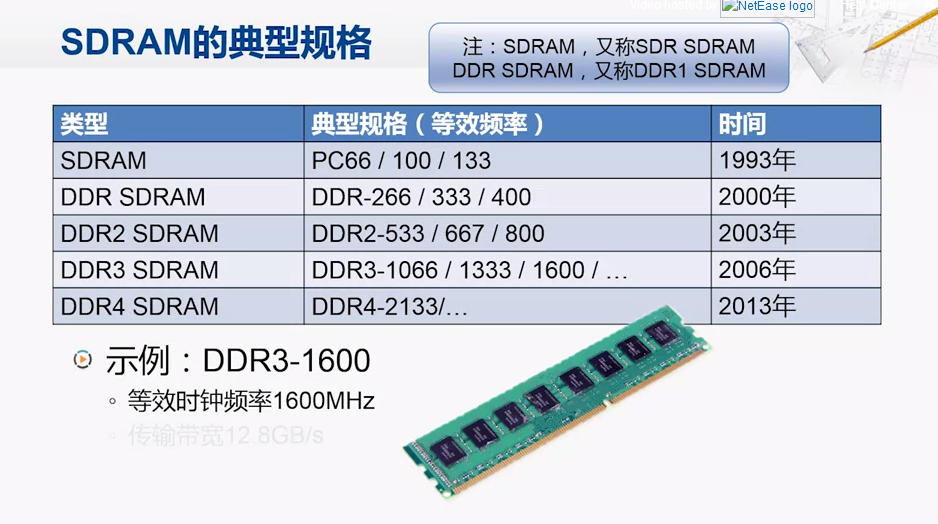

SDRAM是在DRAM的基礎上對輸入輸出介面進行同步,從而提高了讀寫效率,而現在更為常用的記憶體則是在SDRAM的基礎上又進行了進一步的改進. 如DDR1 SDRAM, DDR2 SDRAM ,DDR3 SDRAM.

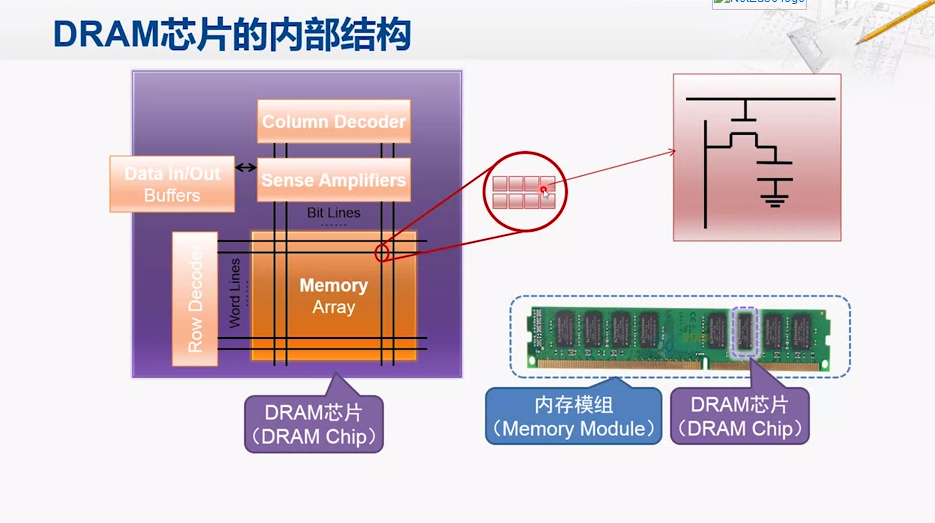

DRAM

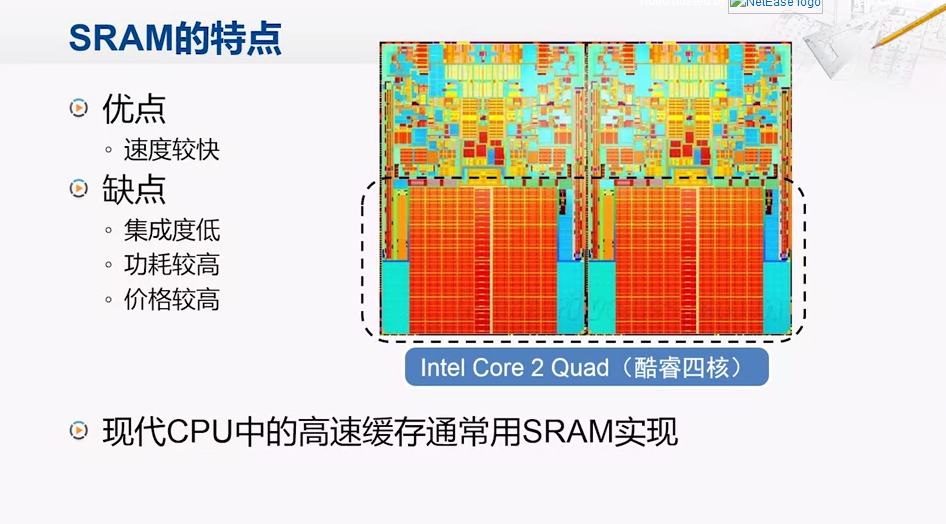

將上述的基本單元組成儲存陣列 , 有地址訊號,片選訊號 , 讀寫 訊號. SRAM 是由電晶體組成 ,自然有了它的優勢和缺點

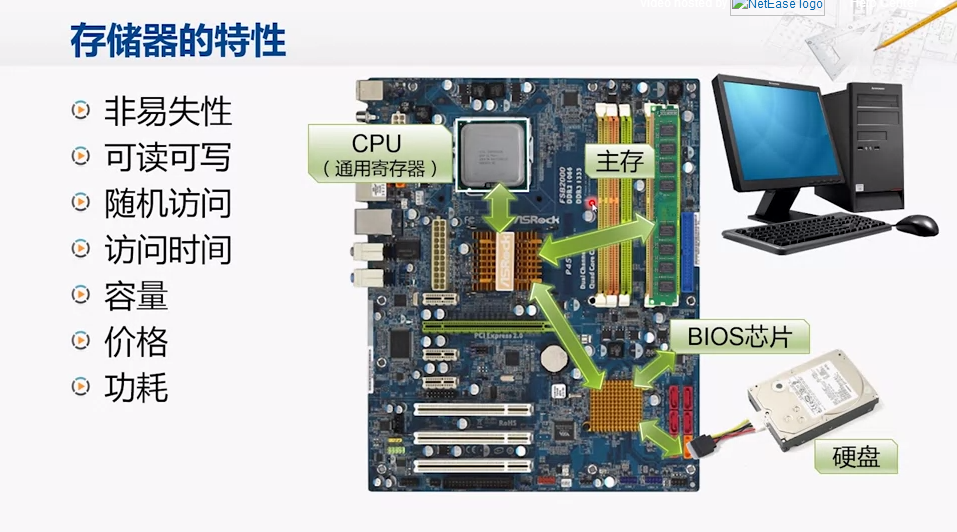

根據它們不同的特點用在不同的場合上

3. 主存的工作原理

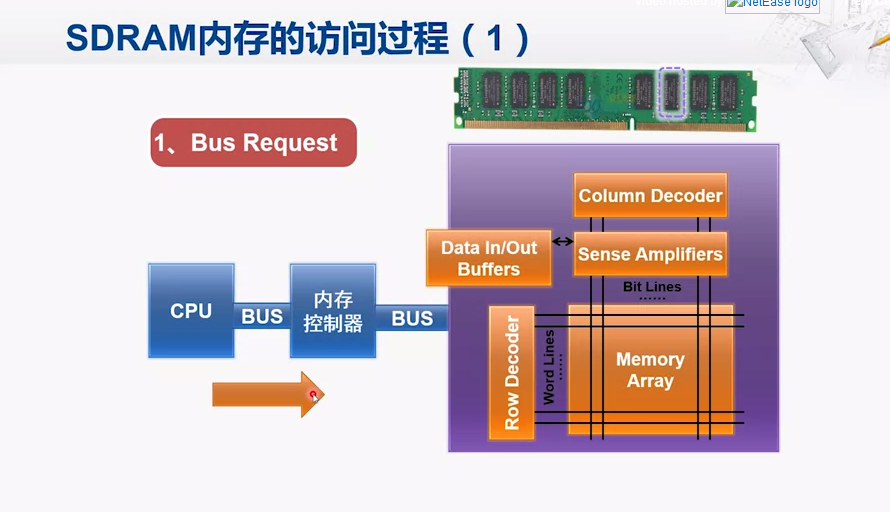

以同步的DRAM為例

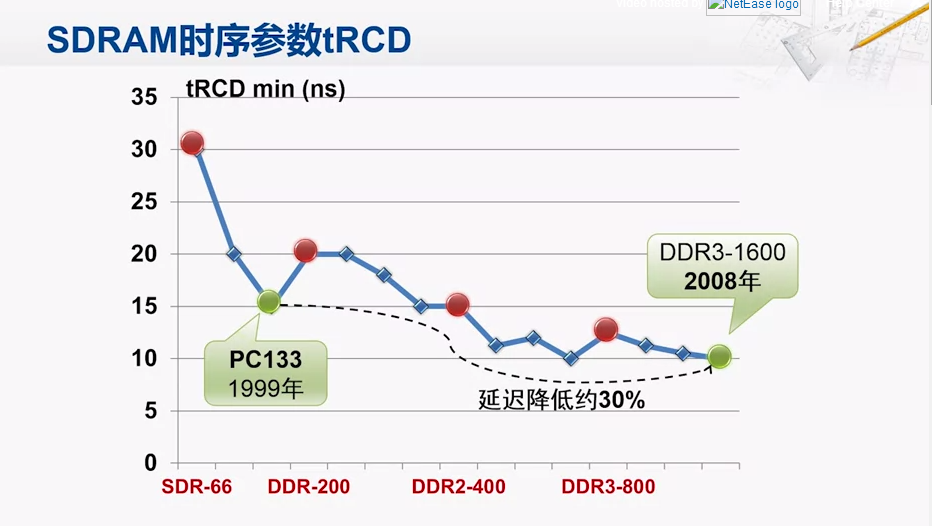

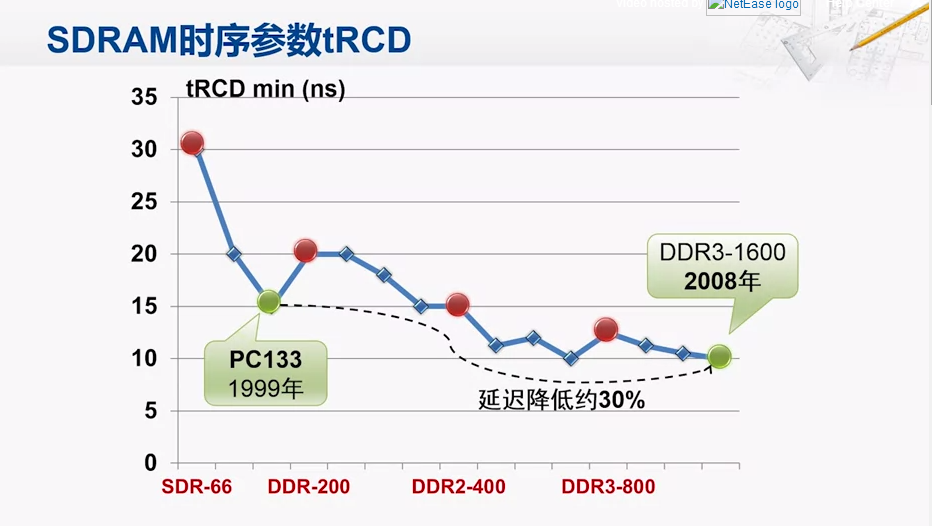

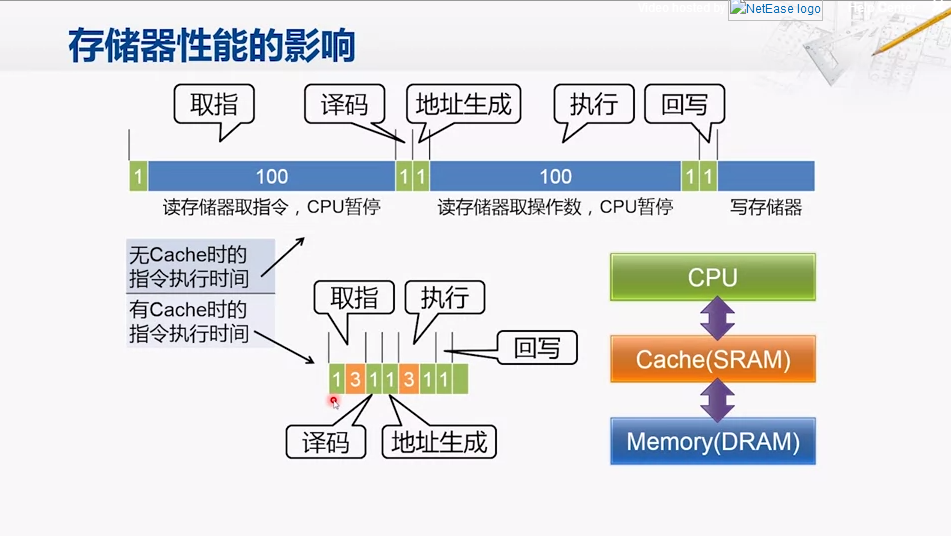

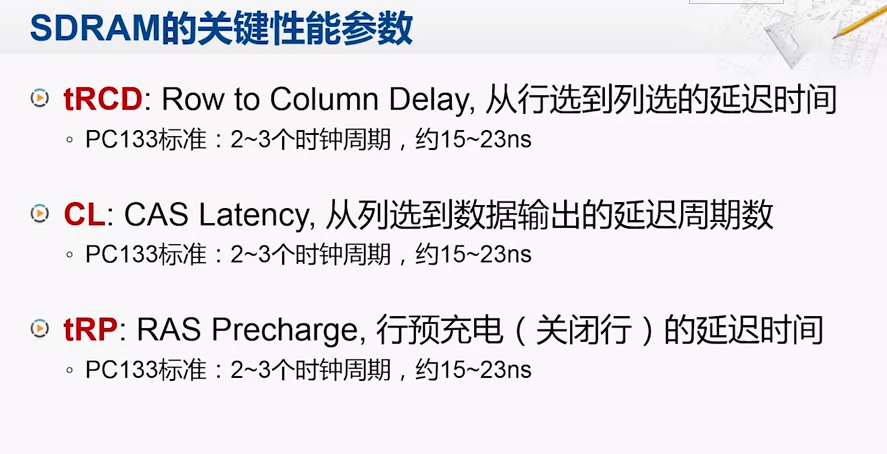

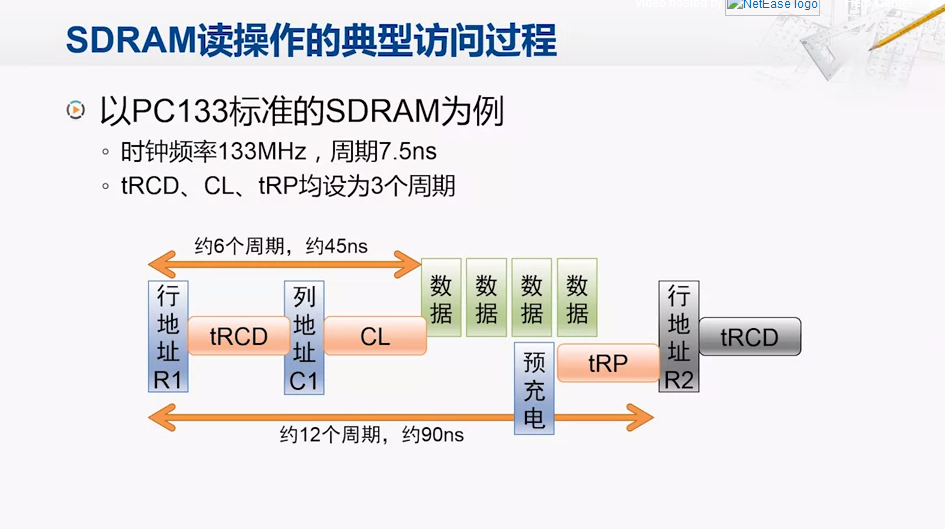

當CPU訪問儲存器時 ,先要申請系統匯流排 ,在獲得匯流排的控制權後,會將地址發到記憶體控制器中對於一個32位的CPU這個地址就是32位的 ,注意在這個時候地址不會分為行地址和列地址 , 而是隻有一個地址 , 然後記憶體控制器會將這個地址進行分解 , 形成行地址和列地址等多個部分 ,然後記憶體控制器會向DRAM晶片發起訪存操作(預充電【可能有也可能沒有】 和 行訪問 ),進行行訪問時 ,記憶體控制器通過匯流排發出的行地址會被DRAM晶片中行譯碼器接收到 , 就會在儲存陣列中選出對應的那一行 , 這一行所有的儲存單元的都會被放大之後放到緩衝區當中(此過程被稱為是啟用或者行訪問過程)。只有等這個緩衝區的訊號都穩定了 , 我們才可以進行下一步的操作。因此我們需要關注的一個時間就叫tRCD , 時間的長短是由DRAM本身的特性決定的 。等tRCD之後記憶體控制器發出列地址 , 由列地址譯碼器接收 ,之後到快取區選出對應的那一列 ,如果現在進行讀操作 , 被選中的儲存單元的數就會送到資料輸出介面上去。從發出列地址到選中儲存單元裡的數的過程 稱為列訪問過程,列訪問也需要時間,從列選到資料輸出的延遲。當DRAM送出資料之後 , 記憶體控制器就會取樣對應的資料,然後將取樣的資料送入到CPU當中 , 那過段時間CPU又會發出訪存的地址 ,如果這次訪問的資料和剛才訪問的地址在同一行,那不需要發行地址,只需要發列地址 ,從快取區中取相應的地址就行了。 當然如果不在一行 ,那麼需要把啟用的一行關閉,這一過程我們稱為預充電 ,實際上預充電可以最早在前一次傳輸 , 後一個數據即將送出的時候開始,因為我們不確定下次傳輸到底會不會在同一行 , 所以我們用兩種可以選擇的策略:1)一種方式是等到新的傳輸開始如果發現要訪問的資料不在已經被啟用的這一行 , 那時再進行預充電 。2)另一種方式是在一次傳輸之後就進行預充電, 這樣是在下一次的傳輸是在同一行概率不高的情況下,反而會獲得更好的效能 ,預充電也需要花一定的時間的,tRP

從此可以看出 ,雖然記憶體的時鐘頻率是7.5ns , 但並不意味著只需7.5ns 就可以從記憶體中得到想要的資料

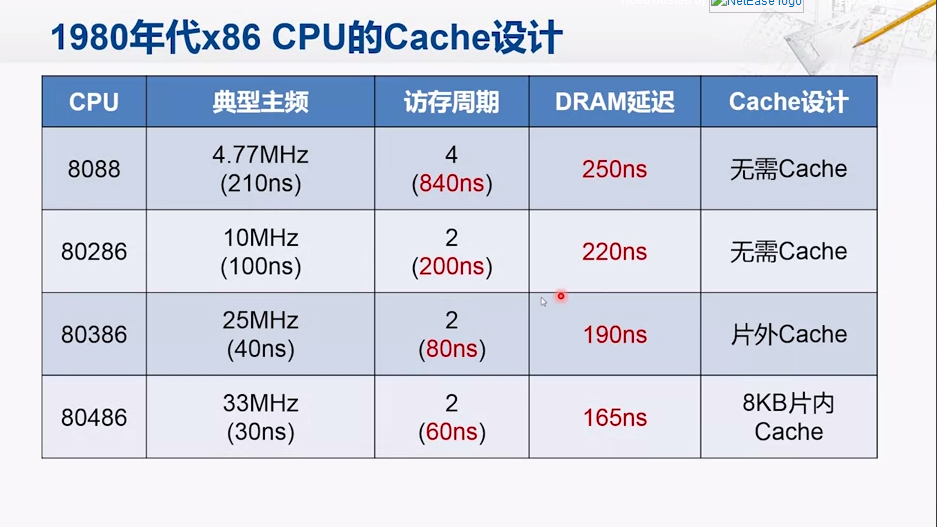

4.主存技術的發展

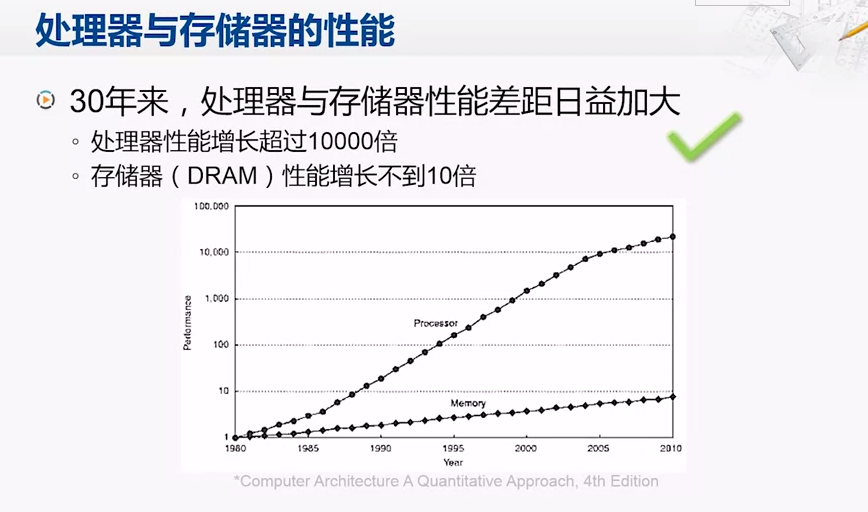

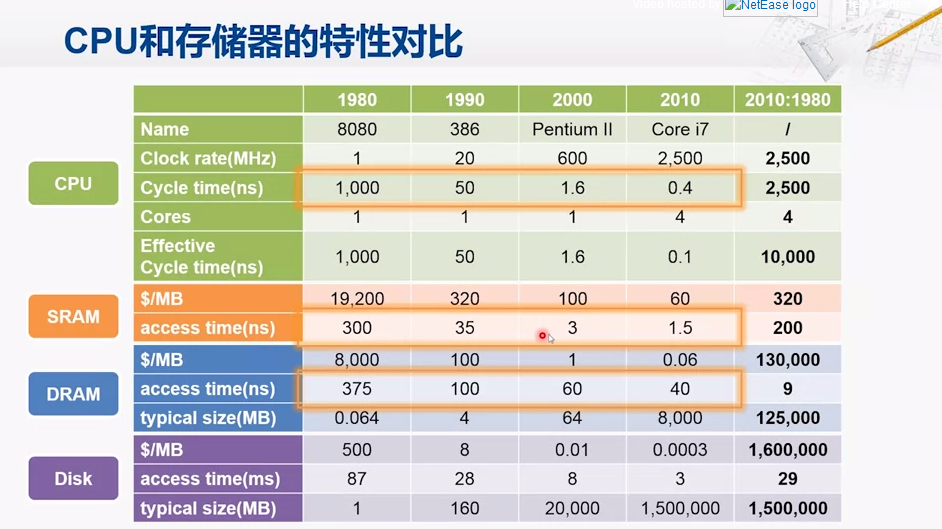

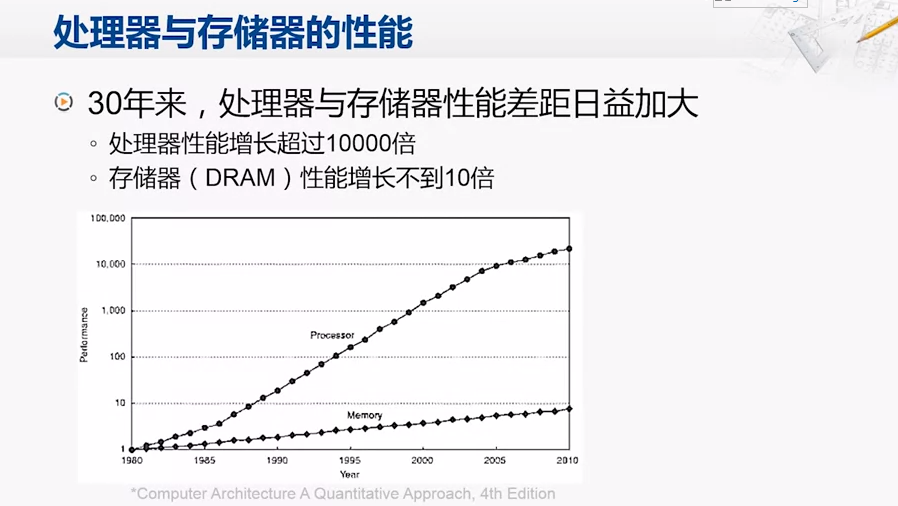

計算機的處理器和儲存器的效能差距日益加大 ,這個說法有問題嗎?

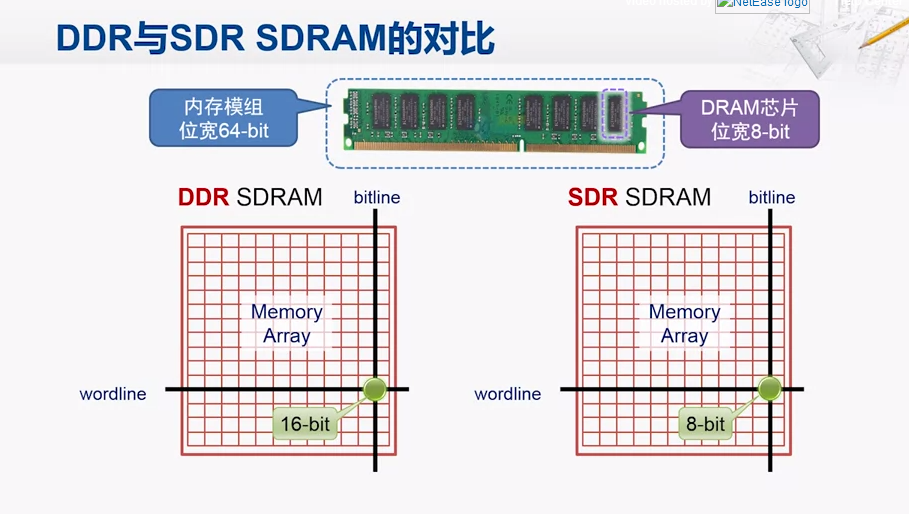

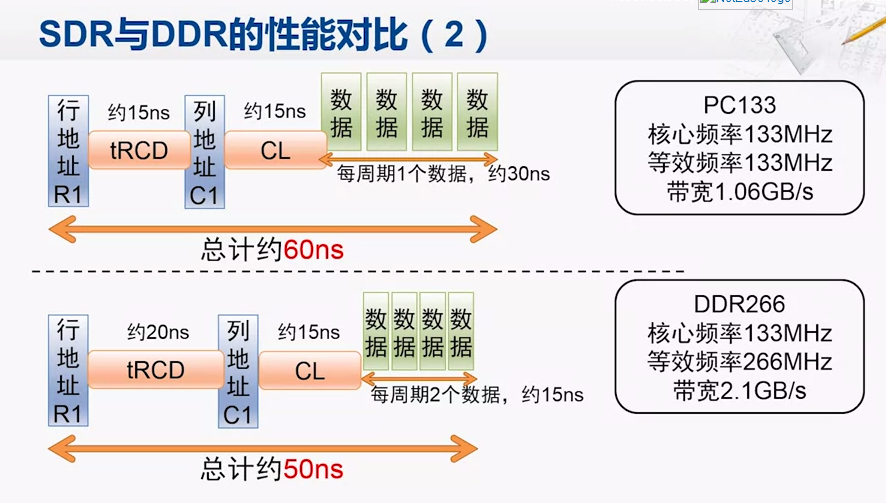

之前提到過SDRAM的結構, SDRAM的基本單元是一個電容和一個電晶體, 對SRAM的讀寫 ,最終體現了對電容的充放電上 , 而要減少充放電時間是十分困難的 ,因此當 SDR SDRAM時代,當時鍾頻率提升到133M/hz之後再很難進一步提升了,那後來的DDR SDRAM是如何提升效能的呢?

對於位寬8bit的SDR SDRAM晶片 , 每次訪問儲存陣列 ,都會取出8 bit 的資料 , 而對於相同位寬的DDR SDRAM晶片,每次訪問儲存陣列都會取出兩倍的資料量 ,這16bit的資料怎麼傳輸的呢? 這就用到雙倍資料率的概念。

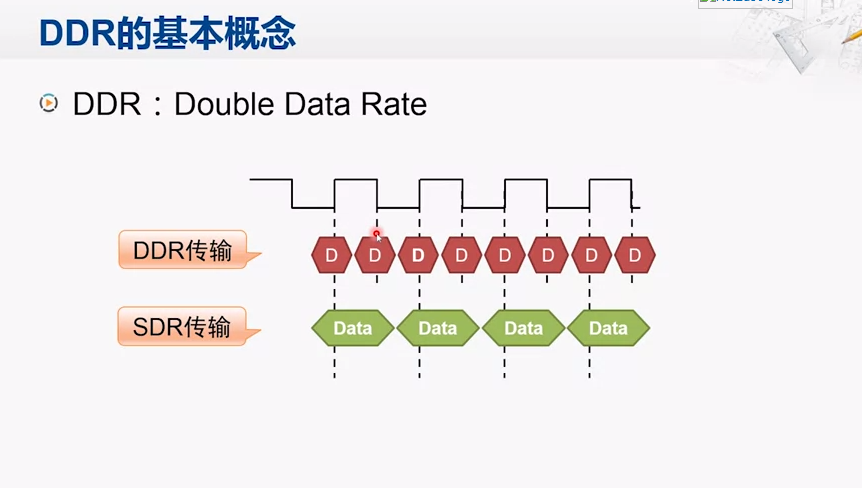

DDR在時鐘上升沿和下降沿都傳輸資料 ,同樣的時鐘頻率下傳輸雙倍的資料 ,注意,DDR是一種傳輸方式,用在SDRAM 上 就成了DDR SDRAM ,但它不僅僅用在記憶體上,還用在其他很多領域。

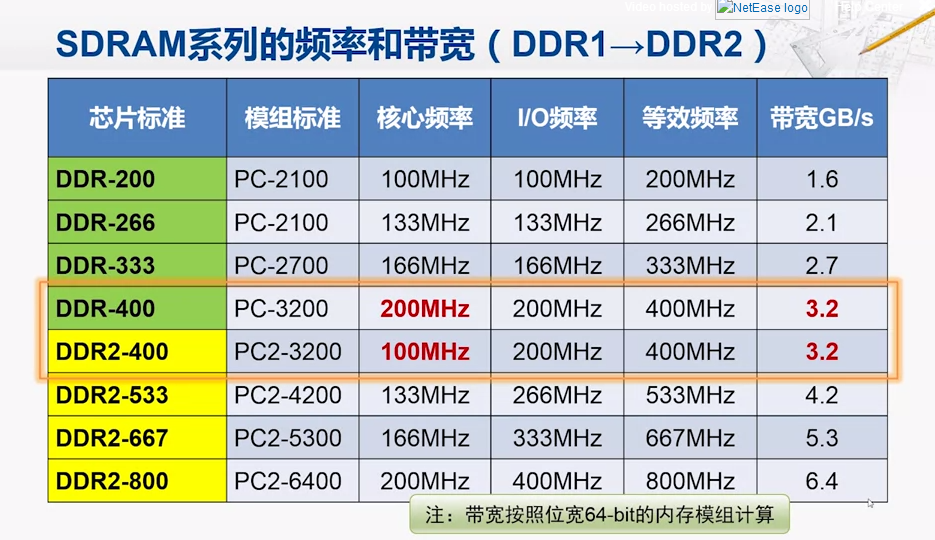

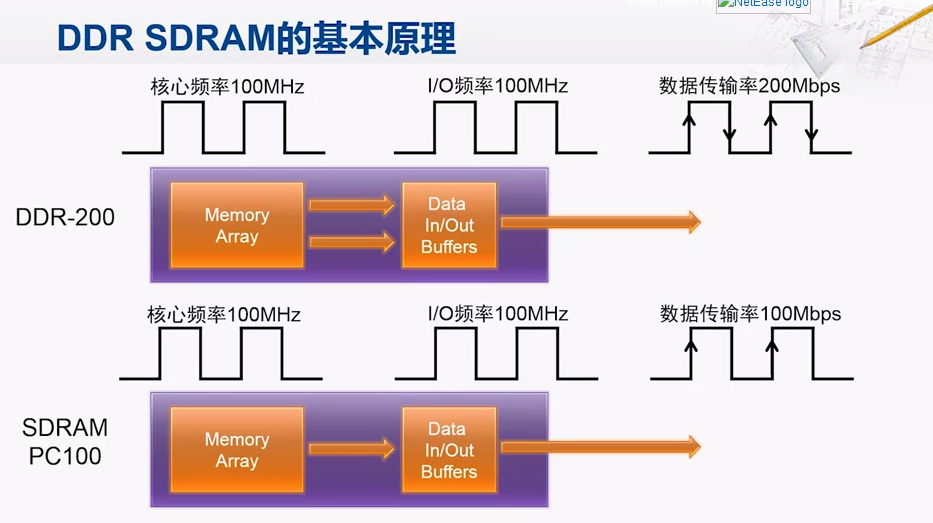

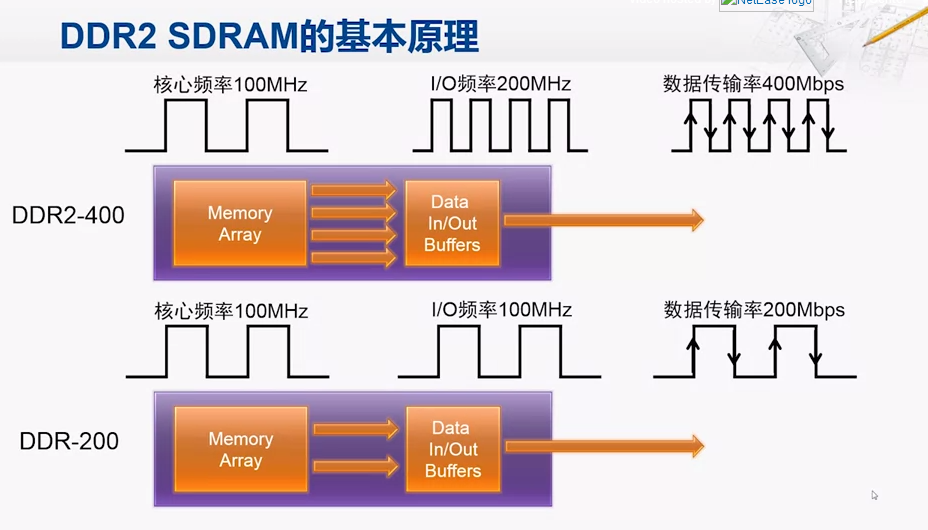

第一代DDR標準 ,即DDR-200儲存陣列核心頻率依然100M/HZ,但每個時鐘週期讀出兩個資料,而介面的時鐘頻率依然也是100M/HZ,但因為兩個時鐘沿都傳輸了資料所以仍然在一個時鐘週期內把這兩個資料都傳輸出去了,從外部看來每個時鐘上升沿和下降沿各傳輸了一個數據,單根資料線上的資料傳輸率為200Mbps,此乃DDR-200的由來.

我們由下可以明白個問題:通常理解的提升記憶體效能應該是減少資料讀寫的時間 ,而此DDR-200沒有這麼做,

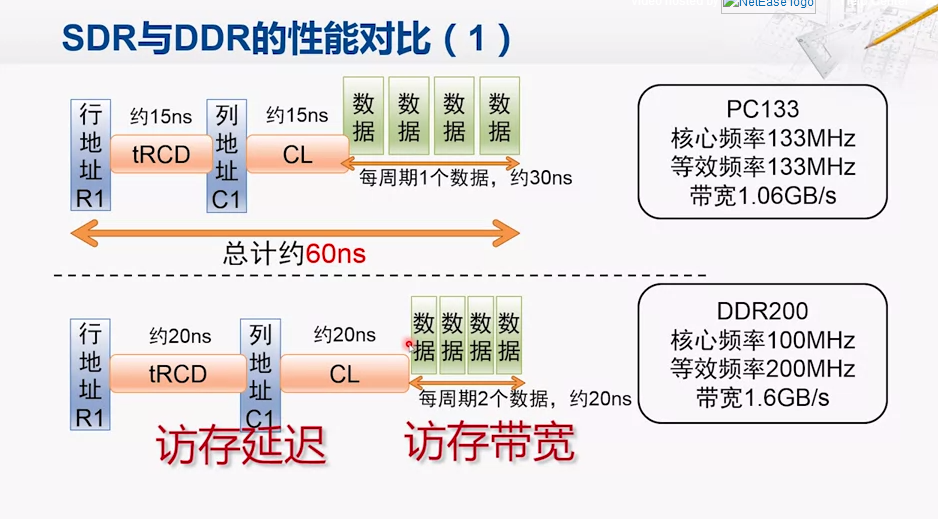

注意:評價記憶體的效能要看兩個指標:1.訪存頻寬 2.訪存延遲

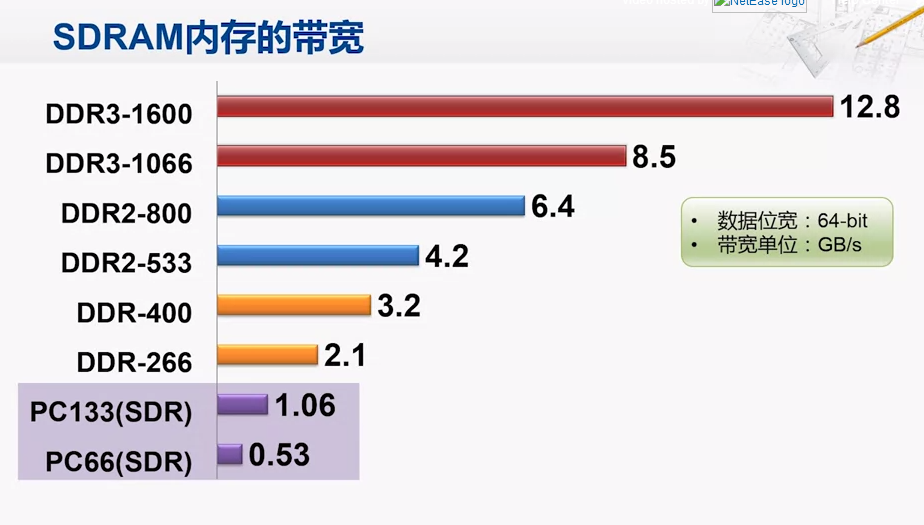

訪存頻寬是記憶體廠商大力宣傳的.有以下圖比較,可以看出DDR-200的效能是比PC133差的,DDR-400的效能明顯優於PC133了但是,到了這個時候核心頻率的提升又遇到了困難. 那麼怎麼提升核心頻率呢?

既然提升核心頻率有困難 , 那就增加預先取出資料的數量,之前從儲存陣列中取出雙倍的資料 , 現在就取出4 倍的資料 , 這樣在外界看來資料傳輸率為400Mbps , 此時單靠雙倍資料率的傳輸也不夠了 , 所以I/O介面時鐘頻率也提升了一倍,變成了200M/HZ ,這樣上下時鐘沿都傳輸資料 , 正好在一個核心時鐘的一個週期內把4個數據都傳輸出去了.

和之前的一樣DDR2 SDRAM的第一代效能也不好, DDR2-400效能不如DDR-400 , 很快就被市場淘汰了.

而從DDR2 到 DDR3 的升級基本上也是同樣的套路

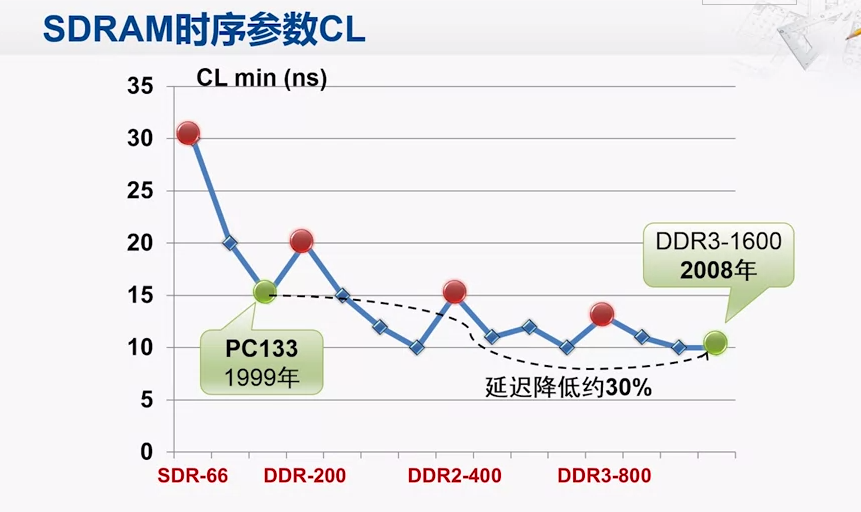

從下面三個圖可以看出 , 記憶體的發展過程 , 基本上以就是以犧牲訪存延時為代價 ,努力提高訪存頻寬 , 訪存頻寬確實有了幾十倍的提升, 但是訪存延時的優化的幅度很有限 , 這是由 SDRAM 的基本單元結構決定的 , 也就是那個電容的充放電過程 ,如果不從材料和結構上做根本的改變 , 基於現在的SDRAM結構 ,想要優化訪存延遲是很困難的 , 所以說從處理器訪存的基礎要求來看 , 讀出一個指定資料所需要的時間確實沒有多少改善,這個說法是正確的。這就是所謂記憶體越來越高的真相 , 如果我是CPU ,我想要的資料你並不能快點給我 , 但你卻給我很多我現在用不著的資料 ,這對現狀有幫助嗎?