TMS320C6678上電配置和FPGA復位DSP

- 第一種是把DSP的配置管腳全部和FPGA的IO連線,由FPGA上電控制(文末附FPGA復位DSP程式)

- 第二種是通過外部上拉/下拉電阻。

上電時序圖注意:(1) 在電源穩定期間,POR要保持低電平,所以復位前拉低。(2) DDRCLK、REFCLK應該在POR拉高前觸發。(3) 一旦獲得DVDD18供電,RESETSTAT拉低。 在DVDD18供電前,所有的LVCMOS輸入和雙向管腳不能驅動為低電平或拉高。(4) 在DVDD18有效後,RESETSTAT可以在任何時刻被拉高。在POR控制boot下,RESET必須在POR拉高前拉高。(5) 在電源穩定後,POR必須持續保持低電平至少100us。至此,電源穩定階段結束。(6) 在電源穩定階段後設備初始化需要500個REFCLK時鐘週期。最大時鐘週期是33.33nsec,所以在POR上升沿前延遲16us是必要的。在整個16us期間,時鐘必須是啟用的。(7) 在POR穩定在高電平之後,RESETFULL必須要保持低電平24個REFCLK時鐘週期。(8) 在RESETFULL上升沿,裝置鎖定GPIO 配置管腳的電平,然後進行配置,到復位狀態位RESETSTAT訊號拉高延遲大約10000到50000個時鐘週期。(9) GPIO配置必須在RESETFULL上升沿前保持至少12個REFCLK時鐘週期(transitions)。(10) GPIO配置必須在RESETFULL上升沿後保持至少12個REFCLK時鐘週期(transitions)。總的來說:

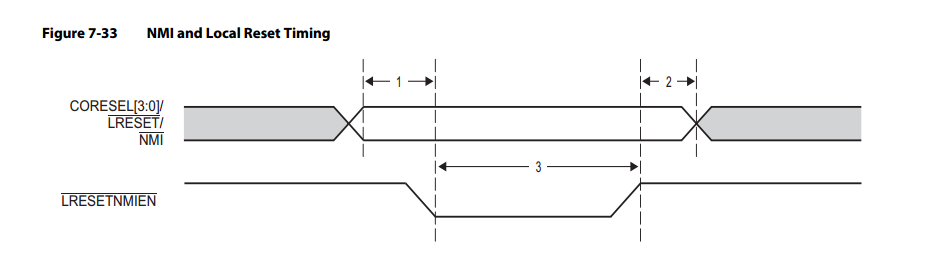

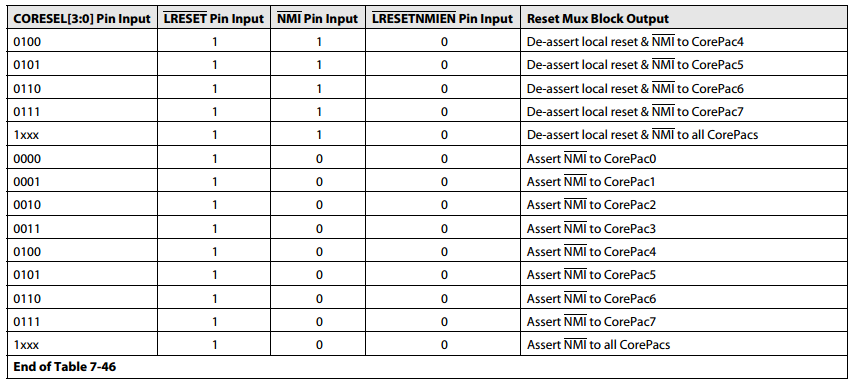

區域性復位時序圖上電覆位後,可以進行區域性復位,即對每個核單獨復位。區域性復位可以被以下方式觸發:

- LRESET pin

- Watchdog timer、CORESEL[3:0] and RSTCFG register

- LPSC MMRs(memory-mapped registers)

一般我們不使用區域性復位,如果上電覆位後,發現某些核處於復位狀態,而其他核可以連線使用,多半是區域性復位造成的,應該把LRESETNMIEN 設定為1,則可以避免這個問題。5. FPGA控制DSP上電覆位程式。module DSP_RST( input clk_25m, input RESETSTAT, //DSP復位狀態 0表示復位態 1表示工作態 input LOCKED, //時鐘模組是否正常 output ref LRESETNMIENz = 1'b0, //區域性復位管腳 output reg PORz=1'b0, //Power-on Reset output reg RESETFULL=1'b0, //Full Reset output reg RESET=1'b0 ); reg [2:0] RES_STATE=2'b00; reg [15:0] por_counter=16'b0,resetfull_counter=16'b0,reset_counter=16'b0; parameter IDLE=2'b00,PULL_RESET=2'b01,PULL_POR=2'b10,PULL_RESETFULL=2'b11;always @(posedge clk_25m) if(LOCKED==1) begin case(RES_STATE) IDLE: RES_STATE<=PULL_RESET ; PULL_RESET: if(reset_counter<25000) begin reset_counter<=reset_counter+16'b1; RES_STATE<=RES_STATE; RESET<=1'b0; PORz<=1'b0; RESETFULL<=1'b0; end else begin RESET<=1'b1; LRESETNMIENz<=1`b1; //禁止區域性復位。 RES_STATE<=PULL_POR; end PULL_POR: if(por_counter<25000) begin por_counter<=por_counter+16'b1; RES_STATE<=RES_STATE; PORz<=1'b0; end else begin PORz<=1'b1; RES_STATE<=PULL_RESETFULL; end PULL_RESETFULL:if(resetfull_counter<25000) begin resetfull_counter<=resetfull_counter+16'b1; RES_STATE<=RES_STATE; RESETFULL<=1'b0; end else begin RESETFULL<=1'b1; RES_STATE<=RES_STATE; end endcase end else begin reset_counter<=16'b0; resetfull_counter<=16'b0; por_counter<=16'b0; RES_STATE<=IDLE; RESET<=1'b0; PORz<=1'b0; RESETFULL<=1'b0; endendmodule

相關推薦

TMS320C6678上電配置和FPGA復位DSP

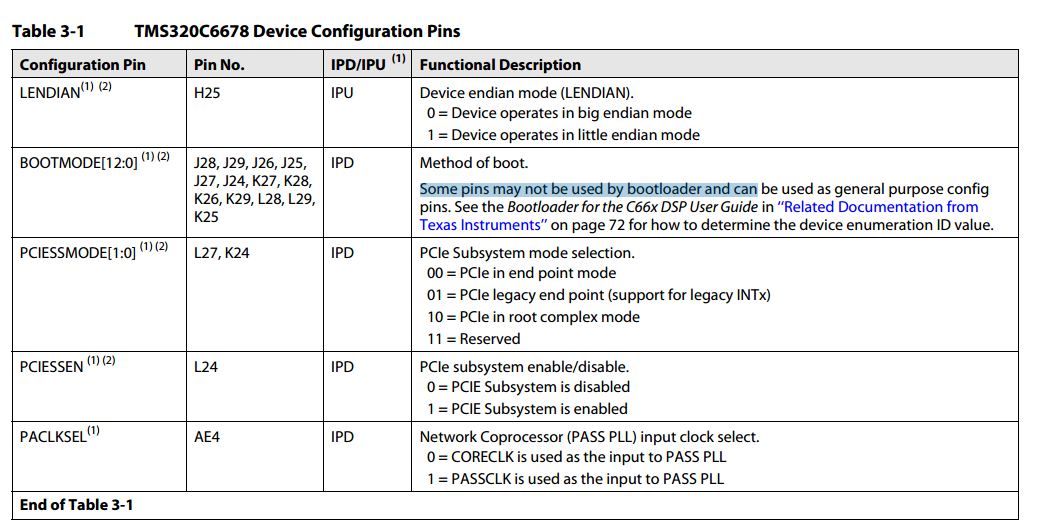

參考手冊:TMS320C6678使用者手冊。1. DSP上電覆位配置什麼? DSP的大、小端,自啟動(boot)模式,PCIe模式,網路協處理器時鐘選擇需要在上電覆位的時候選擇,怎麼選擇?依靠上電時候鎖定DSP Device Configuration pins(裝置配

Mac上安裝配置和簡單使用PostgreSQL(仍然很不懂)

ui s 暫時 psql 控制 Go 修改 文本編輯 CI 推薦 因為想要使用推薦的rails-template。需要使用postgres。並初始化了一個用戶postgres,密碼是postgres。( e.g. $ createuser -d postgres ) 需要買

AT91SAM9G45上電啟動和bootstrap移植過程

上面的圖示已經說的很清楚了,一般裸機第一次上電啟動是通過SAM-BA或者DBGU往儲存器下載正確的程式,之後可以從其它一些儲存器啟動,比如片外norflash,nandflash,dataflash等等。我手裡有塊at91sam9m10g45-ek的開發板,就是從EBI0 CS3上的nandflash啟動的,

Docker在Win 10上的配置和常用命令

前言 最近一直在用docker,所以想簡單介紹、記錄一下docker在win10系統上的配置和執行。 一、下載、安裝docker 這時右側有download for windows,點選此處。 這時候需要註冊,才能下載Docker CE for

DockerTool在Windows上的配置和執行

新開一年,邁入雲端計算的大門,所以選擇從Docker開始,好歹也得有的叢集環境吧 好了,我們開始,從官網下載Docker安裝版,原諒我懶得配Linux系統,直接window上的: 其實就是github上拿就行了,安全來說,不拿最新的哈哈 直接安裝,全安裝就行了。初學者,

nginx在windows上的配置和優化

Nginx (engine x) 是一個高效能的HTTP和反向代理伺服器,也是一個IMAP/POP3/SMTP伺服器。Nginx是由伊戈爾·賽索耶夫為俄羅斯訪問量第二的Rambler.ru 站 點(俄文:Рамблер)開發 的. 它也是一種輕量級的Web伺服

GitLab/Git在AndroidStudio上的配置和簡單使用

GitLab/Git在AndroidStudio上的使用 文 | 莫若吻 (注:以下內容純屬個人經驗,若有不當或者錯誤之處請大家指出,我會改正。非常感謝!) 1.在AndroidStu

小心FPGA的JTAG口(上電和下電順序)

同志們,根據ALTERA官方FAE(現場應用工程師)的強烈建議,請注意不要隨意帶電插拔你的JTAG下載介面,否則會損壞FPGA晶片的JTAG口訊號管腳。現象:在排除了下載線的問題後,還是不能訪問FPGA的JTAG口,那麼很有可能你的FPGA晶片的JTAG口已經損

ansible在centos7上的安裝和配置

1.Ansible簡介:ansible基於python開發,集合了眾多優秀運維工具的優點,實現了批量執行命令、部署程式、配置系統等功能。預設通過SSH協議進行遠端命令執行或下發配置,無需部署任何客戶端代理軟體,從而使得自動化環境部署變得更加簡單。可同時支援多臺主機並進行管理,使得管理主機更加便捷。主版本大概每

Linux嵌入式系統和linux純系統上電載入程式的不同

有些CPU在執行bootloader之前執行一段固化的程式,比如x86結構的CPU就是先執行BIOS中的韌體,然後才執行硬碟的第一個分割槽中的bootloader,在大多數的嵌入式系統中並沒有韌體,bootloader是上電第一個執行的程式。 Bios有上電自檢硬體是不是有問題

Window上安裝配置Zookeeper和Kafka

安裝配置Zookeeper 下載zookeeper安裝包 :http://zookeeper.apache.org/doc/r3.5.4-beta/ 解壓後可以看到: 將conf下的zoo-sample.cfg更名為zoo.cfg,因為剛下下來的bin/zkEnv.cmd裡

(一)通過JAVA連線SAP (sapjco3.jar在Windows和MacOS上的配置)

(一)通過JAVA連線SAP呼叫介面 (sapjco3.jar在Windows和MacOS上的配置) 一、sapjoc3.jar獲取 由於sap官網提供的連結需要合作公司提供賬號密碼,如果商用請索要正確的使用者名稱密碼下載,如果只是想做測試使用,可以使用我這裡提供的連結,資源失效請及時提醒我,謝謝 點選

(一)通過JAVA連接SAP (sapjco3.jar在Windows和MacOS上的配置)

失效 tin and swd pan 建立 ide msg ava (一)通過JAVA連接SAP調用接口 (sapjco3.jar在Windows和MacOS上的配置) 一、sapjoc3.jar獲取 由於sap官網提供的鏈接需要合作公司提供賬號密碼,如果商用請索要正確的用

Linux centos7上gitlab伺服器的搭建,本地配置和使用

1 gitlab的搭建 1. 安裝一堆包,和 啟動相關服務 yum install -y curl policycoreutils-python yum install -y openssh-se

idea 使用git管理專案, window配置和第一次上傳專案到碼雲

首先測試git是否安裝成功 在cmd中輸入命令 git --version 如果成功會出現版本資訊 註冊申請碼雲賬戶碼雲註冊網址,新建遠端服務專案倉儲,獲得ssh公匙複製留作備用。 首先初始化git git init檢視提交到git上的檔案,並檢視是否提交成功,成功後git s

Linux上電自動掛載SD卡和檔案系統的修改

參照黑金例程在ZYNQ開發板上移植好Linux系統後,預設是沒有載入SD卡的。因此每次斷電後,在Linux上的配置資訊全部丟失,每次上電後都要重複配置,非常的不方便,經過死皮爛臉的求問和網上查資料之後,終於實現了這個功能,在這裡分享一下我通過新建petalinux的開機自啟

智慧卡上電後返回ATR(即復位應答)時間過長而無法返ATR的解決方案

關於智慧卡片上電後返回ATR時間過長的問題,是在COS開發完成後的智慧卡相容性測試過程中發現的,不同讀卡器廠商均應遵循ISO7816接觸卡協議來設計接觸型讀卡器,理論上ATR響應時間是一樣的,不過實測之後有一定的差距。這也導致了載入開發COS的智慧IC卡在某些讀

mac上安裝git和配置使用者名稱和郵箱

1.檢查電腦上是否安裝了git。執行git 執行之後,如果如下下面的內容,則證明已經安裝了git,否則跳到第二步 2.安裝git。執行brew install git即可。 配置使用者名稱和郵箱 初次使用g

hadoop集群配置和在windows系統上運用java操作hdfs

sdn 自帶 aux mkdir del 服務 services export rop 安裝 配置 概念 hadoop常用shell命令 使用java操作hadoop 本文介紹hadoop集群配置和在windows系統上運用java操作hdfs 安裝 http:

Jekins在Tomcat上的安裝和配置

首先,apache.org的官網下載Apache Tomcat. 第二:點選/一步一步的安裝tomcat,沒有任何需要說明的難點。 我偏好選擇安裝tomcat可執行檔案,這樣可以在安裝時就自動吧tomcat註冊為windows服務。 如下圖所示。 第三:在瀏覽器位址列輸入http/